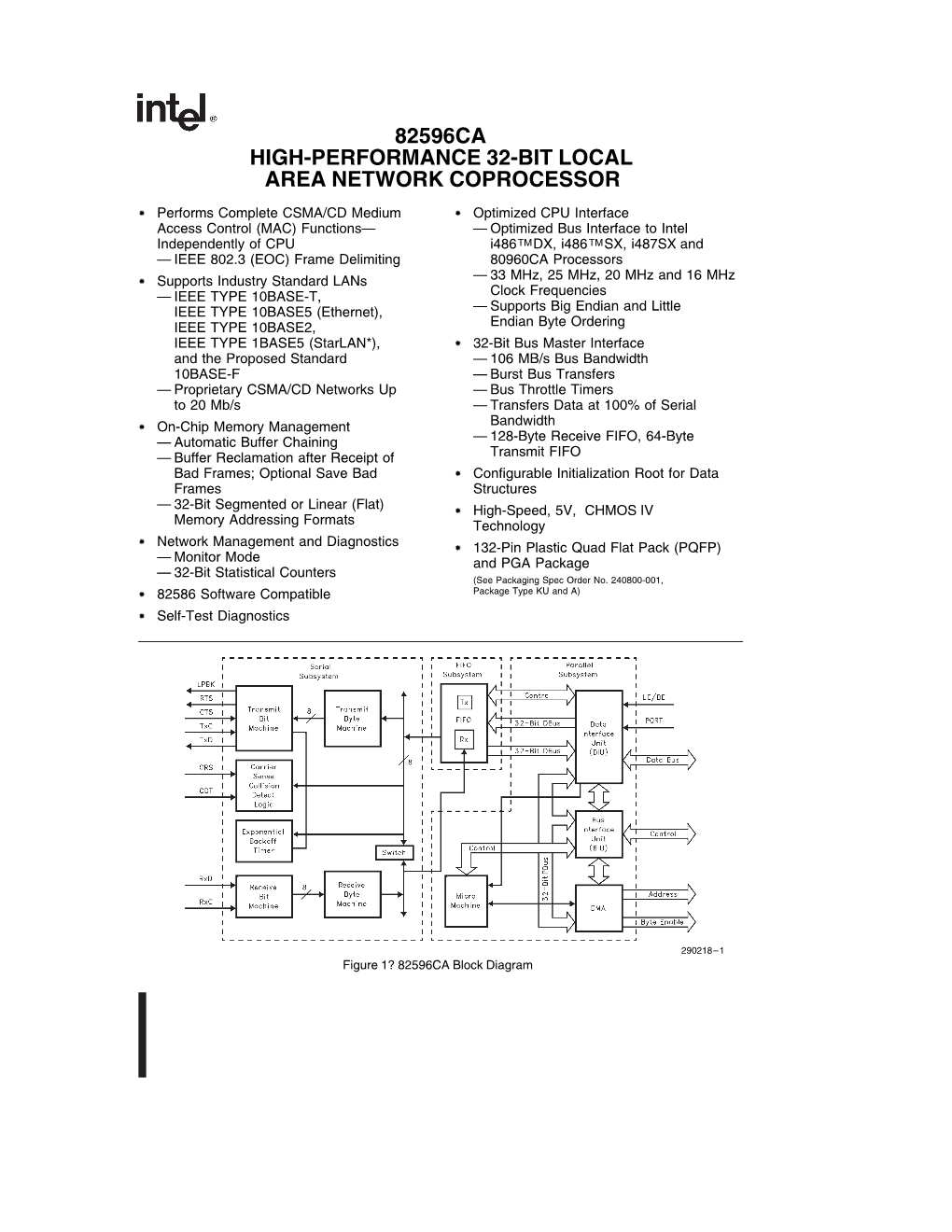

82596Ca High-Performance 32-Bit Local Area Network Coprocessor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Mikrodenetleyicili Endüstriyel Seri Protokol Çözümleyici Sisteminin Programi

YILDIZ TEKNİK ÜNİVERSİTESİ FEN BİLİMLERİ ENSTİTÜSÜ MİKRODENETLEYİCİLİ ENDÜSTRİYEL SERİ PROTOKOL ÇÖZÜMLEYİCİ SİSTEMİNİN PROGRAMI Elektronik ve Haberleşme Müh. Kemal GÜNSAY FBE Elektronik ve Haberleşme Anabilim Dalı Elektronik Programında Hazırlanan YÜKSEK LİSANS TEZİ Tez Danışmanı : Yrd. Doç. Dr. Tuncay UZUN (YTÜ) İSTANBUL, 2009 YILDIZ TEKNİK ÜNİVERSİTESİ FEN BİLİMLERİ ENSTİTÜSÜ MİKRODENETLEYİCİLİ ENDÜSTRİYEL SERİ PROTOKOL ÇÖZÜMLEYİCİ SİSTEMİNİN PROGRAMI Elektronik ve Haberleşme Müh. Kemal GÜNSAY FBE Elektronik ve Haberleşme Anabilim Dalı Elektronik Programında Hazırlanan YÜKSEK LİSANS TEZİ Tez Danışmanı : Yrd. Doç. Dr. Tuncay UZUN (YTÜ) İSTANBUL, 2009 İÇİNDEKİLER Sayfa KISALTMA LİSTESİ ................................................................................................................ v ŞEKİL LİSTESİ ...................................................................................................................... viii ÇİZELGE LİSTESİ .................................................................................................................... x ÖNSÖZ ...................................................................................................................................... xi ÖZET ........................................................................................................................................ xii ABSTRACT ............................................................................................................................ xiii 1. GİRİŞ ...................................................................................................................... -

Gigabit Ethernet - CH 3 - Ethernet, Fast Ethernet, and Gigabit Ethern

Switched, Fast, and Gigabit Ethernet - CH 3 - Ethernet, Fast Ethernet, and Gigabit Ethern.. Page 1 of 36 [Figures are not included in this sample chapter] Switched, Fast, and Gigabit Ethernet - 3 - Ethernet, Fast Ethernet, and Gigabit Ethernet Standards This chapter discusses the theory and standards of the three versions of Ethernet around today: regular 10Mbps Ethernet, 100Mbps Fast Ethernet, and 1000Mbps Gigabit Ethernet. The goal of this chapter is to educate you as a LAN manager or IT professional about essential differences between shared 10Mbps Ethernet and these newer technologies. This chapter focuses on aspects of Fast Ethernet and Gigabit Ethernet that are relevant to you and doesn’t get into too much technical detail. Read this chapter and the following two (Chapter 4, "Layer 2 Ethernet Switching," and Chapter 5, "VLANs and Layer 3 Switching") together. This chapter focuses on the different Ethernet MAC and PHY standards, as well as repeaters, also known as hubs. Chapter 4 examines Ethernet bridging, also known as Layer 2 switching. Chapter 5 discusses VLANs, some basics of routing, and Layer 3 switching. These three chapters serve as a precursor to the second half of this book, namely the hands-on implementation in Chapters 8 through 12. After you understand the key differences between yesterday’s shared Ethernet and today’s Switched, Fast, and Gigabit Ethernet, evaluating products and building a network with these products should be relatively straightforward. The chapter is split into seven sections: l "Ethernet and the OSI Reference Model" discusses the OSI Reference Model and how Ethernet relates to the physical (PHY) and Media Access Control (MAC) layers of the OSI model. -

Gigabit Ethernet

Ethernet Technologies and Gigabit Ethernet Professor John Gorgone Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 1 Topics • Origins of Ethernet • Ethernet 10 MBS • Fast Ethernet 100 MBS • Gigabit Ethernet 1000 MBS • Comparison Tables • ATM VS Gigabit Ethernet •Ethernet8SummaryCopyright 1998, John T. Gorgone, All Rights Reserved 2 Origins • Original Idea sprang from Abramson’s Aloha Network--University of Hawaii • CSMA/CD Thesis Developed by Robert Metcalfe----(1972) • Experimental Ethernet developed at Xerox Palo Alto Research Center---1973 • Xerox’s Alto Computers -- First Ethernet Ethernet8systemsCopyright 1998, John T. Gorgone, All Rights Reserved 3 DIX STANDARD • Digital, Intel, and Xerox combined to developed the DIX Ethernet Standard • 1980 -- DIX Standard presented to the IEEE • 1980 -- IEEE creates the 802 committee to create acceptable Ethernet Standard Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 4 Ethernet Grows • Open Standard allows Hardware and Software Developers to create numerous products based on Ethernet • Large number of Vendors keeps Prices low and Quality High • Compatibility Problems Rare Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 5 What is Ethernet? • A standard for LANs • The standard covers two layers of the ISO model – Physical layer – Data link layer Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 6 What is Ethernet? • Transmission speed of 10 Mbps • Originally, only baseband • In 1986, broadband was introduced • Half duplex and full duplex technology • Bus topology Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 7 Components of Ethernet • Physical Medium • Medium Access Control • Ethernet Frame Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 8 CableCable DesignationsDesignations 10 BASE T SPEED TRANSMISSION MAX TYPE LENGTH Ethernet8 Copyright 1998, John T. -

IEEE Std 802.3™-2012 New York, NY 10016-5997 (Revision of USA IEEE Std 802.3-2008)

IEEE Standard for Ethernet IEEE Computer Society Sponsored by the LAN/MAN Standards Committee IEEE 3 Park Avenue IEEE Std 802.3™-2012 New York, NY 10016-5997 (Revision of USA IEEE Std 802.3-2008) 28 December 2012 IEEE Std 802.3™-2012 (Revision of IEEE Std 802.3-2008) IEEE Standard for Ethernet Sponsor LAN/MAN Standards Committee of the IEEE Computer Society Approved 30 August 2012 IEEE-SA Standard Board Abstract: Ethernet local area network operation is specified for selected speeds of operation from 1 Mb/s to 100 Gb/s using a common media access control (MAC) specification and management information base (MIB). The Carrier Sense Multiple Access with Collision Detection (CSMA/CD) MAC protocol specifies shared medium (half duplex) operation, as well as full duplex operation. Speed specific Media Independent Interfaces (MIIs) allow use of selected Physical Layer devices (PHY) for operation over coaxial, twisted-pair or fiber optic cables. System considerations for multisegment shared access networks describe the use of Repeaters that are defined for operational speeds up to 1000 Mb/s. Local Area Network (LAN) operation is supported at all speeds. Other specified capabilities include various PHY types for access networks, PHYs suitable for metropolitan area network applications, and the provision of power over selected twisted-pair PHY types. Keywords: 10BASE; 100BASE; 1000BASE; 10GBASE; 40GBASE; 100GBASE; 10 Gigabit Ethernet; 40 Gigabit Ethernet; 100 Gigabit Ethernet; attachment unit interface; AUI; Auto Negotiation; Backplane Ethernet; data processing; DTE Power via the MDI; EPON; Ethernet; Ethernet in the First Mile; Ethernet passive optical network; Fast Ethernet; Gigabit Ethernet; GMII; information exchange; IEEE 802.3; local area network; management; medium dependent interface; media independent interface; MDI; MIB; MII; PHY; physical coding sublayer; Physical Layer; physical medium attachment; PMA; Power over Ethernet; repeater; type field; VLAN TAG; XGMII The Institute of Electrical and Electronics Engineers, Inc. -

Gigabit Ethernet Pocket Guide

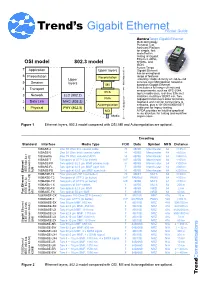

GbE.PocketG.fm Page 1 Friday, March 3, 2006 9:43 AM Carrier Class Ethernet, Metro Ethernet tester, Metro Ethernet testing, Metro Ethernet installation, Metro Ethernet maintenance, Metro Ethernet commissioning, Carrier Class Ethernet tester, Carrier Class Ethernet testing, Carrier Class Ethernet installation, Carrier Class Ethernet maintenance, Gigabit Ethernet tester, Gigabit Ethernet testing, Gigabit Ethernet installation, Gigabit Ethernet maintenance, Gigabit Ethernet commissioning, Gigabit Ethernet protocols, 1000BASE-T tester, 1000BASE-LX test, 1000BASE-SX test, 1000BASE-T testing, 1000BASE-LX testing Trend’s Gigabit EthernetPocket Guide AuroraTango Gigabit Ethernet Multi-technology Personal Test Assistant Platform for simple, fast and effective testing of Gigabit Ethernet, ADSL, OSI model 802.3 model SHDSL, and ISDN. Aurora Tango 7 Application Upper layers Gigabit Ethernet has an exceptional 6 Presentation Reconciliation range of features Upper ensuring reliable delivery of end-to-end 5 Session layers services over Metropolitan networks MII Media independent based on Gigabit Ethernet. 4 It includes a full range of tests and Transport measurements, such as RFC-2544, PCS top ten addresses, real-time Ethernet 3 Network LLC (802.2) statistics, multilayer BERT, etc. Two PMA Gigaport transceivers allow terminate, 2 Data Link MAC (803.3) loopback and monitor connections to Autonegotiation networks, plus a 10/100/1000BASE-T Physical cable port for legacy testing. 1 PHY (802.3) dependent Media MDI A PDA provides an intuitive graphical menu -

Surge Protection for Local Area Networks CONTENTS Page

Application note October 2016 MTL surge protection AN1007 Rev B Surge protection for Local Area Networks CONTENTS Page 1 Introduction and scope ................................................................................... ................................................................................................................................1 2 What is surge protection? ................................................................................... ............................................................................................................................1 2.1 How big are surges? ................................................................................. ..............................................................................................................................1 2.2 Surge protection and network layers ...................................................................... .........................................................................................................1 3 Risk factors ......................................................................................... ...................................................................................................................................................1 4 Economic factors ...................................................................................... ..........................................................................................................................................2 5 How surges -

Hybridní Ethernet (1)

Hybridní Ethernet (1) • Jedná se o kombinaci dříve uvedených typů sítě Ethernet • Tuto kombinaci lze provést pomocí: – hybridního adaptéru (BNC/řada N): mezi tenkým a silným koaxiálním kabelem – repeateru: mezi tenkým a silným koaxiálním kabelem – hubu: mezi tenkým, silným koaxiálním kabelem a kroucenou dvojlinkou 2018-06-01 1 Hybridní Ethernet (2) RJ-45 BNC + T + BNC konektor # # # max. 100 (400) m Terminátor # # AUI konektor # # Hub N + T + N konektor nebo jehlový konektor Repeater min. 0,5 m max. 185 (300) m (300) 185 max. # # # m 500 max. Drop kabel Transceiver (MAU) (max 50 m) # # # # # min. 2,5 m 2018-06-01 2 10Broad36 (1) • Jako přenosové médium používá koaxiální kabel s char. impedancí Z0 = 75 W pracující v přeloženém pásmu • Činnost v přeloženém pásmu umožňuje, aby koaxiální kabel byl využíván i pro přenos jiných informací (např. video), než jsou data přenášená v síti • Jednotlivé stanice se ke koaxiálnímu kabelu připojují pomocí transceiveru a pomocného (drop) kabelu (max. 50 m) 2018-06-01 3 10Broad36 (2) • Maximální délka jednoho kabelu je 1800 m • Všechny sítě 10Broad36 jsou zakončeny pomocí tzv. head-end zařízení, které může být na konci jednoho kabelového segmentu nebo jako kořen více kabelových segmentů • Na druhém konci je síť ukončena termináto- rem • Tímto je možné zvětšit fyzický rozsah célé sítě až 3600 m (s drop kabely 3700 m) 2018-06-01 4 10Broad36 (3) • Síť 10Broad36 může být vybudována ve dvou konfiguracích: – s jedním koaxiálním kabelem: • datové přenosy jsou rozděleny do dvou kanálů, z nichž každý využívá jiné -

802.3Cz PHY Naming

F O P Knowledge Development 802.3cz PHY naming Rubén Pérez-Aranda Bob Grow IEEE 802.3cz Task Force - Nov 2020 Plenary F O About PHY naming P Knowledge Development • Naming for 802.3cz PHYs should be considered to start writing the draft • According to [1], the PHY naming in 802.3: • Evolved where required • Avoided conflicting definition • Not had same letter in the same position meaning something different • Provided limited description of naming in standard • In [2] nGBASE-AR for 802.3cz PHYs was proposed, assuming scrambled coding 64b/66b is used as in other short wavelength multimode PHYs, e.g. 10GBASE-SR. • 802.3cz PHYs naming should be consistent with the adopted baseline • i.e. if no scrambled coding 64b/66b is used, R should be avoided in the corresponding position • The TF is facing the development of multi-gigabit optical PHYs specification for a completely new application, i.e. Automotive, which demands very different requirements compared to data-centers PHYs • Proposed PCS/PMA baseline for 802.3cz is different (see [3]) wrt. BASE-R • Baseline is close to 802.3bv (BASE-H) in the transmit frame structure and PMA • However, very different in the PCS: PAM2 vs. PAM16, RS-FEC vs. MLCC, no THP • PMD baseline will have to be consistent with automotive reliability levels, with an MDI supporting automotive mechanical and environmental requirements, as well as a much wider temperature range of operation • Definitively, we have a very distinct PHY that should use different letters to designate the PHY type name IEEE 802.3cz Task Force - Nov 2020 -

Ethernet (IEEE 802.3)

Computer Networking MAC Addresses, Ethernet & Wi-Fi Lecturers: Antonio Carzaniga Silvia Santini Assistants: Ali Fattaholmanan Theodore Jepsen USI Lugano, December 7, 2018 Changelog ▪ V1: December 7, 2018 ▪ V2: March 1, 2017 ▪ Changes to the «tentative schedule» of the lecture 2 Last time, on December 5, 2018… 3 What about today? ▪Link-layer addresses ▪Ethernet (IEEE 802.3) ▪Wi-Fi (IEEE 802.11) 4 Link-layer addresses 5 Image source: https://divansm.co/letter-to-santa-north-pole-address/letter-to-santa-north-pole-address-fresh-day-18-santa-s-letters/ Network adapters (aka: Network interfaces) ▪A network adapter is a piece of hardware that connects a computer to a network ▪Hosts often have multiple network adapters ▪ Type ipconfig /all on a command window to see your computer’s adapters 6 Image source: [Kurose 2013 Network adapters: Examples “A 1990s Ethernet network interface controller that connects to the motherboard via the now-obsolete ISA bus. This combination card features both a BNC connector (left) for use in (now obsolete) 10BASE2 networks and an 8P8C connector (right) for use in 10BASE-T networks.” https://en.wikipedia.org/wiki/Network_interface_controller TL-WN851ND - WLAN PCI card 802.11n/g/b 300Mbps - TP-Link https://tinyurl.com/yamo62z9 7 Network adapters: Addresses ▪Each adapter has an own link-layer address ▪ Usually burned into ROM ▪Hosts with multiple adapters have thus multiple link- layer addresses ▪A link-layer address is often referred to also as physical address, LAN address or, more commonly, MAC address 8 Format of a MAC address ▪There exist different MAC address formats, the one we consider here is the EUI-48, used in Ethernet and Wi-Fi ▪6 bytes, thus 248 possible addresses ▪ i.e., 281’474’976’710’656 ▪ i.e., 281* 1012 (trillions) Image source: By Inductiveload, modified/corrected by Kju - SVG drawing based on PNG uploaded by User:Vtraveller. -

Ethernet Reference Guide Your Everyday Ethernet Testing Reference Tool Cover Ethernet.1AN: Cover Ethernet.1AN 5/7/07 10:13 AM Page 4

Cover Ethernet.1AN: Cover Ethernet.1AN 5/7/07 10:13 AM Page 3 Ethernet Reference Guide Your everyday Ethernet testing reference tool Cover Ethernet.1AN: Cover Ethernet.1AN 5/7/07 10:13 AM Page 4 This guide provides a detailed overview of Ethernet technology. It presents common Ethernet implementations in service- provider networks, the testing requirements to ensure reliable service, as well as installation and maintenance techniques. Following its introduction in the early 1970s, the Ethernet protocol for data networking has been characterized by ever-increasing popularity and adaptation. In recent years, Ethernet has become the predominant network access protocol, now used in over 95% of all local-area networks. With the advent of Gigabit Ethernet and 10 Gigabit Ethernet, this technology has matured and made its way from local-area networks to metropolitan-area networks, and now wide-area networks, challenging traditional transport protocols such as SONET/SDH and ATM. www.exfo.com Guide Ethernet.1-ang: Guide Ethernet.1AN 5/7/07 10:06 AM Page 1 Table of Contents 2.7 Ethernet Frame Tag ..............................................................................23 2.8 VLAN Tagging........................................................................................23 Symbols Used in Illustrations................................................3 2.9 Traffic Priority ........................................................................................25 2.10 Frame Bursting ......................................................................................26 -

Ethernet Theory of Operation

AN1120 Ethernet Theory of Operation Author: M. Simmons However, with ubiquitous deployment, internet Microchip Technology Inc. connectivity, high data rates and limitless range expansibility, Ethernet can accommodate nearly all wired communications requirements. Potential INTRODUCTION applications include: This document specifies the theory and operation of • Remote sensing and monitoring the Ethernet technology found in PIC® MCUs with • Remote command, control and firmware updating integrated Ethernet and in stand-alone Ethernet • Bulk data transfer controllers. • Live streaming audio, video and media • Public data acquisition (date/time, stock quotes, Ethernet technology contains acronyms and terms news releases, etc.) defined in Table 1. THEORY OF OPERATION APPLICATIONS Ethernet is a data link and physical layer protocol Ethernet is an asynchronous Carrier Sense Multiple defined by the IEEE 802.3™ specification. It comes in Access with Collision Detect (CSMA/CD) many flavors, defined by maximum bit rate, mode of protocol/interface, with a payload size of 46-1500 octets. transmission and physical transmission medium. With data rates of tens to hundreds of megabits/second, it is generally not well suited for low-power applications. • Maximum Bit Rate (Mbits/s): 10, 100, 1000, etc. • Mode of Transmission: Broadband, Baseband • Physical Transmission Medium: Coax, Fiber, UTP, etc. TABLE 1: ETHERNET GLOSSARY Term Definition CRC Cyclic Redundancy Check: Type of checksum algorithm used when computing the FCS for all Ethernet frames and the hash table key for hash table filtering of receive packets. DA Destination Address: The 6-octet destination address field of an Ethernet frame. ESD End-of-Stream Delimiter: In 100 Mb/s operation, the ESD is transmitted after the FCS (during the inter-frame gap) to denote the end of the frame. -

Table of Contents

Table of Contents Section 1 Applications Support ... ------------ 1-1 Section 2 Introduction ________ ............... _. __ 2-1 Section 3 DP8390 Evaluation Board -------··· 3-2 Cable Installation --............... ----- 3-11 Section 4 - Software Reference Software Update -. -............... ---- 4-4 Computer Conferencing . ----------- 4-5 Demostration Network Software ---- 4-7 NIA Access Software ... ---------. -. 4-9 Network Load Simulator ... --------- 4-17 Network Evaluation Software------- 4-21 Writing Drivers for DP8390 ......... -- 4-25 Section 5 - Hardware Reference DP8390 Introductory Guide _... .. 5-1 Hardware Design Guide -. .. .. .. 5-9 Guide to Loopback -----. ......... 5-17 StarLAN with the DP8390 . .. .. .. 5-26 Section 6 Tranceiver Evaluation Kit . .. .. .. 6-1 SECTION 1 APPLICATION CONTACTS National Objectives Semiconductor Preliminary Corporati on July 1986 OBIECTIVE OF DP839EB CHEAPER/ETHER DEMONSTRATION KIT The Cheaper/Ether demonstration kit is intended to provide designers With tools tor evaluations and development of networking products usmg the DP839X chip set. The kit supports Ethernet, Cheapernet and Starlan networks as described in the IEEE 602.3 standard. All required documentation has been provided inside this binder. including the circuit diagram. PAL equations and option set tings. Software tools are also provided as guides to developing drivers tor the DP8390 Network Interface Controller. It is important to read all hardware and software manuals prior to inst.a1l1ng the demonstration kit. IN CASE OF PROBLEMS... If yC111 encounter problems not addressed in the documentation, contact your local Natianal Semicon ductor Field En&i."leer or Field Sales Office. They will provide you with any additional support you may require. I! you have ~ier "echnicai !nquiries regardin& operation of ~'lie JP839X chip set contact !'l'ational Semiconductor at (408) 72l 4247 (for the DP8390) or (408) 721 3M7 (DP8392 and !)PB391).