On Enhanced Clock Synchronization Performance Through Dedicated Ethernet Hardware Support

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Mikrodenetleyicili Endüstriyel Seri Protokol Çözümleyici Sisteminin Programi

YILDIZ TEKNİK ÜNİVERSİTESİ FEN BİLİMLERİ ENSTİTÜSÜ MİKRODENETLEYİCİLİ ENDÜSTRİYEL SERİ PROTOKOL ÇÖZÜMLEYİCİ SİSTEMİNİN PROGRAMI Elektronik ve Haberleşme Müh. Kemal GÜNSAY FBE Elektronik ve Haberleşme Anabilim Dalı Elektronik Programında Hazırlanan YÜKSEK LİSANS TEZİ Tez Danışmanı : Yrd. Doç. Dr. Tuncay UZUN (YTÜ) İSTANBUL, 2009 YILDIZ TEKNİK ÜNİVERSİTESİ FEN BİLİMLERİ ENSTİTÜSÜ MİKRODENETLEYİCİLİ ENDÜSTRİYEL SERİ PROTOKOL ÇÖZÜMLEYİCİ SİSTEMİNİN PROGRAMI Elektronik ve Haberleşme Müh. Kemal GÜNSAY FBE Elektronik ve Haberleşme Anabilim Dalı Elektronik Programında Hazırlanan YÜKSEK LİSANS TEZİ Tez Danışmanı : Yrd. Doç. Dr. Tuncay UZUN (YTÜ) İSTANBUL, 2009 İÇİNDEKİLER Sayfa KISALTMA LİSTESİ ................................................................................................................ v ŞEKİL LİSTESİ ...................................................................................................................... viii ÇİZELGE LİSTESİ .................................................................................................................... x ÖNSÖZ ...................................................................................................................................... xi ÖZET ........................................................................................................................................ xii ABSTRACT ............................................................................................................................ xiii 1. GİRİŞ ...................................................................................................................... -

Insert Paper Title Here

RADIATION-TOLERANT SYSTEM-ON-CHIP (SOC) WITH DETERMINISTIC ETHERNET SWITCHING FOR SCALABLE MODULAR LAUNCHER AVIONICS Christian Fidi, Ivan Masar, Jean-Francois Dufour, Mirko Jakovljevic, TTTech Computertechnik AG, Vienna, Austria for long duration manned missions that cannot be Keywords supported or resupplied from earth. Next-Gen Launcher Avionics, Integrated Modular Furthermore, increasing levels of integration and Architectures, Mixed Criticality Systems, SoC, Cyber- IMA capabilities allows the optimization of a set of Physical Systems, SAE AS6802, AFDX, TTEthernet functions, and new considerations on system architecture. Abstract Space Industry and COTS In space applications with very demanding Space industry is a low-volume industry which environment for electronic components, dedicated devices requires costly high-integrity components designed for are needed to ensure the required reliability and special space environments and operation time of over 20 availability for different mission profiles. Therefore, a years. To reduce system costs, open software platform dedicated reconfigurable radiation-tolerant SoC (System- standards and COTS components are considered in On-Chip) with integrated computing and Ethernet different programs. switching supports the design of future modular As an example, since the Constellation program, architectures. This work presents the motivation for its NASA’s strategy for the design of future spacecraft introduction and describes key SoC properties and architectures (including launchers, landers, etc.) has advances in high performance networking and heavily prioritized the use of COTS technologies for the semiconductor technology for scalable next-generation purpose of reducing cost, minimizing the required amount space avionics systems. of additional development, and removing the schedule risk associated with the creation of custom hardware. -

Synchronous Ethernet Solutions with Altera Fpgas and Silicon Labs Jitter-Attenuating Plls

Synchronous Ethernet Solutions with Altera FPGAs and Silicon Labs Jitter-Attenuating PLLs Hoss Rahbar, Product Marketing Manager, Altera Han Hua Leong, Design Engineer, IP and Device Software Engineering, Altera Bill Simcoe, Marketing Manager, Silicon Labs WP-01257-1.0 White Paper Introduction Synchronous clock signals are required for proper operation of voice communications, cellular wireless networks, passive optical networks (PONs), and a variety of other time-critical networking applications. Traditional time division multiplexed (TDM) telecom equipment—to support standards like Synchonous Optical Networking (SONET) and Synchronous Digital Hierarchy (SDH)—operate with synchronized clock signals. Nodes in these networks are synchronized to a primary reference clock (PRC) or primary reference source (PRS) with long-term frequency accuracy better than 1 part in 1011. The PRS/PRC clocks in TDM networks are provided by highly accurate and stable atomic clocks, or signals from the global positioning system (GPS). The clocks are then distributed to all the nodes in the network over the same connections that transport clients’ voice and data. The network nodes then synchronize their locally generated clocks to the PRS/PRC clock. Ethernet has become the network interface of choice in enterprise, metro, and some core networks. Ethernet networks can be used to transport voice, data, and video at high data rates for substantially lower equipment and service costs than traditional networks. Large capital savings can be realized by using Ethernet for synchronizing network nodes instead of using a more expensive specialized synchronous network. The IEEE 802.3 Ethernet standard is not specified to accurately transfer a clock from the transmitter to the receiver. -

Gigabit Ethernet

Ethernet Technologies and Gigabit Ethernet Professor John Gorgone Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 1 Topics • Origins of Ethernet • Ethernet 10 MBS • Fast Ethernet 100 MBS • Gigabit Ethernet 1000 MBS • Comparison Tables • ATM VS Gigabit Ethernet •Ethernet8SummaryCopyright 1998, John T. Gorgone, All Rights Reserved 2 Origins • Original Idea sprang from Abramson’s Aloha Network--University of Hawaii • CSMA/CD Thesis Developed by Robert Metcalfe----(1972) • Experimental Ethernet developed at Xerox Palo Alto Research Center---1973 • Xerox’s Alto Computers -- First Ethernet Ethernet8systemsCopyright 1998, John T. Gorgone, All Rights Reserved 3 DIX STANDARD • Digital, Intel, and Xerox combined to developed the DIX Ethernet Standard • 1980 -- DIX Standard presented to the IEEE • 1980 -- IEEE creates the 802 committee to create acceptable Ethernet Standard Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 4 Ethernet Grows • Open Standard allows Hardware and Software Developers to create numerous products based on Ethernet • Large number of Vendors keeps Prices low and Quality High • Compatibility Problems Rare Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 5 What is Ethernet? • A standard for LANs • The standard covers two layers of the ISO model – Physical layer – Data link layer Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 6 What is Ethernet? • Transmission speed of 10 Mbps • Originally, only baseband • In 1986, broadband was introduced • Half duplex and full duplex technology • Bus topology Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 7 Components of Ethernet • Physical Medium • Medium Access Control • Ethernet Frame Ethernet8 Copyright 1998, John T. Gorgone, All Rights Reserved 8 CableCable DesignationsDesignations 10 BASE T SPEED TRANSMISSION MAX TYPE LENGTH Ethernet8 Copyright 1998, John T. -

IEEE Std 802.3™-2012 New York, NY 10016-5997 (Revision of USA IEEE Std 802.3-2008)

IEEE Standard for Ethernet IEEE Computer Society Sponsored by the LAN/MAN Standards Committee IEEE 3 Park Avenue IEEE Std 802.3™-2012 New York, NY 10016-5997 (Revision of USA IEEE Std 802.3-2008) 28 December 2012 IEEE Std 802.3™-2012 (Revision of IEEE Std 802.3-2008) IEEE Standard for Ethernet Sponsor LAN/MAN Standards Committee of the IEEE Computer Society Approved 30 August 2012 IEEE-SA Standard Board Abstract: Ethernet local area network operation is specified for selected speeds of operation from 1 Mb/s to 100 Gb/s using a common media access control (MAC) specification and management information base (MIB). The Carrier Sense Multiple Access with Collision Detection (CSMA/CD) MAC protocol specifies shared medium (half duplex) operation, as well as full duplex operation. Speed specific Media Independent Interfaces (MIIs) allow use of selected Physical Layer devices (PHY) for operation over coaxial, twisted-pair or fiber optic cables. System considerations for multisegment shared access networks describe the use of Repeaters that are defined for operational speeds up to 1000 Mb/s. Local Area Network (LAN) operation is supported at all speeds. Other specified capabilities include various PHY types for access networks, PHYs suitable for metropolitan area network applications, and the provision of power over selected twisted-pair PHY types. Keywords: 10BASE; 100BASE; 1000BASE; 10GBASE; 40GBASE; 100GBASE; 10 Gigabit Ethernet; 40 Gigabit Ethernet; 100 Gigabit Ethernet; attachment unit interface; AUI; Auto Negotiation; Backplane Ethernet; data processing; DTE Power via the MDI; EPON; Ethernet; Ethernet in the First Mile; Ethernet passive optical network; Fast Ethernet; Gigabit Ethernet; GMII; information exchange; IEEE 802.3; local area network; management; medium dependent interface; media independent interface; MDI; MIB; MII; PHY; physical coding sublayer; Physical Layer; physical medium attachment; PMA; Power over Ethernet; repeater; type field; VLAN TAG; XGMII The Institute of Electrical and Electronics Engineers, Inc. -

Preparing Your Network for Synchronous Ethernet

APPLICATION BRIEF Preparing Your Network for Synchronous Ethernet As service providers transition to Ethernet of services, this network architecture 5 Easy Steps to SyncE based networks to support IP services, will evolve to native Ethernet. The main • Update existing network they must ensure the synchronization challenge, however, is that from a network synchronization plans to include SyncE distribution chain is maintained synchronization perspective native Ethernet • Assure that synchronization throughout the network. Without effective is not backward compatible with SONET/ infrastructure equipment supports SyncE ESMC (SSM) requirements and synchronization, real time applications SDH. SyncE solves this problem by allowing provides PRS traceability will at best suffer from degradation and at the Ethernet to be synchronized at the • Assure the new SyncE elements worst fail completely — giving a quality of physical layer using the same oscillator are equipped with redundant synchronization reference ports (G.703, experience far from consumer or service specifications as SDH/SONET. Using SyncE and/or J.211) provider expectations. as a replacement path for SONET/SDH • Conduct a sync audit allows operators to upgrade their network • Prepare for time distribution Synchronous Ethernet (SyncE) is one link by link without the need for a fork-lift requirements technology that provides frequency upgrade for the SSU clock distribution synchronization at the same level of SyncE Benefits elements. quality as existing SONET /SDH networks. • Assured high customer QoE while It enables operators to migrate to packet How SyncE Works migrating from SONET/SDH to Carrier Ethernet networking while retaining backward SyncE, specified by ITU standards • Synchronize Ethernet nodes at the compatibility with existing clock distribution G.8261-G.8263, builds on the existing same performance level as SONET/ SDH architectures. -

Gigabit Ethernet Pocket Guide

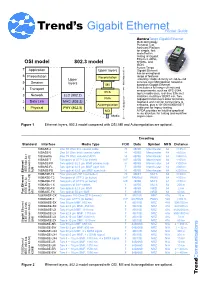

GbE.PocketG.fm Page 1 Friday, March 3, 2006 9:43 AM Carrier Class Ethernet, Metro Ethernet tester, Metro Ethernet testing, Metro Ethernet installation, Metro Ethernet maintenance, Metro Ethernet commissioning, Carrier Class Ethernet tester, Carrier Class Ethernet testing, Carrier Class Ethernet installation, Carrier Class Ethernet maintenance, Gigabit Ethernet tester, Gigabit Ethernet testing, Gigabit Ethernet installation, Gigabit Ethernet maintenance, Gigabit Ethernet commissioning, Gigabit Ethernet protocols, 1000BASE-T tester, 1000BASE-LX test, 1000BASE-SX test, 1000BASE-T testing, 1000BASE-LX testing Trend’s Gigabit EthernetPocket Guide AuroraTango Gigabit Ethernet Multi-technology Personal Test Assistant Platform for simple, fast and effective testing of Gigabit Ethernet, ADSL, OSI model 802.3 model SHDSL, and ISDN. Aurora Tango 7 Application Upper layers Gigabit Ethernet has an exceptional 6 Presentation Reconciliation range of features Upper ensuring reliable delivery of end-to-end 5 Session layers services over Metropolitan networks MII Media independent based on Gigabit Ethernet. 4 It includes a full range of tests and Transport measurements, such as RFC-2544, PCS top ten addresses, real-time Ethernet 3 Network LLC (802.2) statistics, multilayer BERT, etc. Two PMA Gigaport transceivers allow terminate, 2 Data Link MAC (803.3) loopback and monitor connections to Autonegotiation networks, plus a 10/100/1000BASE-T Physical cable port for legacy testing. 1 PHY (802.3) dependent Media MDI A PDA provides an intuitive graphical menu -

Synce Explained

WHITEPAPER Joan d’Austria, 112 - Barcelona - SP - 08018 Chalfont St Peter - Bucks - UK - SL9 9TR www.albedotelecom.com Synchronous Ethernet explained 1. FROM ASYNCHRONOUS TO SYNCHRONOUS ETHERNET Synchronous Ethernet is an ITU-T standard that provides mechanisms to trans- fer frequency over the Ethernet physical layer, which can then be made trace- able to an external source such as a network clock. On this case Ethernet links are part of the synchronization network (see Figure 2). The proposal to specify the transport of a reference clock over Ethernet links was brought by operators to ITU-T Study Group 15 in September 2004. The aim of Synchronous Ethernet is to avoid changes to the existing IEEE Ethernet, but to extend to work as a proper synchronous network. On many respects the evolution to a synchronous Ethernet network is equiva- lent to the one that occurred from PDH/T-Carrier to SDH/SONET and the causes are similar. The higher bit rates are the most important is to keep transmission synchronized by a unified clock in order to keep clock fluctuations and offsets under control as they are a main cause of errors a poor QoS. Despite being an IEEE standard, Ethernet architecture has been described in ITU-T G.8010 as a network made up of an ETH layer and a ETY layer. Written in simple terms, the ETY layer corresponds the physical layer as defined in IEEE 802.3, while the ETH layer represents the pure packet layer. Ethernet MAC Figure 1 ALBEDO Ether.Sync is a field tester for Synchronous Ethernet equipped with all the features to deploy SyncE infrastructures, Precision Time Protocol (PTP / IEEE 1588v2) and Gigabit Ethernet supporting legacy while new test such as eSAM Y.1564 All rights reserved. -

Hybridní Ethernet (1)

Hybridní Ethernet (1) • Jedná se o kombinaci dříve uvedených typů sítě Ethernet • Tuto kombinaci lze provést pomocí: – hybridního adaptéru (BNC/řada N): mezi tenkým a silným koaxiálním kabelem – repeateru: mezi tenkým a silným koaxiálním kabelem – hubu: mezi tenkým, silným koaxiálním kabelem a kroucenou dvojlinkou 2018-06-01 1 Hybridní Ethernet (2) RJ-45 BNC + T + BNC konektor # # # max. 100 (400) m Terminátor # # AUI konektor # # Hub N + T + N konektor nebo jehlový konektor Repeater min. 0,5 m max. 185 (300) m (300) 185 max. # # # m 500 max. Drop kabel Transceiver (MAU) (max 50 m) # # # # # min. 2,5 m 2018-06-01 2 10Broad36 (1) • Jako přenosové médium používá koaxiální kabel s char. impedancí Z0 = 75 W pracující v přeloženém pásmu • Činnost v přeloženém pásmu umožňuje, aby koaxiální kabel byl využíván i pro přenos jiných informací (např. video), než jsou data přenášená v síti • Jednotlivé stanice se ke koaxiálnímu kabelu připojují pomocí transceiveru a pomocného (drop) kabelu (max. 50 m) 2018-06-01 3 10Broad36 (2) • Maximální délka jednoho kabelu je 1800 m • Všechny sítě 10Broad36 jsou zakončeny pomocí tzv. head-end zařízení, které může být na konci jednoho kabelového segmentu nebo jako kořen více kabelových segmentů • Na druhém konci je síť ukončena termináto- rem • Tímto je možné zvětšit fyzický rozsah célé sítě až 3600 m (s drop kabely 3700 m) 2018-06-01 4 10Broad36 (3) • Síť 10Broad36 může být vybudována ve dvou konfiguracích: – s jedním koaxiálním kabelem: • datové přenosy jsou rozděleny do dvou kanálů, z nichž každý využívá jiné -

802.3Cz PHY Naming

F O P Knowledge Development 802.3cz PHY naming Rubén Pérez-Aranda Bob Grow IEEE 802.3cz Task Force - Nov 2020 Plenary F O About PHY naming P Knowledge Development • Naming for 802.3cz PHYs should be considered to start writing the draft • According to [1], the PHY naming in 802.3: • Evolved where required • Avoided conflicting definition • Not had same letter in the same position meaning something different • Provided limited description of naming in standard • In [2] nGBASE-AR for 802.3cz PHYs was proposed, assuming scrambled coding 64b/66b is used as in other short wavelength multimode PHYs, e.g. 10GBASE-SR. • 802.3cz PHYs naming should be consistent with the adopted baseline • i.e. if no scrambled coding 64b/66b is used, R should be avoided in the corresponding position • The TF is facing the development of multi-gigabit optical PHYs specification for a completely new application, i.e. Automotive, which demands very different requirements compared to data-centers PHYs • Proposed PCS/PMA baseline for 802.3cz is different (see [3]) wrt. BASE-R • Baseline is close to 802.3bv (BASE-H) in the transmit frame structure and PMA • However, very different in the PCS: PAM2 vs. PAM16, RS-FEC vs. MLCC, no THP • PMD baseline will have to be consistent with automotive reliability levels, with an MDI supporting automotive mechanical and environmental requirements, as well as a much wider temperature range of operation • Definitively, we have a very distinct PHY that should use different letters to designate the PHY type name IEEE 802.3cz Task Force - Nov 2020 -

Ethernet (IEEE 802.3)

Computer Networking MAC Addresses, Ethernet & Wi-Fi Lecturers: Antonio Carzaniga Silvia Santini Assistants: Ali Fattaholmanan Theodore Jepsen USI Lugano, December 7, 2018 Changelog ▪ V1: December 7, 2018 ▪ V2: March 1, 2017 ▪ Changes to the «tentative schedule» of the lecture 2 Last time, on December 5, 2018… 3 What about today? ▪Link-layer addresses ▪Ethernet (IEEE 802.3) ▪Wi-Fi (IEEE 802.11) 4 Link-layer addresses 5 Image source: https://divansm.co/letter-to-santa-north-pole-address/letter-to-santa-north-pole-address-fresh-day-18-santa-s-letters/ Network adapters (aka: Network interfaces) ▪A network adapter is a piece of hardware that connects a computer to a network ▪Hosts often have multiple network adapters ▪ Type ipconfig /all on a command window to see your computer’s adapters 6 Image source: [Kurose 2013 Network adapters: Examples “A 1990s Ethernet network interface controller that connects to the motherboard via the now-obsolete ISA bus. This combination card features both a BNC connector (left) for use in (now obsolete) 10BASE2 networks and an 8P8C connector (right) for use in 10BASE-T networks.” https://en.wikipedia.org/wiki/Network_interface_controller TL-WN851ND - WLAN PCI card 802.11n/g/b 300Mbps - TP-Link https://tinyurl.com/yamo62z9 7 Network adapters: Addresses ▪Each adapter has an own link-layer address ▪ Usually burned into ROM ▪Hosts with multiple adapters have thus multiple link- layer addresses ▪A link-layer address is often referred to also as physical address, LAN address or, more commonly, MAC address 8 Format of a MAC address ▪There exist different MAC address formats, the one we consider here is the EUI-48, used in Ethernet and Wi-Fi ▪6 bytes, thus 248 possible addresses ▪ i.e., 281’474’976’710’656 ▪ i.e., 281* 1012 (trillions) Image source: By Inductiveload, modified/corrected by Kju - SVG drawing based on PNG uploaded by User:Vtraveller. -

Ethernet Reference Guide Your Everyday Ethernet Testing Reference Tool Cover Ethernet.1AN: Cover Ethernet.1AN 5/7/07 10:13 AM Page 4

Cover Ethernet.1AN: Cover Ethernet.1AN 5/7/07 10:13 AM Page 3 Ethernet Reference Guide Your everyday Ethernet testing reference tool Cover Ethernet.1AN: Cover Ethernet.1AN 5/7/07 10:13 AM Page 4 This guide provides a detailed overview of Ethernet technology. It presents common Ethernet implementations in service- provider networks, the testing requirements to ensure reliable service, as well as installation and maintenance techniques. Following its introduction in the early 1970s, the Ethernet protocol for data networking has been characterized by ever-increasing popularity and adaptation. In recent years, Ethernet has become the predominant network access protocol, now used in over 95% of all local-area networks. With the advent of Gigabit Ethernet and 10 Gigabit Ethernet, this technology has matured and made its way from local-area networks to metropolitan-area networks, and now wide-area networks, challenging traditional transport protocols such as SONET/SDH and ATM. www.exfo.com Guide Ethernet.1-ang: Guide Ethernet.1AN 5/7/07 10:06 AM Page 1 Table of Contents 2.7 Ethernet Frame Tag ..............................................................................23 2.8 VLAN Tagging........................................................................................23 Symbols Used in Illustrations................................................3 2.9 Traffic Priority ........................................................................................25 2.10 Frame Bursting ......................................................................................26