Basic FET Amplifiers 315

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

LSK489 Application Note

LSK489 Application Note Low Noise Dual Monolithic JFET Bob Cordell Introduction For circuits designed to work with high impedance sources, ranging from electrometers to microphone preamplifiers, the use of a low-noise, high-impedance device between the input and the op amp is needed in order to optimize performance. At first glance, one of Linear Systems’ most popular parts, the LSK389 ultra-low-noise dual JFET would appear to be a good choice for such an application. The part’s high input impedance (1 T Ω) and low noise (1 nV/ √Hz at 1kHz and 2mA drain current) enables power transfer while adding almost no noise to the signal. But further examination of the LSK389’s specification shows an input capacitance of over 20pF. This will cause intermodulation distortion as the circuit’s input signal increases in frequency if the source impedance is high. This is because the JFET junction capacitances are nonlinear. This will be especially the case where common source amplifier arrangements allow the Miller effect to multiply the effective value of the gate-drain capacitance. Further, the LSK389’s input impedance will fall to a lower value as the frequency increases relative to a part with lower input capacitance. A better design choice is Linear Systems’ new offering, the LSK489. Though the LSK489 has slightly higher noise (1.5 nV/ √Hz vs. 1.0 nV/ √Hz) its much lower input capacitance of only 4pF means that it will maintain its high input impedance as the frequency of the input signal rises. More importantly, using the lower-capacitance LSK489 will create a circuit that is much less susceptible to intermodulation distortion than one using the LSK389. -

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

A GUIDE to USING FETS for SENSOR APPLICATIONS by Ron Quan

Three Decades of Quality Through Innovation A GUIDE TO USING FETS FOR SENSOR APPLICATIONS By Ron Quan Linear Integrated Systems • 4042 Clipper Court • Fremont, CA 94538 • Tel: 510 490-9160 • Fax: 510 353-0261 • Email: [email protected] A GUIDE TO USING FETS FOR SENSOR APPLICATIONS many discrete FETs have input capacitances of less than 5 pF. Also, there are few low noise FET input op amps Linear Systems that have equivalent input noise voltages density of less provides a variety of FETs (Field Effect Transistors) than 4 nV/ 퐻푧. However, there are a number of suitable for use in low noise amplifier applications for discrete FETs rated at ≤ 2 nV/ 퐻푧 in terms of equivalent photo diodes, accelerometers, transducers, and other Input noise voltage density. types of sensors. For those op amps that are rated as low noise, normally In particular, low noise JFETs exhibit low input gate the input stages use bipolar transistors that generate currents that are desirable when working with high much greater noise currents at the input terminals than impedance devices at the input or with high value FETs. These noise currents flowing into high impedances feedback resistors (e.g., ≥1MΩ). Operational amplifiers form added (random) noise voltages that are often (op amps) with bipolar transistor input stages have much greater than the equivalent input noise. much higher input noise currents than FETs. One advantage of using discrete FETs is that an op amp In general, many op amps have a combination of higher that is not rated as low noise in terms of input current noise and input capacitance when compared to some can be converted into an amplifier with low input discrete FETs. -

Power Electronics

Diodes and Transistors Semiconductors • Semiconductor devices are made of alternating layers of positively doped material (P) and negatively doped material (N). • Diodes are PN or NP, BJTs are PNP or NPN, IGBTs are PNPN. Other devices are more complex Diodes • A diode is a device which allows flow in one direction but not the other. • When conducting, the diodes create a voltage drop, kind of acting like a resistor • There are three main types of power diodes – Power Diode – Fast recovery diode – Schottky Diodes Power Diodes • Max properties: 1500V, 400A, 1kHz • Forward voltage drop of 0.7 V when on Diode circuit voltage measurements: (a) Forward biased. (b) Reverse biased. Fast Recovery Diodes • Max properties: similar to regular power diodes but recover time as low as 50ns • The following is a graph of a diode’s recovery time. trr is shorter for fast recovery diodes Schottky Diodes • Max properties: 400V, 400A • Very fast recovery time • Lower voltage drop when conducting than regular diodes • Ideal for high current low voltage applications Current vs Voltage Characteristics • All diodes have two main weaknesses – Leakage current when the diode is off. This is power loss – Voltage drop when the diode is conducting. This is directly converted to heat, i.e. power loss • Other problems to watch for: – Notice the reverse current in the recovery time graph. This can be limited through certain circuits. Ways Around Maximum Properties • To overcome maximum voltage, we can use the diodes in series. Here is a voltage sharing circuit • To overcome maximum current, we can use the diodes in parallel. -

PH-218 Lec-12: Frequency Response of BJT Amplifiers

Analog & Digital Electronics Course No: PH-218 Lec-12: Frequency Response of BJT Amplifiers Course Instructors: Dr. A. P. VAJPEYI Department of Physics, Indian Institute of Technology Guwahati, India 1 High frequency Response of CE Amplifier At high frequencies, internal transistor junction capacitances do come into play, reducing an amplifier's gain and introducing phase shift as the signal frequency increases. In BJT, C be is the B-E junction capacitance, and C bc is the B-C junction capacitance. (output to input capacitance) At lower frequencies, the internal capacitances have a very high reactance because of their low capacitance value (usually only a few pf) and the low frequency value. Therefore, they look like opens and have no effect on the transistor's performance. As the frequency goes up, the internal capacitive reactance's go down, and at some point they begin to have a significant effect on the transistor's gain. High frequency Response of CE Amplifier When the reactance of C be becomes small enough, a significant amount of the signal voltage is lost due to a voltage-divider effect of the source resistance and the reactance of C be . When the reactance of Cbc becomes small enough, a significant amount of output signal voltage is fed back out of phase with the input (negative feedback), thus effectively reducing the voltage gain. 3 Millers Theorem The Miller effect occurs only in inverting amplifiers –it is the inverting gain that magnifies the feedback capacitance. vin − (−Av in ) iin = = vin 1( + A)× 2π × f ×CF X C Here C F represents C bc vin 1 1 Zin = = = iin 1( + A)× 2π × f ×CF 2π × f ×Cin 1( ) Cin = + A ×CF 4 High frequency Response of CE Amp.: Millers Theorem Miller's theorem is used to simplify the analysis of inverting amplifiers at high-frequencies where the internal transistor capacitances are important. -

Common Drain - Wikipedia, the Free Encyclopedia 10-5-17 下午7:07

Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 Common drain From Wikipedia, the free encyclopedia In electronics, a common-drain amplifier, also known as a source follower, is one of three basic single- stage field effect transistor (FET) amplifier topologies, typically used as a voltage buffer. In this circuit the gate terminal of the transistor serves as the input, the source is the output, and the drain is common to both (input and output), hence its name. The analogous bipolar junction transistor circuit is the common- collector amplifier. In addition, this circuit is used to transform impedances. For example, the Thévenin resistance of a combination of a voltage follower driven by a voltage source with high Thévenin resistance is reduced to only the output resistance of the voltage follower, a small resistance. That resistance reduction makes the combination a more ideal voltage source. Conversely, a voltage follower inserted between a small load resistance and a driving stage presents an infinite load to the driving stage, an advantage in coupling a voltage signal to a small load. Characteristics At low frequencies, the source follower pictured at right has the following small signal characteristics.[1] Voltage gain: Current gain: Input impedance: Basic N-channel JFET source Output impedance: (the parallel notation indicates the impedance follower circuit (neglecting of components A and B that are connected in parallel) biasing details). The variable gm that is not listed in Figure 1 is the transconductance of the device (usually given in units of siemens). References http://en.wikipedia.org/wiki/Common_drain Page 1 of 2 Common drain - Wikipedia, the free encyclopedia 10-5-17 下午7:07 1. -

Cascode Amplifiers by Dennis L. Feucht Two-Transistor Combinations

Cascode Amplifiers by Dennis L. Feucht Two-transistor combinations, such as the Darlington configuration, provide advantages over single-transistor amplifier stages. Another two-transistor combination in the analog designer's circuit library combines a common-emitter (CE) input configuration with a common-base (CB) output. This article presents the design equations for the basic cascode amplifier and then offers other useful variations. (FETs instead of BJTs can also be used to form cascode amplifiers.) Together, the two transistors overcome some of the performance limitations of either the CE or CB configurations. Basic Cascode Stage The basic cascode amplifier consists of an input common-emitter (CE) configuration driving an output common-base (CB), as shown above. The voltage gain is, by the transresistance method, the ratio of the resistance across which the output voltage is developed by the common input-output loop current over the resistance across which the input voltage generates that current, modified by the α current losses in the transistors: v R A = out = −α ⋅α ⋅ L v 1 2 β + + + vin RB /( 1 1) re1 RE where re1 is Q1 dynamic emitter resistance. This gain is identical for a CE amplifier except for the additional α2 loss of Q2. The advantage of the cascode is that when the output resistance, ro, of Q2 is included, the CB incremental output resistance is higher than for the CE. For a bipolar junction transistor (BJT), this may be insignificant at low frequencies. The CB isolates the collector-base capacitance, Cbc (or Cµ of the hybrid-π BJT model), from the input by returning it to a dynamic ground at VB. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

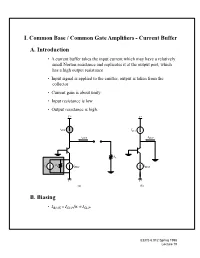

I. Common Base / Common Gate Amplifiers

I. Common Base / Common Gate Amplifiers - Current Buffer A. Introduction • A current buffer takes the input current which may have a relatively small Norton resistance and replicates it at the output port, which has a high output resistance • Input signal is applied to the emitter, output is taken from the collector • Current gain is about unity • Input resistance is low • Output resistance is high. V+ V+ i SUP ISUP iOUT IOUT RL R is S IBIAS IBIAS V− V− (a) (b) B. Biasing = /α ≈ • IBIAS ISUP ISUP EECS 6.012 Spring 1998 Lecture 19 II. Small Signal Two Port Parameters A. Common Base Current Gain Ai • Small-signal circuit; apply test current and measure the short circuit output current ib iout + = β v r gmv oib r − o ve roc it • Analysis -- see Chapter 8, pp. 507-509. • Result: –β ---------------o ≅ Ai = β – 1 1 + o • Intuition: iout = ic = (- ie- ib ) = -it - ib and ib is small EECS 6.012 Spring 1998 Lecture 19 B. Common Base Input Resistance Ri • Apply test current, with load resistor RL present at the output + v r gmv r − o roc RL + vt i − t • See pages 509-510 and note that the transconductance generator dominates which yields 1 Ri = ------ gm µ • A typical transconductance is around 4 mS, with IC = 100 A • Typical input resistance is 250 Ω -- very small, as desired for a current amplifier • Ri can be designed arbitrarily small, at the price of current (power dissipation) EECS 6.012 Spring 1998 Lecture 19 C. Common-Base Output Resistance Ro • Apply test current with source resistance of input current source in place • Note roc as is in parallel with rest of circuit g v m ro + vt it r − oc − v r RS + • Analysis is on pp. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Techniques for Low Power Analog, Digital and Mixed Signal CMOS

Louisiana State University LSU Digital Commons LSU Doctoral Dissertations Graduate School 2005 Techniques for low power analog, digital and mixed signal CMOS integrated circuit design Chuang Zhang Louisiana State University and Agricultural and Mechanical College, [email protected] Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool_dissertations Part of the Electrical and Computer Engineering Commons Recommended Citation Zhang, Chuang, "Techniques for low power analog, digital and mixed signal CMOS integrated circuit design" (2005). LSU Doctoral Dissertations. 852. https://digitalcommons.lsu.edu/gradschool_dissertations/852 This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Digital Commons. For more information, please [email protected]. TECHNIQUES FOR LOW POWER ANALOG, DIGITAL AND MIXED SIGNAL CMOS INTEGRATED CIRCUIT DESIGN A Dissertation Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy in The Department of Electrical and Computer Engineering by Chuang Zhang B.S., Tsinghua University, Beijing, China. 1997 M.S., University of Southern California, Los Angeles, U.S.A. 1999 M.S., Louisiana State University, Baton Rouge, U.S.A. 2001 May 2005 ACKNOWLEDGEMENTS I would like to dedicate my work to my parents, Mr. Jinquan Zhang and Mrs. Lingyi Yu and my wife Yiqian Wang, for their constant encouragement throughout my life. I am very grateful to my advisor Dr. Ashok Srivastava for his guidance, patience and understanding throughout this work. -

JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET Datasheet

JFE150 SLPS732 – JUNE 2021 JFE150 Ultra-Low Noise, Low Gate Current, Audio, N-Channel JFET 1 Features and yields excellent noise performance for currents from 50 μA to 20 mA. When biased at 5 mA, the • Ultra-low noise: device yields 0.8 nV/√Hz of input-referred noise, – Voltage noise: giving ultra-low noise performance with extremely high input impedance (> 1 TΩ). The JFE150 also • 0.8 nV/√Hz at 1 kHz, IDS = 5 mA features integrated diodes connected to separate • 0.9 nV/√Hz at 1 kHz, IDS = 2 mA – Current noise: 1.8 fA/√Hz at 1 kHz clamp nodes to provide protection without the addition • Low gate current: 10 pA (max) of high leakage, nonlinear external diodes. • Low input capacitance: 24 pF at VDS = 5 V The JFE150 can withstand a high drain-to-source • High gate-to-drain and gate-to-source breakdown voltage of 40-V, as well as gate-to-source and gate- voltage: –40 V to-drain voltages down to –40 V. The temperature • High transconductance: 68 mS range is specified from –40°C to +125°C. The device • Packages: Small SC70 and SOT-23 (Preview) is offered in 5-pin SOT-23 and SC-70 packages. 2 Applications Device Information • Microphone inputs PART NUMBER PACKAGE(1) BODY SIZE (NOM) • Hydrophones and marine equipment SOT-23 (5) - Preview 2.90 mm × 1.60 mm JFE150 • DJ controllers, mixers, and other DJ equipment SC-70 (5) 2.00 mm × 1.25 mm • Professional audio mixer or control surface • Guitar amplifier and other music instrument (1) For all available packages, see the package option addendum at the end of the data sheet.