Intel FPGA Programmable Acceleration Card N3000 Data Sheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Influence of Angular Velocity of Pedaling on the Accuracy of The

Research article 2018-04-10 - Rev08 Influence of Angular Velocity of Pedaling on the Accuracy of the Measurement of Cyclist Power Abstract Almost all cycling power meters currently available on the The miscalculation may be—even significantly—greater than we market are positioned on rotating parts of the bicycle (pedals, found in our study, for the following reasons: crank arms, spider, bottom bracket/hub) and, regardless of • the test was limited to only 5 cyclists: there is no technical and construction differences, all calculate power on doubt other cyclists may have styles of pedaling with the basis of two physical quantities: torque and angular velocity greater variations of angular velocity; (or rotational speed – cadence). Both these measures vary only 2 indoor trainer models were considered: other during the 360 degrees of each revolution. • models may produce greater errors; The torque / force value is usually measured many times during slopes greater than 5% (the only value tested) may each rotation, while the angular velocity variation is commonly • lead to less uniform rotations and consequently neglected, considering only its average value for each greater errors. revolution (cadence). It should be noted that the error observed in this analysis This, however, introduces an unpredictable error into the power occurs because to measure power the power meter considers calculation. To use the average value of angular velocity means the average angular velocity of each rotation. In power meters to consider each pedal revolution as perfectly smooth and that use this type of calculation, this error must therefore be uniform: but this type of pedal revolution does not exist in added to the accuracy stated by the manufacturer. -

Basement Flood Mitigation

1 Mitigation refers to measures taken now to reduce losses in the future. How can homeowners and renters protect themselves and their property from a devastating loss? 2 There are a range of possible causes for basement flooding and some potential remedies. Many of these low-cost options can be factored into a family’s budget and accomplished over the several months that precede storm season. 3 There are four ways water gets into your basement: Through the drainage system, known as the sump. Backing up through the sewer lines under the house. Seeping through cracks in the walls and floor. Through windows and doors, called overland flooding. 4 Gutters can play a huge role in keeping basements dry and foundations stable. Water damage caused by clogged gutters can be severe. Install gutters and downspouts. Repair them as the need arises. Keep them free of debris. 5 Channel and disperse water away from the home by lengthening the run of downspouts with rigid or flexible extensions. Prevent interior intrusion through windows and replace weather stripping as needed. 6 Many varieties of sturdy window well covers are available, simple to install and hinged for easy access. Wells should be constructed with gravel bottoms to promote drainage. Remove organic growth to permit sunlight and ventilation. 7 Berms and barriers can help water slope away from the home. The berm’s slope should be about 1 inch per foot and extend for at least 10 feet. It is important to note permits are required any time a homeowner alters the elevation of the property. -

Simple Harmonic Motion

[SHIVOK SP211] October 30, 2015 CH 15 Simple Harmonic Motion I. Oscillatory motion A. Motion which is periodic in time, that is, motion that repeats itself in time. B. Examples: 1. Power line oscillates when the wind blows past it 2. Earthquake oscillations move buildings C. Sometimes the oscillations are so severe, that the system exhibiting oscillations break apart. 1. Tacoma Narrows Bridge Collapse "Gallopin' Gertie" a) http://www.youtube.com/watch?v=j‐zczJXSxnw II. Simple Harmonic Motion A. http://www.youtube.com/watch?v=__2YND93ofE Watch the video in your spare time. This professor is my teaching Idol. B. In the figure below snapshots of a simple oscillatory system is shown. A particle repeatedly moves back and forth about the point x=0. Page 1 [SHIVOK SP211] October 30, 2015 C. The time taken for one complete oscillation is the period, T. In the time of one T, the system travels from x=+x , to –x , and then back to m m its original position x . m D. The velocity vector arrows are scaled to indicate the magnitude of the speed of the system at different times. At x=±x , the velocity is m zero. E. Frequency of oscillation is the number of oscillations that are completed in each second. 1. The symbol for frequency is f, and the SI unit is the hertz (abbreviated as Hz). 2. It follows that F. Any motion that repeats itself is periodic or harmonic. G. If the motion is a sinusoidal function of time, it is called simple harmonic motion (SHM). -

Hub City Powertorque® Shaft Mount Reducers

Hub City PowerTorque® Shaft Mount Reducers PowerTorque® Features and Description .................................................. G-2 PowerTorque Nomenclature ............................................................................................ G-4 Selection Instructions ................................................................................ G-5 Selection By Horsepower .......................................................................... G-7 Mechanical Ratings .................................................................................... G-12 ® Shaft Mount Reducers Dimensions ................................................................................................ G-14 Accessories ................................................................................................ G-15 Screw Conveyor Accessories ..................................................................... G-22 G For Additional Models of Shaft Mount Reducers See Hub City Engineering Manual Sections F & J DOWNLOAD AVAILABLE CAD MODELS AT: WWW.HUBCITYINC.COM Certified prints are available upon request EMAIL: [email protected] • www.hubcityinc.com G-1 Hub City PowerTorque® Shaft Mount Reducers Ten models available from 1/4 HP through 200 HP capacity Manufacturing Quality Manufactured to the highest quality 98.5% standards in the industry, assembled Efficiency using precision manufactured components made from top quality per Gear Stage! materials Designed for the toughest applications in the industry Housings High strength ductile -

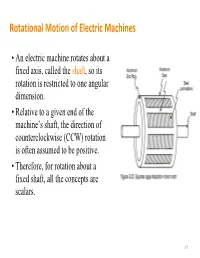

Rotational Motion of Electric Machines

Rotational Motion of Electric Machines • An electric machine rotates about a fixed axis, called the shaft, so its rotation is restricted to one angular dimension. • Relative to a given end of the machine’s shaft, the direction of counterclockwise (CCW) rotation is often assumed to be positive. • Therefore, for rotation about a fixed shaft, all the concepts are scalars. 17 Angular Position, Velocity and Acceleration • Angular position – The angle at which an object is oriented, measured from some arbitrary reference point – Unit: rad or deg – Analogy of the linear concept • Angular acceleration =d/dt of distance along a line. – The rate of change in angular • Angular velocity =d/dt velocity with respect to time – The rate of change in angular – Unit: rad/s2 position with respect to time • and >0 if the rotation is CCW – Unit: rad/s or r/min (revolutions • >0 if the absolute angular per minute or rpm for short) velocity is increasing in the CCW – Analogy of the concept of direction or decreasing in the velocity on a straight line. CW direction 18 Moment of Inertia (or Inertia) • Inertia depends on the mass and shape of the object (unit: kgm2) • A complex shape can be broken up into 2 or more of simple shapes Definition Two useful formulas mL2 m J J() RRRR22 12 3 1212 m 22 JRR()12 2 19 Torque and Change in Speed • Torque is equal to the product of the force and the perpendicular distance between the axis of rotation and the point of application of the force. T=Fr (Nm) T=0 T T=Fr • Newton’s Law of Rotation: Describes the relationship between the total torque applied to an object and its resulting angular acceleration. -

PHYS 211 Lecture 5 - Oscillations: Simple Harmonic Motion 5 - 1

PHYS 211 Lecture 5 - Oscillations: simple harmonic motion 5 - 1 Lecture 5 - Oscillations: simple harmonic motion Text: Fowles and Cassiday, Chap. 3 Consider a power series expansion for the potential energy of an object 2 V(x) = Vo + V1x + V2x + ..., where x is the displacement of an object from its equilibrium position, and Vi, i = 0,1,2... are fixed coefficients. The leading order term in this series is unimportant to the dynamics of the object, since F = -dV/dx and the derivative of a constant vanishes. Further, if we require the equilibrium position x = 0 to be a true minimum in the energy, then V1 = 0. This doesn’t mean that potentials with odd powers in x must vanish, but just says that their minimum is not at x = 0. Thus, the simplest function that one can write is quadratic: 2 V = V2x [A slightly more complicated variant is |x| = (x2)1/2, which is not smooth at x = 0]. For small excursions from equilibrium, the quadratic term is often the leading-order piece of more complex functions such as the Morse or Lennard-Jones potentials. Quadratic potentials correspond to the familiar Hooke’s Law of ideal springs V(x) = kx 2/2 => F(x) = -dV/dx = -(2/2)kx = -kx, where k is the spring constant. Objects subject to Hooke’s Law exhibit oscillatory motion, as can be seen by solving the differential equation arising from Newton’s 2nd law: F = ma => -kx = m(d 2x/dt 2) or d 2x /dt 2 + (k/m)x = 0. We solved this equation in PHYS 120: x(t) = A sin( ot + o) Other functional forms such as cosine can be changed into this form using a suitable choice of the phase angle o. -

Determining the Load Inertia Contribution from Different Power Consumer Groups

energies Article Determining the Load Inertia Contribution from Different Power Consumer Groups Henning Thiesen * and Clemens Jauch Wind Energy Technology Institute (WETI), Flensburg University of Applied Sciences, 24943 Flensburg, Germany; clemens.jauch@hs-flensburg.de * Correspondence: henning.thiesen@hs-flensburg.de Received: 27 February 2020; Accepted: 25 March 2020 ; Published: 1 April 2020 Abstract: Power system inertia is a vital part of power system stability. The inertia response within the first seconds after a power imbalance reduces the velocity of which the grid frequency changes. At present, large shares of power system inertia are provided by synchronously rotating masses of conventional power plants. A minor part of power system inertia is supplied by power consumers. The energy system transformation results in an overall decreasing amount of power system inertia. Hence, inertia has to be provided synthetically in future power systems. In depth knowledge about the amount of inertia provided by power consumers is very important for a future application of units supplying synthetic inertia. It strongly promotes the technical efficiency and cost effective application. A blackout in the city of Flensburg allows for a detailed research on the inertia contribution from power consumers. Therefore, power consumer categories are introduced and the inertia contribution is calculated for each category. Overall, the inertia constant for different power consumers is in the range of 0.09 to 4.24 s if inertia constant calculations are based on the power demand. If inertia constant calculations are based on the apparent generator power, the load inertia constant is in the range of 0.01 to 0.19 s. -

Rotation: Moment of Inertia and Torque

Rotation: Moment of Inertia and Torque Every time we push a door open or tighten a bolt using a wrench, we apply a force that results in a rotational motion about a fixed axis. Through experience we learn that where the force is applied and how the force is applied is just as important as how much force is applied when we want to make something rotate. This tutorial discusses the dynamics of an object rotating about a fixed axis and introduces the concepts of torque and moment of inertia. These concepts allows us to get a better understanding of why pushing a door towards its hinges is not very a very effective way to make it open, why using a longer wrench makes it easier to loosen a tight bolt, etc. This module begins by looking at the kinetic energy of rotation and by defining a quantity known as the moment of inertia which is the rotational analog of mass. Then it proceeds to discuss the quantity called torque which is the rotational analog of force and is the physical quantity that is required to changed an object's state of rotational motion. Moment of Inertia Kinetic Energy of Rotation Consider a rigid object rotating about a fixed axis at a certain angular velocity. Since every particle in the object is moving, every particle has kinetic energy. To find the total kinetic energy related to the rotation of the body, the sum of the kinetic energy of every particle due to the rotational motion is taken. The total kinetic energy can be expressed as .. -

For POWER SPEED ATHLETES

NUTRITIONAL CONSIDERATIONS & STRATEGIES for POWER SPEED ATHLETES Landon Evans, MS, RD, CSCS 2017 USTFCCCA NATIONAL CONFERENCE University of IOWA DISCLOSURE I have no financial relationship to the audience. 2017 USTFCCCA NATIONAL CONFERENCE 2 NUTRITION POWER SPEED ATHLETES Polarizing topic (to put it mildly) Perspective tuning OUTLINE Nutritional analysis Framework (the less debatable) Special considerations 2017 USTFCCCA NATIONAL NUTRITION POWER SPEED ATHLETES CONFERENCE Top 3 Emotionally Fueled Topics on Earth 1. Religion POLARIZING TOPIC 2. Politics 3. Nutrition https://hollandsopus.files.wordpress.com/2011/05/man_yelling_at_computer.jpg Bonus #4 (in my life with 2 young daughters): Glitter 2017 USTFCCCA NATIONAL NUTRITION POWER SPEED ATHLETES CONFERENCE Coach’s mortgage depends on their athletes’ successes. Coach gets frustrated with outcomes. Coach turns to judging/critiquing lifestyle POLARIZING You need to gain You need to 30lbs to compete in this lose 10lbs TOPIC conference How do you expect to recover You should when you’re doing eat less carbs [___]?! You should stop eating gluten 2017 USTFCCCA NATIONAL NUTRITION POWER SPEED ATHLETES CONFERENCE YOU NEED TO OK [________] Coach, but how? YOU POLARIZING NEED TO OK TOPIC [________] Coach, but last time I did that and I [____] 100 possible thoughts or statements 2017 USTFCCCA NATIONAL NUTRITION POWER SPEED ATHLETES CONFERENCE ANOTHER PFAFFISM Training is overrated Henk K, Dan P 2014 Seminar PERSPECTIVE TUNING 2017 USTFCCCA NATIONAL NUTRITION POWER SPEED ATHLETES CONFERENCE PERSPECTIVE TUNING 2017 USTFCCCA NATIONAL NUTRITION POWER SPEED ATHLETES CONFERENCE (some) Dietitians are great… But the most effective nutritionists are PERSPECTIVE the ones that can COACH it. TUNING So, in a large part, YOU (coaches) are a lot more effective than I will ever be for your group/team. -

Rotational Motion and Angular Momentum 317

CHAPTER 10 | ROTATIONAL MOTION AND ANGULAR MOMENTUM 317 10 ROTATIONAL MOTION AND ANGULAR MOMENTUM Figure 10.1 The mention of a tornado conjures up images of raw destructive power. Tornadoes blow houses away as if they were made of paper and have been known to pierce tree trunks with pieces of straw. They descend from clouds in funnel-like shapes that spin violently, particularly at the bottom where they are most narrow, producing winds as high as 500 km/h. (credit: Daphne Zaras, U.S. National Oceanic and Atmospheric Administration) Learning Objectives 10.1. Angular Acceleration • Describe uniform circular motion. • Explain non-uniform circular motion. • Calculate angular acceleration of an object. • Observe the link between linear and angular acceleration. 10.2. Kinematics of Rotational Motion • Observe the kinematics of rotational motion. • Derive rotational kinematic equations. • Evaluate problem solving strategies for rotational kinematics. 10.3. Dynamics of Rotational Motion: Rotational Inertia • Understand the relationship between force, mass and acceleration. • Study the turning effect of force. • Study the analogy between force and torque, mass and moment of inertia, and linear acceleration and angular acceleration. 10.4. Rotational Kinetic Energy: Work and Energy Revisited • Derive the equation for rotational work. • Calculate rotational kinetic energy. • Demonstrate the Law of Conservation of Energy. 10.5. Angular Momentum and Its Conservation • Understand the analogy between angular momentum and linear momentum. • Observe the relationship between torque and angular momentum. • Apply the law of conservation of angular momentum. 10.6. Collisions of Extended Bodies in Two Dimensions • Observe collisions of extended bodies in two dimensions. • Examine collision at the point of percussion. -

Work, Power, & Energy

WORK, POWER, & ENERGY In physics, work is done when a force acting on an object causes it to move a distance. There are several good examples of work which can be observed everyday - a person pushing a grocery cart down the aisle of a grocery store, a student lifting a backpack full of books, a baseball player throwing a ball. In each case a force is exerted on an object that caused it to move a distance. Work (Joules) = force (N) x distance (m) or W = f d The metric unit of work is one Newton-meter ( 1 N-m ). This combination of units is given the name JOULE in honor of James Prescott Joule (1818-1889), who performed the first direct measurement of the mechanical equivalent of heat energy. The unit of heat energy, CALORIE, is equivalent to 4.18 joules, or 1 calorie = 4.18 joules Work has nothing to do with the amount of time that this force acts to cause movement. Sometimes, the work is done very quickly and other times the work is done rather slowly. The quantity which has to do with the rate at which a certain amount of work is done is known as the power. The metric unit of power is the WATT. As is implied by the equation for power, a unit of power is equivalent to a unit of work divided by a unit of time. Thus, a watt is equivalent to a joule/second. For historical reasons, the horsepower is occasionally used to describe the power delivered by a machine. -

In-Class Problems 23-24: Harmonic Oscillation and Mechanical Energy: Solution

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Department of Physics Physics 8.01 TEAL Fall Term 2004 In-Class Problems 23-24: Harmonic Oscillation and Mechanical Energy: Solution Problem 22: Journey to the Center of the Earth Imagine that one drilled a hole with smooth sides straight through the center of the earth. If the air is removed from this tube (and it doesn’t fill up with water, liquid rock, or iron from the core) an object dropped into one end will have enough energy to just exit the other end after an interval of time. Your goal is to find that interval of time. a) The gravitational force on an object of mass m, located inside the earth a distance r < Re, from the center (Re is the radius of the earth), is due only to the mass of the earth that lies within a solid sphere of radius r. What is the gravitational force as a function of the distance r from the center? Express your answer in terms of g and Re . Note: you do not need the mass of the earth to answer this question. You only need to assume that the earth is of uniform density. Answer: Choose a radial coordinate with unit vector rˆ pointing outwards. The gravitational force on an object of mass m at the surface of the earth is given by two expressions Gmm v e ˆ ˆ Fgrav =− 2 r =−mgr . Re Therefore we can solve for the gravitational constant acceleration 1 Gme g = 2 . Re When the object is a distance r from the center of the earth, the mass of the earth that lies outside the sphere of radius r does not contribute to the gravitational force.