Doublethink AT&T DSP3210+68040 CPU Board Specs

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Openbsd Gaming Resource

OPENBSD GAMING RESOURCE A continually updated resource for playing video games on OpenBSD. Mr. Satterly Updated August 7, 2021 P11U17A3B8 III Title: OpenBSD Gaming Resource Author: Mr. Satterly Publisher: Mr. Satterly Date: Updated August 7, 2021 Copyright: Creative Commons Zero 1.0 Universal Email: [email protected] Website: https://MrSatterly.com/ Contents 1 Introduction1 2 Ways to play the games2 2.1 Base system........................ 2 2.2 Ports/Editors........................ 3 2.3 Ports/Emulators...................... 3 Arcade emulation..................... 4 Computer emulation................... 4 Game console emulation................. 4 Operating system emulation .............. 7 2.4 Ports/Games........................ 8 Game engines....................... 8 Interactive fiction..................... 9 2.5 Ports/Math......................... 10 2.6 Ports/Net.......................... 10 2.7 Ports/Shells ........................ 12 2.8 Ports/WWW ........................ 12 3 Notable games 14 3.1 Free games ........................ 14 A-I.............................. 14 J-R.............................. 22 S-Z.............................. 26 3.2 Non-free games...................... 31 4 Getting the games 33 4.1 Games............................ 33 5 Former ways to play games 37 6 What next? 38 Appendices 39 A Clones, models, and variants 39 Index 51 IV 1 Introduction I use this document to help organize my thoughts, files, and links on how to play games on OpenBSD. It helps me to remember what I have gone through while finding new games. The biggest reason to read or at least skim this document is because how can you search for something you do not know exists? I will show you ways to play games, what free and non-free games are available, and give links to help you get started on downloading them. -

* Reader Su PPC Review * Classified * the Latest News

_ • in • • • Ai • _ • _ • - • • • • • • • • h h •••••.• • .* • II • • ••••••• • a_ • • • • • • • • • • in_ a_ s_ • • • • U.S. •••••.• • :•:a:• • • • • • • • .• .7 * Reader Su rvey PPC Review s . * Classified * The Latest News * Best- of pp ,.._, .... ,..„....,.. , ":9 !linter ,„,...,,,,::,, * Alfi ga & 4(..- *- • - • *--.... , -* 4,-*-...-A- • 11_-e._i_. • -j.i •-+ .- - *, +4,,,iri. , .* , ism.m_-.!....!....., XI a 0 i r_tui,je! 4I.! .1.' . i _ • . a_ 25.. • - IS X ''''' ;!:::-*.:!,(::-- ,.. 1- 11.- • - a 16_1! .. ! .,..,...,.....,,,._,..,„,_ - illi.i.ia_ il'ig_.• i CDI Pia ,......-......-7.-7.7:-.....-..,..-:-....„.. ._._•_ a. x_ •_ •_ •_ s V i _ V Tli IS_ ill ill a_a_n_ a_ a_ 2_ a_ a. ii. i_ iti_Liai_ it- ii_iiii_ iti_ii_ ii_lit_ i_ -a- i_ ii 6_ -• it_ it i_ ; it_ i i-i*:`•,a- ii. ii*._ iS i._ ilLial'-`•!_la. N. it.. a- •••••a_a_s .. , it ti-it • •-•••••••••••• r'..e4 Australian Dollar Down 12% International freight up 8% Last Chance before the price rise. HARDWARE SOFTWARE GREEN MOUSE $ 25.00 ALL NEW. NO SECOND HAND GOODS HYPER MOUSE II $ 35.00 AMINET CD $ 25.00 FI GRAND PRIX $ 35.00 ROCFIRE JOYSTICK $ 24.00 AMINET CD 8,10,13,15. $10.00 PRIME MOVER $ 35.00 PEN MOUSE $ 24.00 AMINET SETS 1,2 $ 39.00 XTREME RACING $ 20.00 HAND SCANNER 64 G/S $ 150.00 AMINET SETS 3,4,5 $55.00 OVERDRIVE $ 35.00 EURO CD 2 $ 24.95 F117 A $ 35.00 WITH FULL OCR & TOUCHUP 4 MONUMENT PRO V3 $ 460.00 F 19 $ 35.00 SECUREKEY $ 64.95 ADORAGE $ 160.00 DOG FIGHT $ 29.00 880K EXTERNAL DRIVE $ 99.00 ANIMAGE $150.00 B17 FLYING FORTRESS $ 35.00 CLARISSA ROCGEN AGA $ 190.00 -

Company Model #1 #2 Av. Price EUR # Sales Market Acorn System 1 300

Company Model #1 #2 Av. price EUR # sales Market Acorn System 1 300 2 600 Acorn A4 184 7 1288 Acorn Atom 164 35 5740 MITS Altair 680 1016 6 6096 MITS Altair 8800; 8800b 10000 1796 39 70044 APF Imagination Machine 347 2 694 Apple I 180 25072 2 50144 Apple III 65000 274 49 13426 Apple Lisa 1 9143 2 18286 Apple Lisa 2 100000 613 79 48427 Apple 20th anniversary Mac 498 43 21414 Atari 4160STE 156 3 468 Atari 1200XL 82 55 4510 Atari 800XE 32 64 2048 Atari ATW800 200 250 Atari ST Book 1000 1200 561 10 5610 Atari Stacy 216 49 10584 Atari TT 156 134 20904 Atari Falcon 14000 284 191 54244 Be BeBox 1900 869 15 13035 Bit Corporation BIT 90 48 2 96 Camputers Lynx 48, 96, 128 30000 113 23 2599 Canon Cat 20000 716 4 2864 Commodore 4064; Educator 342 7 2394 Commodore P500 1500 3000 419 6 2514 Commodore 610 / 620 142 32 4544 Commodore 710 / 720 192 20 3840 Commodore C116 10000 45 108 4860 Commodore C64 (Golden) 200 1000 2932 3 8796 Commodore MAX Machine 396 17 6732 Commodore 3008 254 1 254 Commodore SX64 89000 94 489 45966 Commodore PET 2001 10000 191 211 40301 Commodore SuperPET 9000 150 9 1350 Commodore Amiga 3000 235 174 40890 Commodore Amiga 3000T Commodore Amiga 4000 302 267 80634 Commodore Amiga 4000T 677 45 30465 Commodore; MOS KIM-1 261 57 14877 Compukit UK-101 240 5 1200 Comx COMX35 79 6 474 Comx PC1 57 1 57 Cybervision Cybervision 2001 190 2 380 Digital Equipment VK100 64 1 64 Dragon 64 69 23 1587 Dragon 200 / 200E 202 1 202 EACA Colour Genie EG2000 64 17 1088 EAW P8000 389 8 3112 EO 440/880 10000 205 1 205 Enterprise 64 111 12 1332 Enterprise -

Hwb: the Hardware Book (Offline)

HwB: The Hardware Book (Offline) Welcome to the Hardware Book. Internet's largest free collection of connector pinouts and cable descriptions. Newsflash! A new version of The Hardware Book has been released as of 2001-06-08! See News for more details. This is an offline version, the latest release of HwB can be found at http://www.hardwarebook.net/. Connectors Pinouts for connectors, buses etc. Cables How to build serial cables and many other cables. Adapters How to build adapters. Circuits Misc circuits (active filters etc). Tables Misc tables with info. (AWG..) WWW Links Links to other electronic resources. News News information about The Hardware Book. Wanted Information we are currently looking for. About Who did this? And why? Comment Send your comments to the author. Copyright © The Hardware Book Team 1996-2001. May be copied and redistributed, partially or in whole, as apropriate. Document last modified: 2001-06-08 file:///C|/tmp/tech/HwB/index.html [6/14/2001 11:59:19 PM] HwB: Connector Menu (Offline) [ Audio/Video | Buses | Cartridges/Expansions | Cellular Phones | Memories | Misc | Networks | Parallel | PC | Power Supply | Serial | Storage | Mice/Keyboards/Joysticks ] What does the information that is listed for each connector mean? See the tutorial. Audio/Video Audio ActionMedia 2 Audio/Video Capture Amiga 1000 RF Monitor Apple AudioVision CBM 1902A NeoGeo Audio/Video Sony RGB Multi Input TI-99/4A Video/Audio Consoles Atari Jaguar A/V N64 Video PlayStation A/V Sega Dreamcast A/V Sega Genesis 2/32X/Nomad A/V Sega Genesis/Master -

A4000/A3000 Hardware

A4000/A3000 H ardware D eveloper N otes P art I: T he Z orro III Bus S pecification P art II: T he A miga Local B us Slot P art III: T he A miga V ideo S lot Document Revision 1.11 December 1992 by Dave Haynie with Scott Schaeffer, Scott Hood and Dan Baker Copyright © 1990,1991,1992 Commodore-Amiga, Inc. Important Information "A life spent maJäng mistakes is not onty more honorable but more usefuljhan a life spent doing nothing." -George Bernard Shaw This Pocument Contains Preliminarv Information The Information contained here is preliminary in nature and subject to possible errors and omissions. Few Zorro ID cards have yet been designed, so some features described here have not actually been tested in a System, or in some cases, actuaUy implemented as of this wridng. That, of course, is one major reason for having a specification in the first place. Commodore Technology reserves the right to correct any mistake, error, omission (or viscious lie). Corrections will be published as Updates to this document, which will be released as necessary. Revisions will be tracked via the revison number that appears on the front cover. New revisions will always list the conections up front, and developers will be kept up to date on released revisions via the normal CATS channels. All Information herein is Copyright © 1990,1991,1992 by Commodore-Amiga, Inc., and may not be reproduced in any form without permission. A cknowledgements "Art is I; Science is we." -Claude Bernard I’d like to acknowledge the following people and groups, without whom this new stuff would have been impossible: • The original Amiga designers, for designing the first microcomputer bus with support for multiple masters, Software board configuration, and room to grow. -

Multifacesoftware Multifacecard Serialmaster

MultiFaceSoftware MultiFaceCard SerialMaster 1 English 2 MultiFaceSoftware MultiFaceCard SerialMaster 3 License Agreements This product is copyright protected. No part of this product may be copied, distributed or processed electronically or any other means without written consent of bsc büroautomation AG. The buyer is granted a non-exclusive right of use with one Computer respectively. We guarantee warranty for the original product from the date of purchase, under the condition that the registration card is returned to us immediately after the purchase. Warranty covers the rectification of evident flaws of material or function for products that are sent to us freight paid and with a copy of the receipt. Change or repair of parts does not extend the term of warranty. If the product is not installed or used according to design and instructions or if it was altered or modified or if the computer is deficient, the warranty is void. We reject any liability for damages caused directly or indirectly by the product. We guarantee however, having performed a thorough product quality test with the result of flawless performance prior to shipment. We reserve the right to technical changes and changes in the contents of this product. All rights reserved. Copyright 1991-1993 bsc büroautomation AG Trademarks »Commodore«, the Commodore Logo, and »CBM« are registered trademarks of Commodore Electronics Limited. »Amiga«, »AmigaDOS«, »Amiga Kickstart«, »Amiga Workbench« and »AUTOCONFIG« are registered trademarks of Commodore Electronics Limited. »Centronics« is a registered trademark of Centronics Data Computer Corp. »Epson« is a registered trademark of Epson America, Inc. »LaserJet« is a registered trademark of Hewlett-Packard Company. -

Concierto Das Picasso IV Soundmodul

Concierto Das Picasso IV Soundmodul Handbuch 18. August 1997 Copyright c 1997 Village Tronic Marketing GmbH MuhlenstraûeÈ 2 31157 Sarstedt Technische Hotline: Tel. 05066 / 7013-10 FAX: Tel. 05066 / 7013-49 Rechtliches Die vorliegende Publikation ist urheberrechtlich geschutzt.È Alle Rechte vorbehalten. Dieses Handbuch darf in keiner Form, auch auszugsweise, ohne schriftliche Geneh- migung der Village Tronic Marketing GmbH durch Fotokopie, Mikro®lm, Textdatei oder andere Verfahren reproduziert, vervielfaltigt,È verbreitet oder in andere Sprachen ubersetztÈ werden. Bei der Erstellung von Hardware und Begleitmaterial wurde mit groûterÈ Sorgfalt vorgegangen. Trotzdem lassen sich Fehler nicht vollkommen ausschlieûen. Die Village Tronic Marketing GmbH ubernimmtÈ keine Haftung furÈ Schaden,È die mittel- oder unmittelbar durch den Einsatz der Concierto entstehen oder zuruckzufÈ uhrenÈ sind. In diesem Handbuch wird ohne besondere Kennzeichnung bezug auf weitere Produkte genommen, die dennoch warenzeichen- oder urheberrechtlich geschutztÈ sein konnen.È Hardware: Paul Jordan, Frank Otto Software: Olaf Barthel Handbuch: Olaf Barthel Inhaltsverzeichnis 1 Leistungsumfang der Concierto 3 : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : 1.1 Digitalton : 3 : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : 1.2 Synthesizer : 3 : : : : : : : : : : : : : : : : : : : : : : : : : : : : 1.3 Klangmischer : 3 : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : 1.4 MIDI : 3 2 Systemanforderungen 5 3EinschrankungenÈ 7 4 Software -

A Bibliography of Publications in Byte Magazine: 1990–1994

A Bibliography of Publications in Byte Magazine: 1990{1994 Nelson H. F. Beebe University of Utah Department of Mathematics, 110 LCB 155 S 1400 E RM 233 Salt Lake City, UT 84112-0090 USA Tel: +1 801 581 5254 FAX: +1 801 581 4148 E-mail: [email protected], [email protected], [email protected] (Internet) WWW URL: http://www.math.utah.edu/~beebe/ 05 September 2013 Version 2.12 Title word cross-reference 100 [Ano94-129, Bry93b, HK94]. 100-Mbps [Bry93b]. 100-MHz [Ano94-129, HK94]. 1000 [Ano91u]. 10A [Ano92-73]. 110 [Nad90a]. 1120NX [Ano91e]. 1200C /Views [Api94b]. [Rei93b]. 13-pound [Nad90d]. 144 [Tho93b]. 14th [Ano92-185]. 15-to 040/120 [Ano93-60]. 040/200 [Ano93-60]. [Ano94-89]. 15th [Ano90m]. 16 [Tho90e]. 16-and [Gre94e]. 16-bit 1 [Ano90w, Ano90-51, Ano90a, Ano90-110, [Ano93-48, Ano94-88, Ano94-119, Gla90b, Ano90-113, Ano91-29, Ano93-61, Ano93-130, Sha94b, Tho94b, Wsz90]. 16-Million-Color Ano94a, Del93a, Del93b, Die90b, Far90, [Tho90e]. 16.7 [Ano91-131]. Nan90b, Pep91, Ref94]. 1-2-3 16.7-Million-Color [Ano91-131]. 165c [AR91, Gas93, Ano90-51, Ano90-110, [Tho93a]. 17-ppm [Ano93-92]. 180 Ano90-113, Ano91-29, Ano93-61, Ano94a, [Ano93-93]. 180-MBps [Ano93-93]. 1954 Del93a, Del93b, Die90b, Far90, Pep91]. [Hal94d]. 1954-1994 [Hal94d]. 1990s 1-2-3/G [Ano90-51, Die90b]. 1-megabyte [Cra91k, Lip90b, Osm90, Ras91b, Ras91o, [Tho90d, Ano90a]. 1/2 [Ano92-45]. Tho90f, VC90s, Woo91b]. 1994 [Hal94d]. 1/2-inch [Ano92-45]. 10 [Ano94-165, Nan94b]. 10-Mbps 2 [Ano91-117, Ano91-76, Ano91-131, [Ano94-165, Nan94b]. -

Commodore Devoile L'amiga

ORDINATEUR CREATIF Uorkbtnth 7D1H8 îfjphlcs n» I olhtr nn Hi Quality Version Available on AMIGALAND.COM COMMODORE DEVOILE L'AMIGA 600 Draw-4D Pro - Rapide et convivial ScapeMaker - De TIFF dans vos scènes Vista Mandeltour - A la découverte des fractales Maestro - Une interface audio numérique Professional Cale de Gold Disk 379458403000900450 AVRIL 1992 No. 45 Suisse 9.40 FS, Belgique 219FB, Canada $5.75 Désormais, grâce à GVP. "W TO US 1 / POUVE u / COURIR EN V 500ET EN 286 AVEC LA MÊME RECANE Le HD 500 a définitivement changé les performances de votre bécane. Un disque dur Quantum dernière AUSSI EFFICACE QUE SIMPLE, le HD500 génération et jusqu'à 8 mégas de PAT500 de GVP supporte toutes les de GVP peut RAM apportent suffisamment de res versions de MS-DOS (non fourni) à évoluer vers sources à votre 500 pour satisfaire partir de la V3.2, et donc des milliers les systèmes toutes vos exigences. d'applications PC. Le comportement accélérateurs Aujourd'hui, GVP vous ouvre un logiciel est remarquable : COMBO 68030. nouveau monde : AT500, un émula • émulation des modes graphiques Pensez y avant de teur PC/AT 286 à 16 Mhz assez puis Hercules®, CGA, EGA et VGA choisir une autre sant pour vous ouvrir les fenêtres de monochrome ainsi que T 3 100 sur les marque! WINDOWS® et assez petit pour se écrans standards Commodore. cacher dans le boîtier de votre HD • fonctionnement des applications HD500-52Q OKo : Hi Quality Version Available on AMIGALAND.COM500. Amiga et MS-DOS en multitâche. 4290 Frs TTC. • utilisation de tous les lecteurs de HD500-52Q OKo + AT500 : ENLEVEZ LE CARENAGE DE VOTRE HD500 disquettes connectés à l'Amiga en et enfichez PAT500 dans le mode MS/Dos ou AmigaDOS 6990 Frs TTC. -

Commodore@ Announces 68040 Amiga@ 3000T

Commodore Business Machines Limited 3470 Pharmacy Avenue Agincourt, Ontario M1W 3G3 ( t Commodore· NEWS Tel: (416) 499-4292 For Immediate Release Contact: Tom Shepherd September 8, 1992 Director of Marketing (416) 499-4292 COMMODORE@ ANNOUNCES 68040 AMIGA@ 3000T AGIN COURT, ONTARIO -- Commodore Business Machines Ltd. today announced a new version of the Amiga 3000T multimedia workstation powered by a 25MHz Motorola@ 68040 processor, making it the most expandable and powerful Amiga currently available. The Manufacturer's Suggested Retail Price is $6,895.00 including a monitor. Units should be available in mid September 1992 at Commodore authorized reseller locations. The Amiga 3000T-040/200 features the Motorola 68040 processor with an integrated math co 0 processor and provides approximately 20 CISC MIPS and 3.5 DP Megaflops. The 68040 equipped A3000T features throughput that equals or surpasses other similarly equipped Motorola 68040 or Intel® 486-based machines. The unit includes AmigaDOS™ 2.0 and comes standard with a 200MB hard disk drive, a 3.5" floppy disk drive, 5MB of RAM (expandable to 18MB), and 32 bit bus architecture. "The Amiga 3000T is ideal for the demanding needs of the professional multimedia developer involved in videographics, dynamic presentations, interactive training or point-of-sale kiosks," said Commodore Director of Marketing Tom Shepherd. "The great speed and expandability of the system, combined with the system's ability* to connect to a Novell® network and share information with MACs and PCs, make it the logical choice for use as a multimedia development workstation." --- more --- ... Commodore® Announces 68040 Amiga® 3000T - Page 2 Commodore International Limited, through its operating subsidiaries around the world, manufactures and markets personal computers to customers in the professional, government, education and consu~er market sectors. -

Concierto the Picasso IV Sound Module

Concierto The Picasso IV sound module Manual 18 August 1997 Copyright c 1997 Village Tronic Marketing GmbH MuhlenstraûeÈ 2 31157 Sarstedt Germany Technical Hotline: Tel. +49 (0)5066 / 7013-10 FAX: Tel. +49 (0)5066 / 7013-49 Legal information The publication at hand is protected by copyright. All rights reserved. No part of this book must be reproduced in any way by means of photo copies, micro ®ches, text ®les or other procedures or be translated into a language suitable for machines, particularly data processing systems, without the written consent of Village Tronic Marketing GmbH. Translation into other languages will also require the written consent of Village Tronic Marketing GmbH. Text, illustrations and programs were created with extreme care. However, Village Tronic Marketing GmbH cannot be held responsible legally for any faulty statements that have gone unnoticed, and results thereof, nor take any liability whatsoever. Also, Village Tronic Marketing GmbH does not accept any liability for damages that are directly or indirectly related to using the Concierto. Within the text, trademarks are not marked speci®cally. Hardware: Paul Jordan, Frank Otto Software: Olaf Barthel Manual: Olaf Barthel Contents 1 Features of the Concierto 3 : : : : : : : : : : : : : : : : : : : : : : : : : : : : : 1.1 Digital sound : 3 : : : : : : : : : : : : : : : : : : : : : : : : : : 1.2 Synthesized sound : 3 : : : : : : : : : : : : : : : : : : : : : : : : : : : : : 1.3 Sound mixer : 3 : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : : -

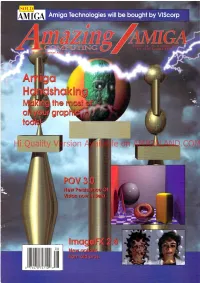

Hi Quality Version Available on AMIGALAND.COM

Hi Quality Version Available on AMIGALAND.COM j \ b w Vbion no'j 07447074710908 QUALITY Q E M S S S W I ^ " UIKPAK 1000 Forge Avenue, Norristown, Pennsylvania 19403 Plwne 610-666-8080 FAX 610-666-8086 To: Amazing Computing/Amiga Readers From: David A, Ziembicki CEO-QuikPak Corporation Re: Amiga Update There is progress on all fronts. Shipment of A1200s is on schedule and will begin in early July. Interest in this product is quite strong and we look forward to a successful relaunch of the A1200 and expect this computer to become a recognized Internet access solution. We are evaluating modems, browser software, and ISP's and expect to make an announcement of alliances for these items around the time of A1200 shipment to dealers. Hi Quality Version Available on AMIGALAND.COMAccording to our sources, the VIScorp agreement is proceeding to final conclusion and we have been working with VIScorp on strategies for some future products in the Amiga family. Although it may not always be obvious to the Amiga community at large, VIScorp is using their resources to coordinate the efforts of all to rebuild the Amiga in North America and stabilize the market here as well as keeping an eye on the future. There is also heightened activity with all of the third party developers. We are aware of many proposed upgrades to existing products as well as several new products on the drawing board now which should be completed and shipping in the fall. We are encouraged by all of the positive efforts of these developers and we are using our best efforts to support these activities.