The IAS Computer Family Scrapbook

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PL/I List Processing • PL/I Language Lacked Facili�Es for Trea�Ng Linked Lists HAROLD LAWSON,JR

The Birth of the Pointer Variable Based upon: Experiences and Reflec;ons of a Computer Pioneer Harold “Bud” Lawson FELLOW FELLOW and LIFE MEMBER IEEE COMPUTER SOCIETY CHARLES BABBAGE COMPUTER PIONEER FELLOW Overlapping Phases • Phase 1 (1959-1974) – Computer Industry • Phase 2 (1974-1996) - Computer-Based Systems • Phase 3 (1996-Present) – Complex Systems • Dedicated to all the talented colleagues that I have worked with during my career. • We have had fun and learned from each other. • InteresMng ReflecMons and Happenings are indicated in Red. Computer Industry (1959 to 1974) • Summer 1958 - US Census Bureau • 1959 Temple University (Introduc;on to IBM 650 (Drum Machine)) • 1959-61 Employed at Remington-Rand Univac • 1961-67 Employed at IBM • 1967-69 Part Time Consultant (Professor) • 1969-70 Employed at Standard Computer Corporaon • 1971-73 Consultant to Datasaab, Linköping • 1973-… Consultant .. Expert Witness.. Rear Admiral Dr. Grace Murray Hopper (December 9, 1906 – January 1, 1992) Minted the word “BUG” – During her Mme as Programmer of the MARK I Computer at Harvard Minted the word “COMPILER” with A-0 in 1951 Developed Math-MaMc and FlowmaMc and inspired the Development of COBOL Grace loved US Navy Service – The oldest acMve officer, reMrement at 80. From Grace I learned that it is important to queson the status-quo, to seek deeper meaning and explore alterna5ve ways of doing things. 1980 – Honarary Doctor The USS Linköpings Universitet Hopper Univac Compiler Technology of the 1950’s Grace Hopper’s Early Programming Languages Math-MaMc -

A Politico-Social History of Algolt (With a Chronology in the Form of a Log Book)

A Politico-Social History of Algolt (With a Chronology in the Form of a Log Book) R. w. BEMER Introduction This is an admittedly fragmentary chronicle of events in the develop ment of the algorithmic language ALGOL. Nevertheless, it seems perti nent, while we await the advent of a technical and conceptual history, to outline the matrix of forces which shaped that history in a political and social sense. Perhaps the author's role is only that of recorder of visible events, rather than the complex interplay of ideas which have made ALGOL the force it is in the computational world. It is true, as Professor Ershov stated in his review of a draft of the present work, that "the reading of this history, rich in curious details, nevertheless does not enable the beginner to understand why ALGOL, with a history that would seem more disappointing than triumphant, changed the face of current programming". I can only state that the time scale and my own lesser competence do not allow the tracing of conceptual development in requisite detail. Books are sure to follow in this area, particularly one by Knuth. A further defect in the present work is the relatively lesser availability of European input to the log, although I could claim better access than many in the U.S.A. This is regrettable in view of the relatively stronger support given to ALGOL in Europe. Perhaps this calmer acceptance had the effect of reducing the number of significant entries for a log such as this. Following a brief view of the pattern of events come the entries of the chronology, or log, numbered for reference in the text. -

Early Stored Program Computers

Stored Program Computers Thomas J. Bergin Computing History Museum American University 7/9/2012 1 Early Thoughts about Stored Programming • January 1944 Moore School team thinks of better ways to do things; leverages delay line memories from War research • September 1944 John von Neumann visits project – Goldstine’s meeting at Aberdeen Train Station • October 1944 Army extends the ENIAC contract research on EDVAC stored-program concept • Spring 1945 ENIAC working well • June 1945 First Draft of a Report on the EDVAC 7/9/2012 2 First Draft Report (June 1945) • John von Neumann prepares (?) a report on the EDVAC which identifies how the machine could be programmed (unfinished very rough draft) – academic: publish for the good of science – engineers: patents, patents, patents • von Neumann never repudiates the myth that he wrote it; most members of the ENIAC team contribute ideas; Goldstine note about “bashing” summer7/9/2012 letters together 3 • 1.0 Definitions – The considerations which follow deal with the structure of a very high speed automatic digital computing system, and in particular with its logical control…. – The instructions which govern this operation must be given to the device in absolutely exhaustive detail. They include all numerical information which is required to solve the problem…. – Once these instructions are given to the device, it must be be able to carry them out completely and without any need for further intelligent human intervention…. • 2.0 Main Subdivision of the System – First: since the device is a computor, it will have to perform the elementary operations of arithmetics…. – Second: the logical control of the device is the proper sequencing of its operations (by…a control organ. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

Ucla Computer Science Depart "Tment

THE UCLA COMPUTER SCIENCE DEPART"TMENT QUARTERLY THE DEPARTMENT AND ITS PEOPLE FALL 1987/WINTER 1988 VOL. 16 NO. 1 SCHOOL OF ENGINEERING AND APPLIED SCIENCE COMPUTER SCIENCE DEPARTMENT OFFICERS Dr. Gerald Estrin, Chair Dr. Jack W. Carlyle, Vice Chair, Planning & Resources Dr. Sheila Greibach, Vice Chair, Graduate Affairs Dr. Lawrence McNamee, Vice Chair, Undergraduate Affairs Mrs. Arlene C. Weber, Management Services Officer Room 3713 Boelter Hall QUARTERLY STAFF Dr. Sheila Greibach, Editor Ms. Marta Cervantes, Coordinator Material in this publication may not be reproduced without written permission of the Computer Science Department. Subscriptions to this publication are available at $20.00/year (three issues) by contacting Ms. Brenda Ramsey, UCLA Computer Science Department, 3713 Boelter Hall, Los Angeles, CA 90024-1596. THE UCLA COMPUTER SCIENCE DEPARTMENT QUARTERLY The Computer Science Department And Its People Fall Quarter 1987/Winter Quarter 1988 Vol. 16, No. 1 SCHOOL OF ENGINEERING AND APPLIED SCIENCE UNIVERSITY OF CALIFORNIA, LOS ANGELES Fall-Winfer CSD Quarterly CONTENTS COMPUTER SCIENCE AT UCLA AND COMPUTER SCIENCE IN THE UNITED STATES GeraldEstrin, Chair...................................................................................................... I THE UNIVERSITY CONTEXT .............................................................................................. 13 THE UCLA COMPUTER SCIENCE DEPARTMENT The Faculty A rane nf;ntraract Biographies ............................................................................................................................. -

Id Question Microprocessor Is the Example of ___Architecture. A

Id Question Microprocessor is the example of _______ architecture. A Princeton B Von Neumann C Rockwell D Harvard Answer A Marks 1 Unit 1 Id Question _______ bus is unidirectional. A Data B Address C Control D None of these Answer B Marks 1 Unit 1 Id Question Use of _______isolates CPU form frequent accesses to main memory. A Local I/O controller B Expansion bus interface C Cache structure D System bus Answer C Marks 1 Unit 1 Id Question _______ buffers data transfer between system bus and I/O controllers on expansion bus. A Local I/O controller B Expansion bus interface C Cache structure D None of these Answer B Marks 1 Unit 1 Id Question ______ Timing involves a clock line. A Synchronous B Asynchronous C Asymmetric D None of these Answer A Marks 1 Unit 1 Id Question -----timing takes advantage of mixture of slow and fast devices, sharing the same bus A Synchronous B asynchronous C Asymmetric D None of these Answer B Marks 1 Unit 1 Id st Question In 1 generation _____language was used to prepare programs. A Machine B Assembly C High level programming D Pseudo code Answer B Marks 1 Unit 1 Id Question The transistor was invented at ________ laboratories. A AT &T B AT &Y C AM &T D AT &M Answer A Marks 1 Unit 1 Id Question ______is used to control various modules in the system A Control Bus B Data Bus C Address Bus D All of these Answer A Marks 1 Unit 1 Id Question The disadvantage of single bus structure over multi bus structure is _____ A Propagation delay B Bottle neck because of bus capacity C Both A and B D Neither A nor B Answer C Marks 1 Unit 1 Id Question _____ provide path for moving data among system modules A Control Bus B Data Bus C Address Bus D All of these Answer B Marks 1 Unit 1 Id Question Microcontroller is the example of _____ architecture. -

The 1-Bit Instrument: the Fundamentals of 1-Bit Synthesis

BLAKE TROISE The 1-Bit Instrument The Fundamentals of 1-Bit Synthesis, Their Implementational Implications, and Instrumental Possibilities ABSTRACT The 1-bit sonic environment (perhaps most famously musically employed on the ZX Spectrum) is defined by extreme limitation. Yet, belying these restrictions, there is a surprisingly expressive instrumental versatility. This article explores the theory behind the primary, idiosyncratically 1-bit techniques available to the composer-programmer, those that are essential when designing “instruments” in 1-bit environments. These techniques include pulse width modulation for timbral manipulation and means of generating virtual polyph- ony in software, such as the pin pulse and pulse interleaving techniques. These methodologies are considered in respect to their compositional implications and instrumental applications. KEYWORDS chiptune, 1-bit, one-bit, ZX Spectrum, pulse pin method, pulse interleaving, timbre, polyphony, history 2020 18 May on guest by http://online.ucpress.edu/jsmg/article-pdf/1/1/44/378624/jsmg_1_1_44.pdf from Downloaded INTRODUCTION As unquestionably evident from the chipmusic scene, it is an understatement to say that there is a lot one can do with simple square waves. One-bit music, generally considered a subdivision of chipmusic,1 takes this one step further: it is the music of a single square wave. The only operation possible in a -bit environment is the variation of amplitude over time, where amplitude is quantized to two states: high or low, on or off. As such, it may seem in- tuitively impossible to achieve traditionally simple musical operations such as polyphony and dynamic control within a -bit environment. Despite these restrictions, the unique tech- niques and auditory tricks of contemporary -bit practice exploit the limits of human per- ception. -

The History of Computer Language Selection

The History of Computer Language Selection Kevin R. Parker College of Business, Idaho State University, Pocatello, Idaho USA [email protected] Bill Davey School of Business Information Technology, RMIT University, Melbourne, Australia [email protected] Abstract: This examines the history of computer language choice for both industry use and university programming courses. The study considers events in two developed countries and reveals themes that may be common in the language selection history of other developed nations. History shows a set of recurring problems for those involved in choosing languages. This study shows that those involved in the selection process can be informed by history when making those decisions. Keywords: selection of programming languages, pragmatic approach to selection, pedagogical approach to selection. 1. Introduction The history of computing is often expressed in terms of significant hardware developments. Both the United States and Australia made early contributions in computing. Many trace the dawn of the history of programmable computers to Eckert and Mauchly’s departure from the ENIAC project to start the Eckert-Mauchly Computer Corporation. In Australia, the history of programmable computers starts with CSIRAC, the fourth programmable computer in the world that ran its first test program in 1949. This computer, manufactured by the government science organization (CSIRO), was used into the 1960s as a working machine at the University of Melbourne and still exists as a complete unit at the Museum of Victoria in Melbourne. Australia’s early entry into computing makes a comparison with the United States interesting. These early computers needed programmers, that is, people with the expertise to convert a problem into a mathematical representation directly executable by the computer. -

The Legacy of Victor R. Basili

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange About Harlan D. Mills Science Alliance 2005 Foundations of Empirical Software Engineering: The Legacy of Victor R. Basili Barry Boehm Hans Dieter Rombach Marvin V. Zelkowitz Follow this and additional works at: https://trace.tennessee.edu/utk_harlanabout Part of the Physical Sciences and Mathematics Commons Recommended Citation Boehm, Barry; Rombach, Hans Dieter; and Zelkowitz, Marvin V., "Foundations of Empirical Software Engineering: The Legacy of Victor R. Basili" (2005). About Harlan D. Mills. https://trace.tennessee.edu/utk_harlanabout/3 This Book is brought to you for free and open access by the Science Alliance at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in About Harlan D. Mills by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange The Harlan D. Mills Collection Science Alliance 1-1-2005 Foundations of Empirical Software Engineering: The Legacy of Victor R.Basili Barry Boehm Hans Dieter Rombach Marvin V. Zelkowitz Recommended Citation Boehm, Barry; Rombach, Hans Dieter; and Zelkowitz, Marvin V., "Foundations of Empirical Software Engineering: The Legacy of Victor R.Basili" (2005). The Harlan D. Mills Collection. http://trace.tennessee.edu/utk_harlan/36 This Book is brought to you for free and open access by the Science Alliance at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in The Harlan D. Mills Collection by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. -

10, June 5, 1981 ------The Address of the ASC Is: 2131 G St

Newsletter of the American Society for Cybernetics I Roger Conant. Editor ~ 1108 SEO. UICC Box 4348 11" Chicago.IL 60680 312+996-2308 Number 10, June 5, 1981 ----------------------------------------------------------------------- The address of the ASC is: 2131 G St. N.W., Washington DC 20052. ----------------------------------------------------------------------- THE NEW C~BERNETICS ASC Annual Meeting Finally, we hope to keep the registration Marvin Center, George Washington University fee as low as possible. However, due to October 30 - November 3, 1981 the difficulty in planning space require Program Chairperson - Larry Richards ments at the Marvin Center we urge you to register as soon as possible and will pro vide a discount for those who submit their The program for the first annual meeting registration materials at least one month of the ASC in a number of years is now in advance of the meeting. If you have being finalized. You should receive a any suggestions for enhancing the quality program announcement and registration form of our society's first major conference, semetime in July. Due to unanticipated, or if you have any questions, please feel but extremely encouraging, interest in free to contact me. participating in the conference, we may extend its length to four days as opposed Dr. Laurence D. Richards to the original plan of thr ~ e days. Department of Administrative Science Colby College The program is shaping up to be indeed Waterville,Maine 04901 very exciting, with such well known per phone: 207/873-1131x587 sonalitis as Heinz von Foerster, Ernst von Glasersfeld, Lars LÖfgren, Russell Ackoff, Lillian Schwartz, Paul Rubinyi, Gerrit Broekstra, Klaus Krippendorff, Robert Lilienfeld, Herbert BrÜn, and Roberto Canete already agreeing to participate in various ways. -

Computer Development at the National Bureau of Standards

Computer Development at the National Bureau of Standards The first fully operational stored-program electronic individual computations could be performed at elec- computer in the United States was built at the National tronic speed, but the instructions (the program) that Bureau of Standards. The Standards Electronic drove these computations could not be modified and Automatic Computer (SEAC) [1] (Fig. 1.) began useful sequenced at the same electronic speed as the computa- computation in May 1950. The stored program was held tions. Other early computers in academia, government, in the machine’s internal memory where the machine and industry, such as Edvac, Ordvac, Illiac I, the Von itself could modify it for successive stages of a compu- Neumann IAS computer, and the IBM 701, would not tation. This made a dramatic increase in the power of begin productive operation until 1952. programming. In 1947, the U.S. Bureau of the Census, in coopera- Although originally intended as an “interim” com- tion with the Departments of the Army and Air Force, puter, SEAC had a productive life of 14 years, with a decided to contract with Eckert and Mauchly, who had profound effect on all U.S. Government computing, the developed the ENIAC, to create a computer that extension of the use of computers into previously would have an internally stored program which unknown applications, and the further development of could be run at electronic speeds. Because of a demon- computing machines in industry and academia. strated competence in designing electronic components, In earlier developments, the possibility of doing the National Bureau of Standards was asked to be electronic computation had been demonstrated by technical monitor of the contract that was issued, Atanasoff at Iowa State University in 1937. -

The State of Digital Computer Technology in Europe, 1961

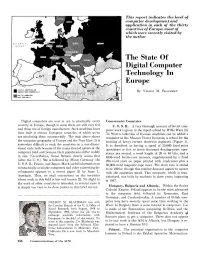

This report indicates the level of computer development and application in each of the thirty countries of Europe, most of which were recently visited by the author The State Of Digital Computer Technology In Europe By NELSON M. BLACHMAN Digital computers are now in use in practically every Communist Countries country in Europe, though in some there are still very few U. S. S.R. A very thorough account of Soviet com- and these are of foreign manufacture. Such machines have puter work is given in the report edited by Willis Ware [3]. been built in sixteen European countries, of which seven To Ware's collection of Russian machines can be added a are producing them commercially. The map above shows computer at the Moscow Power Institute, a school for the the computer geography of Europe and the Near East. It is training of heavy-current electrical engineers (Figure 1). somewhat difficult to rank the countries on a one-dimen- It is described as having a speed of 25,000 fixed-point sional scale both because of the many-faceted nature of the operations or five to seven thousand floating-point oper- computer field and because their populations differ widely ations per second, a word length of 20 or 40 bits, and a in size. Nevertheh~ss, Great Britain clearly comes first 4096-word ferrite-core memory, supplemented by a fixed (after the U. S.). She is followed by (West) Germany, the 256-word store on paper printed with condensers plus a U. S. S. R., France, and Japan. Much useful information on 50,000-word magnetic-tape store.