Pinned Photodiode CMOS Image Sensortcad

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Photodiode and LIGHT EMITTING DIODE

Photodiode and LIGHT EMITTING DIODE Presentation by JASWANT KUMAR ROLL NO.-12 rd IT(3 SEM.) 1 About LEDs (1/2) • A light emitting diode (LED) is essentially a PN junction opto- semiconductor that emits a monochromatic (single color) light when operated in a forward biased direction. • LEDs convert electrical energy into light energy. LED SYMBOL 2 ABOUT LEDS (2/2) • The most important part of a light emitting diode (LED) is the semi-conductor chip located in the center of the bulb as shown at the right. • The chip has two regions separated by a junction. • The junction acts as a barrier to the flow of electrons between the p and the n regions. 3 LED CIRCUIT • In electronics, the basic LED circuit is an electric power circuit used to power a light-emitting diode or LED. The simplest such circuit consists of a voltage source and two components connect in series: a current-limiting resistor (sometimes called the ballast resistor), and an LED. Optionally, a switch may be introduced to open and close the circuit. The switch may be replaced with another component or circuit to form a continuity tester. 4 HOW DOES A LED WORK? • Each time an electron recombines with a positive charge, electric potential energy is converted into electromagnetic energy. • For each recombination of a negative and a positive charge, a quantum of electromagnetic energy is emitted in the form of a photon of light with a frequency characteristic of the semi- conductor material. 5 Mechanism behind photon emission in LEDs? MechanismMechanism isis “injection“injection Electroluminescence”.Electroluminescence”. -

Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits

Sensors and Materials, Vol. 13, No. 4 (2001) 189-206 MYUTokyo S &M0442 Integrated High-Speed, High-Sensitivity Photodiodes and Optoelectronic Integrated Circuits Horst Zimmermann Institut fiirElektrische Mess- und Schaltungstechnik, Technische Universitat Wien, Gusshausstrasse, A-1040 Wien, Austria (Received February 28, 2000; accepted February3, 2001) Key words: integrated circuits, integrated optoelectronics, optical receivers, optoelectronic de vices, PIN photodiode, double photodiode, silicon A review of the properties of photodiodes available through the use of standard silicon technologies is presented and some examples of how to improve monolithically integrated photodiodes are shown. The application of these photodiodes in optoelectronic integrated circuits (OEICs) is described. An innovative double photodiode requiring no process modificationsin complementary metal-oxide sem!conductor (CMOS) and bipolar CMOS (BiCMOS) technologies achieves a bandwidth in excess of 360 MHzand data rates exceeding 622 Mb/s. Furthermore, a new PIN photodiode requiring only one additional mask for the integration in a CMOS process is capable of handling a data rate of 1.1 Gb/s. Antireflection coating improves the quantum efficiencyof integrated photodiodes to values of more than 90%. Integrated optical receivers for data communication achieve a high bandwidth and a high sensitivity. Furthermore, an OEIC for application in optical storage systems is introduced. Author's e-mail address: [email protected] 189 l 90 Sensors and Materials, Vol. 13, No. 4 (2001) 1. Introduction Photons with an energy larger than the band gap generate electron-hole pairs in semiconductors. This photogeneration G obeys an exponential law: aP,0 G( x) = -- exp( -ax), Ahv (1) where xis the penetration depth coordinate, P0 is the nonreflectedportion of the incident optical power, A is the light-sensitive area of a photodiode, hv is the energy of the photon, and a is the wavelength-dependent absorption coefficient. -

Leds As Single-Photon Avalanche Photodiodes by Jonathan Newport, American University

LEDs as Single-Photon Avalanche Photodiodes by Jonathan Newport, American University Lab Objectives: Use a photon detector to illustrate properties of random counting experiments. Use limiting probability distributions to perform statistical analysis on a physical system. Plot histograms. Condition a detector’s signal for further electronic processing. Use a breadboard, power supply and oscilloscope to construct a circuit and make measurements. Learn about semiconductor device physics. Reading: Taylor 3.2 – The Square-Root Rule for a Counting Experiment pp. 48-49 Taylor 5.1-5.3 – Histograms and the Normal Distribution pp. 121-135 Taylor Ch. 11 – The Poisson Distribution pp. 245-254 Taylor Problem 5.6 – The Exponential Distribution p. 155 Experiment #1: Lighting an LED A Light-Emitting Diode is a non-linear circuit element that can produce a controlled amount of light. The AND113R datasheet shows that the luminous intensity is proportional to the current flowing through the LED. As illustrated in the IV curve shown below, the current flowing through the diode is in turn proportional to the voltage across the diode. Diodes behave like a one-way valve for current. When the voltage on the Anode is more positive than the voltage on the Cathode, then the diode is said to be in Forward Bias. As the voltage across the diode increases, the current through the diode increases dramatically. The heat generated by this current can easily destroy the device. It is therefore wise to install a current-limiting resistor in series with the diode to prevent thermal runaway. When the voltage on the Cathode is more positive than the voltage on the Anode, the diode is said to be in Reverse Bias. -

Bipolar Junction Transistor As a Detector for Measuring in Diagnostic X-Ray Beams

2013 International Nuclear Atlantic Conference - INAC 2013 Recife, PE, Brazil, November 24-29, 2013 ASSOCIAÇÃO BRASILEIRA DE ENERGIA NUCLEAR - ABEN ISBN: 978-85-99141-05-2 BIPOLAR JUNCTION TRANSISTOR AS A DETECTOR FOR MEASURING IN DIAGNOSTIC X-RAY BEAMS Francisco A. Cavalcanti1,2, David S. Monte1,2, Aline N. Alves1,2, Fábio R. Barros2, Marcus A. P. Santos2, and Luiz A. P. Santos1,2 1 Departamento de Energia Nuclear Universidade Federal de Pernambuco Av. Prof. Luiz Freire, 1000 50740-540 Recife, PE [email protected] 2 Centro Regional de Ciências Nucleares do Nordeste (CRCN-NE / CNEN) Av. Prof. Luiz Freire, 1 50740-540 Recife, PE [email protected] ABSTRACT Photodiode and phototransistor are the most frequently used devices for measuring ionizing radiation in medical applications. The cited devices have the operating principle well known, however the bipolar junction transistor (BJT) is not a typical device used as a detector for measuring some physical quantities for diagnostic radiation. In fact, a photodiode, for example, has an area about 10 mm square and a BJT has an area which can be more than 10 thousands times smaller. The purpose of this paper is to bring a new technique to estimate some physical quantities or parameters in diagnostic radiation; for example, peak kilovoltage (kVp), deep dose measurements. The methodology for each type of evaluation depends on the energy range of the radiation and the physical quantity or parameter to be measured. Actually, some characteristics of the incident radiation under the device can be correlated with the readout signal, which is a function of the electrical currents in the electrodes of the BJT: Collector, Base and Emitter. -

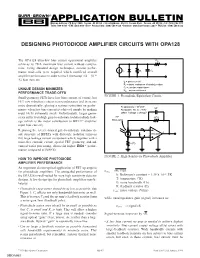

Designing Photodiode Amplifier Circuits with Opa128

® DESIGNING PHOTODIODE AMPLIFIER CIRCUITS WITH OPA128 The OPA128 ultra-low bias current operational amplifier RS achieves its 75fA maximum bias current without compro- mise. Using standard design techniques, serious perfor- I R C mance trade-offs were required which sacrificed overall P J J amplifier performance in order to reach femtoamp (fA = 10–15 A) bias currents. IP = photocurrent RJ = shunt resistance of diode junction CJ = junction capacitance UNIQUE DESIGN MINIMIZES R = series resistance PERFORMANCE TRADE-OFFS S FIGURE 1. Photodiode Equivalent Circuit. Small-geometry FETs have low bias current, of course, but FET size reduction reduces transconductance and increases noise dramatically, placing a serious restriction on perfor- Responsivity ≈ 109V/W 5pF mance when low bias current is achieved simply by making Bandwidth: DC to ≈ 30Hz input FETs extremely small. Unfortunately, larger geom- Offset Voltage ≈ ±485µV etries suffer from high gate-to-substrate isolation diode leak- HP 109Ω age (which is the major contribution to BIFET® amplifier 5082-4204 input bias current). Replacing the reverse-biased gate-to-substrate isolation di- 2 6 OPA128LM ode structure of BlFETs with dielectric isolation removes 3 this large leakage current component which, together with a 8 noise-free cascode circuit, special FET geometry, and ad- 109Ω vanced wafer processing, allows far higher Difet ® perfor- mance compared to BIFETs. FIGURE 2. High-Sensitivity Photodiode Amplifier. HOW TO IMPROVE PHOTODIODE AMPLIFIER PERFORMANCE An important electro-optical application of FET op amps is √ for photodiode amplifiers. The unequaled performance of eOUT = 4k TBR the OPA128 is well-suited for very high sensitivity detector k: Boltzman’s constant = 1.38 x 10–23 J/K ° designs. -

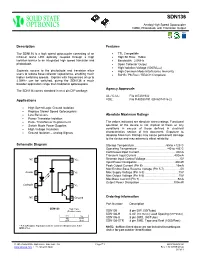

SDN136 Analog High Speed Optocoupler 1Mbd, Photodiode with Transistor Output

SDN136 Analog High Speed Optocoupler 1MBd, Photodiode with Transistor Output Description Features The SDN136 is a high speed optocoupler consisting of an TTL Compatible infrared GaAs LED optically coupled through a high High Bit Rate: 1Mb/s isolation barrier to an integrated high speed transistor and Bandwidth: 2.0MHz photodiode. Open Collector Output High Isolation Voltage (5000VRMS) Separate access to the photodiode and transistor allow High Common Mode Interference Immunity users to reduce base-collector capacitance, enabling much RoHS / Pb-Free / REACH Compliant higher switching speeds. Signals with frequencies of up to 2.0MHz can be switched, giving the SDN136 a much broader application range than traditional optocouplers. Agency Approvals The SDN136 comes standard in an 8 pin DIP package. UL / C-UL: File # E201932 Applications VDE: File # 40035191 (EN 60747-5-2) High Speed Logic Ground Isolation Replace Slower Speed Optocouplers Absolute Maximum Ratings Line Receivers Power Transistor Isolation Pulse Transformer Replacement The values indicated are absolute stress ratings. Functional Switch Mode Power Supplies operation of the device is not implied at these or any High Voltage Insulation conditions in excess of those defined in electrical Ground Isolation – Analog Signals characteristics section of this document. Exposure to absolute Maximum Ratings may cause permanent damage to the device and may adversely affect reliability. Schematic Diagram Storage Temperature …………………………..-55 to +125°C Operating Temperature …………………………-40 -

Photovoltaic Couplers for MOSFET Drive for Relays

Photocoupler Application Notes Basic Electrical Characteristics and Application Circuit Design of Photovoltaic Couplers for MOSFET Drive for Relays Outline: Photovoltaic-output photocouplers(photovoltaic couplers), which incorporate a photodiode array as an output device, are commonly used in combination with a discrete MOSFET(s) to form a semiconductor relay. This application note discusses the electrical characteristics and application circuits of photovoltaic-output photocouplers. ©2019 1 Rev. 1.0 2019-04-25 Toshiba Electronic Devices & Storage Corporation Photocoupler Application Notes Table of Contents 1. What is a photovoltaic-output photocoupler? ............................................................ 3 1.1 Structure of a photovoltaic-output photocoupler .................................................... 3 1.2 Principle of operation of a photovoltaic-output photocoupler .................................... 3 1.3 Basic usage of photovoltaic-output photocouplers .................................................. 4 1.4 Advantages of PV+MOSFET combinations ............................................................. 5 1.5 Types of photovoltaic-output photocouplers .......................................................... 7 2. Major electrical characteristics and behavior of photovoltaic-output photocouplers ........ 8 2.1 VOC-IF characteristics .......................................................................................... 9 2.2 VOC-Ta characteristic ........................................................................................ -

(PPS) • CMOS Photodiode Active Pixel Sensor (APS) • Photoga

Lecture Notes 4 CMOS Image Sensors CMOS Passive Pixel Sensor (PPS) • Basic operation ◦ Charge to output voltage transfer function ◦ Readout speed ◦ CMOS Photodiode Active Pixel Sensor (APS) • Basic operation ◦ Charge to output voltage transfer function ◦ Readout speed ◦ Photogate and Pinned Diode APS • Multiplexed APS • EE 392B: CMOS Image Sensors 4-1 Introduction CMOS image sensors are fabricated in \standard" CMOS technologies • Their main advantage over CCDs is the ability to integrate analog and • digital circuits with the sensor Less chips used in imaging system ◦ Lower power dissipation ◦ Faster readout speeds ◦ More programmability ◦ New functionalities (high dynamic range, biometric, etc) ◦ But they generally have lower perofrmance than CCDs: • Standard CMOS technologies are not optimized for imaging ◦ More circuits result in more noise and fixed pattern noise ◦ In this lecture notes we discuss various CMOS imager architectures • In the following lecture notes we discuss fabrication and layout issues • EE 392B: CMOS Image Sensors 4-2 CMOS Image Sensor Architecture Word Pixel: Row Decoder Photodetector & Readout treansistors Bit Column Amplifiers/Caps Output Column Mux Readout performed by transferring one row at a time to the column • storage capacitors, then reading out the row, one (or more) pixel at a time, using the column decoder and multiplexer In many CMOS image sensor architectures, row integration times are • staggerred by the row/column readout time (scrolling shutter) EE 392B: CMOS Image Sensors 4-3 CMOS Image Sensor -

Overview of Camera Systems Used in Beam Instrumentation

Beata Walasek-Höhne verview of Video Cameras used in Beam Instrumentation FAIR GmbH | GSI GmbH Outline: Taking an Image . Source of light more details: talk of E. Bravin „Transverse Profile measurements“ . Optics more details: talk of S. Gibson „Introduction to optics“ . Image sensors . Analog i. Video Tube . Solid state sensors i. CCD ii. CMOS iii. CID . Radiation hardness . Digitizer more details: talk of M. Gasior „Analog Digital Conversion“ . Post processing FAIR GmbH | GSI GmbH 2 Source of light . light is represented as both a particle (photon) and electromagnetic wave . photons have a defined energy . energy correlates to wavelength 풉풄 푬 = 흀 . wavelength corresponds to color . number of the photons corresponds to intensity . visible light is a very narrow band in the electromagnetic spectrum FAIR GmbH | GSI GmbH 3 Source of light 600mbar Kr 600mbar Kr © GSI, www.gsi.de Ruby-Ceramics (Chromox) screen at LHC for injection and first turn, protons at 450 GeV © CERN, www.cern.ch YAG:Ce at FLASH © DESY, www.desy.de FAIR GmbH | GSI GmbH 4 Source of light 600mbar Kr 100 mm © GSI, www.gsi.de FAIR GmbH | GSI GmbH 5 Analog Video Cameras © Pete Simpkin, Marconi vidicon Camera www.bbceng.info FAIR GmbH | GSI GmbH 6 Analog Video Cameras . early 1900s first experiment in image transmission . in 1930s new electronic designs based on a cathode-ray video camera tube, including two versions dissector tube (Philo Farnsworth) and iconoscope (Vladimir Zsworykin) Dissector tube © Television News magazine, 1931 FAIR GmbH | GSI GmbH 7 Analog Video Cameras . analog system became the standard in the television industry and remained in wide use until the 1980s Iconoscope © Radio News magazine, 1945 FAIR GmbH | GSI GmbH 8 Analog Video Cameras: Vidicon . -

Amplified Photodetector User's Guide

AMPLIFIED PHOTODETECTOR USER’S GUIDE Thank you for purchasing your Amplified Photodetector. This user’s guide will help answer any questions you may have regarding the safe use and optimal operation of your Amplified Photodetector. TABLE OF CONTENTS I. Amplified Photodetector Overview ................................................................................................................. 1 II. Operation of your Amplified Photodetector .................................................................................................... 1 III. Troubleshooting ............................................................................................................................................... 2 IV. Drawings: Amplified Photodetectors .............................................................................................................. 2 V. Specifications: Amplified Photodetectors ....................................................................................................... 3 VI. Schematics: Amplified Photodetectors ............................................................................................................ 3 VII. Glossary of Terms .......................................................................................................................................... 4 I. Amplified Photodetector Overview The Amplified Photodetectors contain PIN photodiodes that utilize the photovoltaic effect to convert optical power into an electrical current. Figure 1 below identifies the main elements of -

Photodiode Arbind Kumar Mallik Department of Physics, Tribhuwan Multiple Campus, Palpa, Nepal [email protected]

Photodiode Arbind Kumar Mallik Department of Physics, Tribhuwan Multiple Campus, Palpa, Nepal [email protected] Abstract:- Light detection is important for many types of electronic instruments. One of the most important of these light detecting tools is the photodiode. These tools are present in dozens of electronic devices. Photodiodes are semi-conductors that convert light into electrical voltage. This turns light signals into electrical input instructions that the machine can understand. Infect photodiodes are optoelectronic devices, meaning that they create electricity when light shines on them, similar to photovoltaic cells. In this article a brief about photodiodes are discussed. Keywords:- photodiode, semiconductor, valence band, depletion region, p-n photodiode, p-i-n photodiode, quantum efficiency, dark current, photovoltaic mode, photoconductive mode. 1. INTRODUCTION LED with anode and cathode leads projecting out In semiconductors, electrons are released from from the case. But a photodiode is the exact opposite the valence band, when energy is supplied to such of an LED in function. Instead of emitting light, the electrons. This energy can be supplied in the form photodiode absorbs light and produces current. A of heat or through an accelerating voltage. Light photodiode and its symbol are shown in fig-1(a) and energy can also be used to produce the current in fig-1(b) respectively. semiconductors. A junction diode made from light (or photo) sensitive semiconductor is called a photodiode. Photodiode technology developments came out of the basic developments of the PN junction diode that started in the 1940s in earnest. Applications for the use of the PN junction diode were found outside the basic use of rectifying signals. -

A Graphene/Polycrystalline Silicon Photodiode and Its Integration in a Photodiode–Oxide–Semiconductor Field Effect Transistor

micromachines Article A Graphene/Polycrystalline Silicon Photodiode and Its Integration in a Photodiode–Oxide–Semiconductor Field Effect Transistor Yu-Yang Tsai, Chun-Yu Kuo, Bo-Chang Li, Po-Wen Chiu and Klaus Y. J. Hsu * Institute of Electronics Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan; [email protected] (Y.-Y.T.); [email protected] (C.-Y.K.); [email protected] (B.-C.L.); [email protected] (P.-W.C.) * Correspondence: [email protected]; Tel.: +886-3-574-2594 Received: 25 May 2020; Accepted: 15 June 2020; Published: 17 June 2020 Abstract: In recent years, the characteristics of the graphene/crystalline silicon junction have been frequently discussed in the literature, but study of the graphene/polycrystalline silicon junction and its potential applications is hardly found. The present work reports the observation of the electrical and optoelectronic characteristics of a graphene/polycrystalline silicon junction and explores one possible usage of the junction. The current–voltage curve of the junction was measured to show the typical exponential behavior that can be seen in a forward biased diode, and the photovoltage of the junction showed a logarithmic dependence on light intensity. A new phototransistor named the “photodiode–oxide–semiconductor field effect transistor (PDOSFET)” was further proposed and verified in this work. In the PDOSFET, a graphene/polycrystalline silicon photodiode was directly merged on top of the gate oxide of a conventional metal–oxide–semiconductor field effect transistor (MOSFET). The magnitude of the channel current of this phototransistor showed a logarithmic dependence on the illumination level. It is shown in this work that the PDOSFET facilitates a better pixel design in a complementary metal–oxide–semiconductor (CMOS) image sensor, especially beneficial for high dynamic range (HDR) image detection.