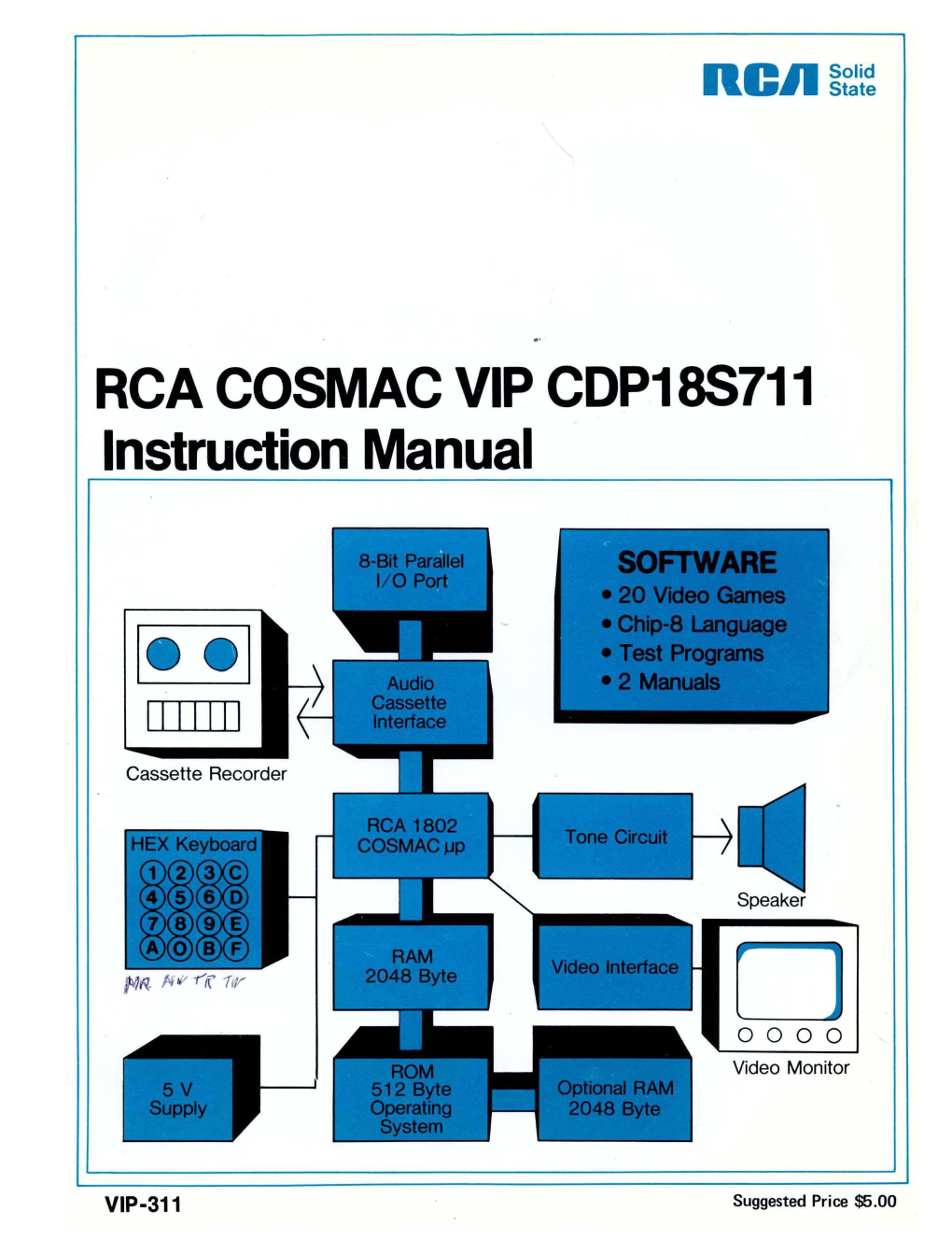

RCA COSMAC VIP CDP188711 Instruction Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Captain Cosmo's Whizbang Has Finally Made the Big Time with a Real Book Review1n Kilobaud Courtesy Satisfied Reader Larry Stone

CAPTAIN ..COSMO'S WHIZ BANG .. By _Jeff • Duntemann For Me and You and the 1802 I WHAT IS THIS? It's a book, by cracky, about the 1802; hopefully the oddest and most entertaining book on any microprocessor ever written. The 1802 is, after all, an odd and entertaining chip. This view is not shared by all. Physicist Mike Brandl said he could swallow a mouthful of sand and barf up a better microprocessor than the 1802, and another colleague claims its instruction set demands that he program with his left hand. Bitch, bitch, bitch. I kinda like it. Much of this material I.rd oped out while recovering from hernia surgery not long ago and couldn't lift anything heavier than a 40-pin DIP. I had a lot of fun and thought you might like to be copied in on it. Like everything else I do, this book is an experiment. If I don't take a serious loss on production and mailing costs, I may do up another one. I've got a little gimcrack on the bench that'll make you people drool: an easy-to-build thermal printer for the 1802 that you can make for seventy bucks flat with all new parts. I'm working on an automatic phone dialer board and a few other things. Selectric interface. Robotics. Ham radio stuff. All kindsa things. Are you interested? Would you lay out another five beans for a Volume II? Let me know; drop me a note with any and all comments and spare not the spleen; I'm a hard man to offend and I lQ~~ crackpot letters. -

Periodical Guide for Computerists 1977

PERIODICAL GUIDE FOR COMPUTERISTS An Index of Magazine Articles for Computer Hobbyists January - December 1977 PERIODICAL GUIDE FOR COMPUTERISTS 1977 TABLE OF CONTENTS AMATEUR RADIO---------------------- 3 MICROCOMPUTERS ANALOG HARDWARE AND CIRCUITS------- 3 GENERAL------------------------- 36 APPLICATIONS, GENERAL-------------- 4 FUNDAMENTALS AND DESIGN--------- 37 ART--------------------------------5 SELECTION GUIDE----------------- 38 ASTRONOMY--------------------------6 AL TAI R 8800 & 680--------------- 38 BAR CODES--------------------------6 APPLE---------------------------39 BIORYTHMS--------------------------6 DI GIT AL GROUP------------------- 39 BIO FEEDBACK------------------------ 6 ELF & VIP ( COSMAC)-------------- 39 BOOKS AND PUBLICATIONS-------------6 HEATHKIT------------------------ 39 BUSINESS AND ACCOUNTING------------ 7 IMSAI--------------------------- 39 CALCULATORS------------------------ 8 INTERCEPT IM6100---------------- 39 CLUBS AND ORGANIZATIONS------------ 9 KIM----------------------------- 39 CLOCKS-----------------------------·9 PET----------------------------- 40 COMMUNICATION---------------------- 10 RADIO SHACK--------------------- 40 CONSTRUCTION----------------------- 10 SOL----------------------------- 40 CONTROL---------------------------- 11 SPHERE-------------------------- 40 CON VE RS ION, CODE------------------- 11 SWTPC--------------------------- 40 CONVERSION, NUMBER BASE------------ 11 WAVE MATE----------------------- 40 DEBUG------------------------------ 12 OTHER MICROCOMPUTERS------------ 41 -

Creative Computing Magazine Is Published Bi-Monthly by Creative Computing

he #1 magazine of computer applicafa *'are raHSJS? sfife a*«uiH O K» » #-. ^ *&> iiD o «» •— "^ Ul JT © O O Ul oo >- at O- X * 3 •O »- •« ^» ^ *© c * c ir — _j «_> o t^ ^ o am z 6 %' 7 * » • • Consumer Computers Buying Guide a/ Paf/i Analysis Electronic Game Reviews Mail Label Programs Someday all terminals will be smart. 128 Functions-software controlled 82 x 16 or 92 x 22 format-plus graphics 7x12 matrix, upper/lower case letters Printer output port 50 to 38,400 baud-selectable "CHERRY" keyboard CT-82 Intelligent Terminal, assembled and tested $795.00 ppd in Cont. U.S. SOUTHWEST TECHNICAL PRODUCTS CORPORATION 219 W. RHAPSODY SAN ANTONIO, TEXAS 78216 CIRCLE 106 ON READER 3ERVICE CARD Give creative Gontpattng to a fHend for " [W*nr fiwter service - call tell free X * • -540-0445] 800-631-8112 InNJ 201 TYPE OF SUBSCRIPTION BOOKS AND MERCHANDISE Foreign Foreign Term USA Surface Air D Gift Send to me 1 2 issues D $ 15 $ 23 $ 39 24 issues D 28 44 76 Gifts cannot be gift wrapped but a 36 issues D 40 64 112 Lifetime D 300 400 600 card with your name will be sent with each order YOUR NAME AND ADDRESS : Quan Cat Descriptions Price Name Address Cittj State Zip- NAME TO APPEAR ON GIFT CARD* SEND GIFT SUBSCRIPTION TO- Name Address Citvf State. .Zip. PAYMENT INFORMATION a Cash , check or 7M.O. enclosed o Visa/BankAmericard") Card no. Books shipping charge SI 00 USA S2 00 Foreign a Master Charge J Exp. NJ Residents add 5% sales lax DPlease bill me ($100 billing fee will be added) be prepaid- TOTAL (magazines and books) Book, orders from individuals must creative computing creative computing Books. -

1900 (Parents: 769, Clones: 1131)

Supported systems: 1900 (parents: 769, clones: 1131) Description [ ] Name [ ] Parent [ ] Year [ ] Manufacturer [ ] Sourcefile [ ] 1200 Micro Computer shmc1200 studio2 1978 Sheen studio2.c (Australia) 1292 Advanced Programmable Video 1292apvs 1976 Radofin vc4000.c System 1392 Advanced Programmable Video 1392apvs 1292apvs 1976 Radofin vc4000.c System 15IE-00-013 ie15 1980 USSR ie15.c 286i k286i ibm5170 1985 Kaypro at.c 3B1 3b1 1985 AT&T unixpc.c 3DO (NTSC) 3do 1991 The 3DO Company 3do.c 3DO (PAL) 3do_pal 3do 1991 The 3DO Company 3do.c 3DO M2 3do_m2 199? 3DO konamim2.c 4004 Nixie Clock 4004clk 2008 John L. Weinrich 4004clk.c 486-PIO-2 ficpio2 ibm5170 1995 FIC at.c 4D/PI (R2000, 20MHz) sgi_ip6 1988 Silicon Graphics Inc sgi_ip6.c 6809 Portable d6809 1983 Dunfield d6809.c 68k Single Board 68ksbc 2002 Ichit Sirichote 68ksbc.c Computer 79152pc m79152pc ???? Mera-Elzab m79152pc.c 800 Junior elwro800 1986 Elwro elwro800.c 9016 Telespiel mtc9016 studio2 1978 Mustang studio2.c Computer (Germany) A5120 a5120 1982 VEB Robotron a51xx.c A5130 a5130 a5120 1983 VEB Robotron a51xx.c A7150 a7150 1986 VEB Robotron a7150.c Aamber Pegasus pegasus 1981 Technosys pegasus.c Aamber Pegasus with pegasusm pegasus 1981 Technosys pegasus.c RAM expansion unit ABC 1600 abc1600 1985 Luxor abc1600.c ABC 80 abc80 1978 Luxor Datorer AB abc80.c ABC 800 C/HR abc800c 1981 Luxor Datorer AB abc80x.c ABC 800 M/HR abc800m abc800c 1981 Luxor Datorer AB abc80x.c ABC 802 abc802 1983 Luxor Datorer AB abc80x.c ABC 806 abc806 1983 Luxor Datorer AB abc80x.c Acorn Electron electron 1983 -

Cosmac Elf 2000 User's Manual

COSMAC ELF 2000 USER'S MANUAL Sixth Edition Copyright © 2004-2006 by Spare Time Gizmos. Visit our web site at www.SpareTimeGizmos.com Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 published by the Free Software Foundation; with no invariant sections; with the front cover text “Portions Copyright © 2004-2006 by Spare Time Gizmos” and our URL, and with no back cover text. A copy of this license may be obtained from http://www.gnu.org/licenses/fdl.txt. CONTENTS 1 OVERVIEW ................................................................................................................................. 1 1.1 REGULATORY WARNING..................................................................................................... 2 1.2 SAFETY WARNING ............................................................................................................. 2 1.3 WARRANTY ....................................................................................................................... 2 2 ASSEMBLY.................................................................................................................................. 5 2.1 ERRATA ............................................................................................................................ 5 2.2 PART SELECTION............................................................................................................... 5 2.3 OPTIONAL SUBSYSTEMS ................................................................................................... -

Assembly Language Step-By-Step: Programming with DOS and Linux

Assembly Language Step-by-Step: Programming with DOS and Linux, Second Edition by Jeff Duntemann ISBN:0471375233 John Wiley & Sons © 2000 (613 pages) A “Lost World” journey into 16-bit assembler programming concepts and techniques. <?xml version="1.0" encoding="ISO-8859-1"?> Table of Contents Assembly Language Step-by-Step—Programming with DOS and Linux, Second Edition Foreword Introduction - "Why Would You Want to Do That?" Another Pleasant Valley Saturday Understanding What Computers Chapter 1 - Really Do Chapter 2 - Alien Bases Getting Your Arms around Binary and Hexadecimal Chapter 3 - Lifting the Hood Discovering What Computers Actually Are The Right to Assemble The Process of Making Assembly Language Chapter 4 - Programs NASM-IDE: A Place to Stand Give me a lever long enough, and a Chapter 5 - place to stand, and I will move the Earth. An Uneasy Alliance The x86 CPU and Its Segmented Memory Chapter 6 - System Following Your Instructions Meeting Machine Instructions up Close Chapter 7 - and Personal Chapter 8 - Our Object All Sublime Creating Programs that Work Dividing and Conquering Using Procedures and Macros to Battle Chapter 9 - Complexity Bits, Flags, Branches, and Tables Easing into Mainstream Chapter 10 - Assembly Programming Chapter 11 - Stringing Them Up Those Amazing String Instructions The Programmer's View of Linux Tools and Skills to Help You Write Chapter 12 - Assembly Code under a True 32-Bit OS Coding for Linux Applying What You've Learned to a True Chapter 13 - Protected Mode Operating System Conclusion - Not the End, But Only the Beginning Appendix A - Partial 8086/8088 Instruction Set Reference Appendix B - Segment Register Assumptions for Real Mode Segmented Model Appendix C - Web URLs for Assembly Programmers Appendix D - Segment Register Assumptions Appendix E - What's on the CD-ROM? Index List of Figures List of Tables Back Cover The bestselling guide to assembly language--now updated and expanded to include coverage of Linux. -

PROGRAMS for the COSMAC ELF INTERPRETERS Paul C. Moews

PROGRAMS FOR THE COSMAC ELF INTERPRETERS PAUL C. MOEWS - 1 - PROGRAMS FOR THE COSMAC ELF INTERPRETERS Paul C. Moews List of Sections 1. Introduction ………………………………………………………………………………………….... 3 2. A Demonstration Interpreter …………………………………………………………………………... 4 3. The CHIP-8 Language …………………………………………………………………………….…... 9 4. Hardware Differences between 1802 Computers ……………………………………………………... 13 5. A Complete ELF CHIP-8 Interpreter ……………………………………………………………….… 13 6. Extending the CHIP-8 Instruction Set ………………………………………………………………… 22 7. Appendix ……………………………………………………………………………………………… 28 List of Programs Machine Code 1. Demonstration Interpreter …………………………………………………………………………….. 8 2. Complete CHIP-8 Interpreter …………………………………………………………………………. 14 3. Additional Skip Instructions …………………………………………………………………………... 22 4. Multiply, Divide and 16 Bit Display Instructions …………………………………………………….. 23 5. Six Bit ASCII Symbols ……………………………………………………………………………….. 25 Interpretive Code 1. Addition (Demonstration Interpreter) …………………………………………………………………. 5 2. Subroutine Use (Demonstration Interpreter) ………………………………………………………….. 5 3. Addition Problems (Demonstration Interpreter) ……………………………………………………… 6 4. Addition Problems (Full Interpreter) ………………………………………………………………….. 10 5. Display ASCII Character (Full Interpreter) …………………………………………………………… 26 Copyright © 1979 by Paul C. Moews All rights reserved Published March, 1979 by Paul C. Moews Printed by Parousia Press, Storrs, Connecticut - 2 - Introduction This booklet’s purpose is to explain the construction and operation of an interpreter -

Cdp1802a, Cdp1802ac, Cdp1802bc

TM CDP1802A, CDP1802AC, CDP1802BC March 1997 CMOS 8-Bit Microprocessors Features Description • Maximum Input Clock Maximum Frequency Options The CDP1802 family of CMOS microprocessors are 8-bit At VDD = 5V register oriented central processing units (CPUs) designed - CDP1802A, AC . 3.2MHz for use as general purpose computing or control elements in - CDP1802BC . 5.0MHz a wide range of stored program systems or products. • Maximum Input Clock Maximum Frequency Options The CDP1802 types include all of the circuits required for At VDD = 10V fetching, interpreting, and executing instructions which have - CDP1802A, AC . 6.4MHz been stored in standard types of memories. Extensive • Minimum Instruction Fetch-Execute Times input/output (I/O) control features are also provided to facili- tate system design. At VDD = 5V - CDP1802A, AC . 5.0µs The 1800 series architecture is designed with emphasis on - CDP1802BC . 3.2µs the total microcomputer system as an integral entity so that systems having maximum flexibility and minimum cost can • Any Combination of Standard RAM and ROM Up to be realized. The 1800 series CPU also provides a synchro- 65,536 Bytes nous interface to memories and external controllers for I/O •8-Bit Parallel Organization With Bidirectional Data Bus devices, and minimizes the cost of interface controllers. Fur- and Multiplexed Address Bus ther, the I/O interface is capable of supporting devices oper- ating in polled, interrupt driven, or direct memory access • 16 x 16 Matrix of Registers for Use as Multiple modes. Program Counters, Data Pointers, or Data Registers The CDP1802A and CDP1802AC have a maximum input •On-Chip DMA, Interrupt, and Flag Inputs clock frequency of 3.2MHz at VDD = 5V. -

The 1802 Membership Card

The 1802 Membership Card For me and you and the 1802 TMSI c/o Lee Hart 814 8th Ave N Sartell MN 56377 (USA) [email protected] http://www.sunrise-ev.com/membershipcard.htm Rev. J2 -- last revised: March 24, 2019 1 What the heck is this? It's an adventure, by cracky! The Membership Card is your ticket to the weird and wonderful world of microcomputing. Our guide will be the COSMAC 1802, perhaps the oddest and most entertaining microprocessor yet invented. I hope you'll find this manual to be equally odd and entertaining. The COSMAC 1802 was created in the 1970's at the dawn of the microcomputer revolution, by Joseph Weisbecker <https://en.wikipedia.org/wiki/Joseph_Weisbecker> of RCA Corporation. It used their new CMOS fabrication process, for very low power consumption, high noise immunity, and was very simple to use. It was intended for military and aerospace; applications too tough for other microcomputers to survive. But Joe was a hacker at heart. He wrote a series of articles starting in the August 1976 issue of Popular Electronics magazine called "Build the COSMAC ELF". It described a simple low-cost computer, using the 1802 microprocessor. At the time, microcomputer systems cost hundreds to thousands of dollars. (Hmm... they still do today!) But Weisbecker's ELF cost about $80! Yet, it was an honest-to-goodness real live computer, able to do anything its much bigger cousins could do -- albeit a bit slower and cruder. It was the ideal computer trainer. Hobbyists built thousands of ELFs, learning about computer design, construction, and programming in the process. -

The DREAM 6800 Computer

The DREAM 6800 Computer This computer first saw the light of day as a series of articles that featured in the May, June, July and August 1979 issues of the now-defunct magazine Electronics Australia and it reappeared in a follow-up booklet entitled Microprocessors and Personal Computers, published in 1980. The DREAM 6800 (Domestic Recreational Educational and Adaptive Microcomputer incorporating the Motorola 6800 microprocessor) was designed by Michael J Bauer from Brisbane's Deakin University. It is not particularly sophisticated but at the time offered those handy with a soldering iron the opportunity to build a simple computer that would be a lot of fun to use. It offered programming in two languages: native 6800 machine code and a strange but quite powerful language called CHIP-8 (Comprehensive Hexadecimal Intetpretive Programming- 8 bit). In its basic form, the language features thirty-three two-byte instructions and had been developed at the RCA Laboratories in the US by one Joe Weisbecker in the 70s, principally for those interested in writing their own games programs. RCA also developed a computer called the COSMAC VIP, that could run programs written in CHIP-8. At the time it was termed a "high level" language but it would hardly even begin to qualify for that description nowadays. Still, writing CHIP-8 programs was, and still is, fun and of particular interest to MicroBee users is the fact that a CHIP-8 interpreter, cleverly linked to MicroWorld BASIC, was written by a Melbourne solicitor, Lindsay Ford and enhanced CHIP-8 still further by providing additional instructions. -

The 1802 Membership Card

The 1802 Membership Card For me and you and the 1802 TMSI c/o Lee Hart 814 8th Ave N Sartell MN 56377 (USA) [email protected] http://www.sunrise-ev.com/membershipcard.htm Rev. JK -- last revised: 10/25/2018 1 What the heck is this? It's an adventure, by cracky! The Membership Card is your ticket to the weird and wonderful world of microcomputing. Our guide will be the COSMAC 1802, perhaps the oddest and most entertaining microprocessor yet invented. I hope you'll find this manual to be equally odd and entertaining. The COSMAC 1802 was created in the 1970's at the dawn of the microcomputer revolution, by Joseph Weisbecker <https://en.wikipedia.org/wiki/Joseph_Weisbecker> of RCA Corporation. It used their new CMOS fabrication process, for very low power consumption, high noise immunity, and was very simple to use. It was intended for military and aerospace; applications too tough for other microcomputers to survive. But Joe was a hacker at heart. He wrote a series of articles starting in the August 1976 issue of Popular Electronics magazine called "Build the COSMAC ELF". It described a simple low-cost computer, using the 1802 microprocessor. At the time, microcomputer systems cost hundreds to thousands of dollars. (Hmm... they still do today!) But Weisbecker's ELF cost about $80! Yet, it was an honest-to-goodness real live computer, able to do anything its much bigger cousins could do -- albeit a bit slower and cruder. It was the ideal computer trainer. Hobbyists built thousands of ELFs, learning about computer design, construction, and programming in the process. -

1802 Microprocessor on Altera Cyclone V Soc

PROJECT DESIGN: 1802 Microprocessor on Altera Cyclone V SoC Prepared by Jennifer Bi, Nelson Gomez, Kundan Guha, and Justin Wong Embedded Systems 4840 May 17, 2019 1 Contents 1 Introduction3 1.1 Overview . .3 1.2 Background . .3 1.3 References . .3 2 System Design and Implementation5 2.1 Hardware-Software Interfaces . .5 3 CPU 6 4 Memory Overview7 5 Peripherals8 5.1 Graphics . .8 5.2 Sound . .8 5.3 Hex Display . .8 6 ISA 9 6.1 1802 ISA . .9 7 Interrupts and DMA 13 8 Timing diagrams 14 9 Testing 16 9.1 Verilator . 16 9.2 TinyElf . 16 10 Code Listings 17 10.1 Hardware files . 17 10.2 Software files . 34 10.3 Verilog files . 42 10.4 Hardware test programs . 57 2 1 Introduction 1.1 Overview We implement the CPD1802 Microprocessor on the Altera Cyclone V SoC FPGA using System Verilog. Our implementation has limited functionality, in particular, we do not support interrupt and DMA CPU states. For the parts that we did implement, our implementation remains faithful to the original COSMAC specification. We verified our 1802 implementation with a test suite written in Verilator. We also provide a small software interface on the SoC's ARM Hard Processor System for starting/restting the 1802 as well as loading memory. In particular, this will enable us to load and run programs. Our original goal was to implement the CPD1861 Video Display Controller in addition to the 1802. This would have enabled us to load an existing implementation of the Chip8 emulator to be able to run Chip8 games on it.