1802 Microprocessor on Altera Cyclone V Soc

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Captain Cosmo's Whizbang Has Finally Made the Big Time with a Real Book Review1n Kilobaud Courtesy Satisfied Reader Larry Stone

CAPTAIN ..COSMO'S WHIZ BANG .. By _Jeff • Duntemann For Me and You and the 1802 I WHAT IS THIS? It's a book, by cracky, about the 1802; hopefully the oddest and most entertaining book on any microprocessor ever written. The 1802 is, after all, an odd and entertaining chip. This view is not shared by all. Physicist Mike Brandl said he could swallow a mouthful of sand and barf up a better microprocessor than the 1802, and another colleague claims its instruction set demands that he program with his left hand. Bitch, bitch, bitch. I kinda like it. Much of this material I.rd oped out while recovering from hernia surgery not long ago and couldn't lift anything heavier than a 40-pin DIP. I had a lot of fun and thought you might like to be copied in on it. Like everything else I do, this book is an experiment. If I don't take a serious loss on production and mailing costs, I may do up another one. I've got a little gimcrack on the bench that'll make you people drool: an easy-to-build thermal printer for the 1802 that you can make for seventy bucks flat with all new parts. I'm working on an automatic phone dialer board and a few other things. Selectric interface. Robotics. Ham radio stuff. All kindsa things. Are you interested? Would you lay out another five beans for a Volume II? Let me know; drop me a note with any and all comments and spare not the spleen; I'm a hard man to offend and I lQ~~ crackpot letters. -

Creative Computing Magazine Is Published Bi-Monthly by Creative Computing

he #1 magazine of computer applicafa *'are raHSJS? sfife a*«uiH O K» » #-. ^ *&> iiD o «» •— "^ Ul JT © O O Ul oo >- at O- X * 3 •O »- •« ^» ^ *© c * c ir — _j «_> o t^ ^ o am z 6 %' 7 * » • • Consumer Computers Buying Guide a/ Paf/i Analysis Electronic Game Reviews Mail Label Programs Someday all terminals will be smart. 128 Functions-software controlled 82 x 16 or 92 x 22 format-plus graphics 7x12 matrix, upper/lower case letters Printer output port 50 to 38,400 baud-selectable "CHERRY" keyboard CT-82 Intelligent Terminal, assembled and tested $795.00 ppd in Cont. U.S. SOUTHWEST TECHNICAL PRODUCTS CORPORATION 219 W. RHAPSODY SAN ANTONIO, TEXAS 78216 CIRCLE 106 ON READER 3ERVICE CARD Give creative Gontpattng to a fHend for " [W*nr fiwter service - call tell free X * • -540-0445] 800-631-8112 InNJ 201 TYPE OF SUBSCRIPTION BOOKS AND MERCHANDISE Foreign Foreign Term USA Surface Air D Gift Send to me 1 2 issues D $ 15 $ 23 $ 39 24 issues D 28 44 76 Gifts cannot be gift wrapped but a 36 issues D 40 64 112 Lifetime D 300 400 600 card with your name will be sent with each order YOUR NAME AND ADDRESS : Quan Cat Descriptions Price Name Address Cittj State Zip- NAME TO APPEAR ON GIFT CARD* SEND GIFT SUBSCRIPTION TO- Name Address Citvf State. .Zip. PAYMENT INFORMATION a Cash , check or 7M.O. enclosed o Visa/BankAmericard") Card no. Books shipping charge SI 00 USA S2 00 Foreign a Master Charge J Exp. NJ Residents add 5% sales lax DPlease bill me ($100 billing fee will be added) be prepaid- TOTAL (magazines and books) Book, orders from individuals must creative computing creative computing Books. -

Cosmac Elf 2000 User's Manual

COSMAC ELF 2000 USER'S MANUAL Sixth Edition Copyright © 2004-2006 by Spare Time Gizmos. Visit our web site at www.SpareTimeGizmos.com Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 published by the Free Software Foundation; with no invariant sections; with the front cover text “Portions Copyright © 2004-2006 by Spare Time Gizmos” and our URL, and with no back cover text. A copy of this license may be obtained from http://www.gnu.org/licenses/fdl.txt. CONTENTS 1 OVERVIEW ................................................................................................................................. 1 1.1 REGULATORY WARNING..................................................................................................... 2 1.2 SAFETY WARNING ............................................................................................................. 2 1.3 WARRANTY ....................................................................................................................... 2 2 ASSEMBLY.................................................................................................................................. 5 2.1 ERRATA ............................................................................................................................ 5 2.2 PART SELECTION............................................................................................................... 5 2.3 OPTIONAL SUBSYSTEMS ................................................................................................... -

Assembly Language Step-By-Step: Programming with DOS and Linux

Assembly Language Step-by-Step: Programming with DOS and Linux, Second Edition by Jeff Duntemann ISBN:0471375233 John Wiley & Sons © 2000 (613 pages) A “Lost World” journey into 16-bit assembler programming concepts and techniques. <?xml version="1.0" encoding="ISO-8859-1"?> Table of Contents Assembly Language Step-by-Step—Programming with DOS and Linux, Second Edition Foreword Introduction - "Why Would You Want to Do That?" Another Pleasant Valley Saturday Understanding What Computers Chapter 1 - Really Do Chapter 2 - Alien Bases Getting Your Arms around Binary and Hexadecimal Chapter 3 - Lifting the Hood Discovering What Computers Actually Are The Right to Assemble The Process of Making Assembly Language Chapter 4 - Programs NASM-IDE: A Place to Stand Give me a lever long enough, and a Chapter 5 - place to stand, and I will move the Earth. An Uneasy Alliance The x86 CPU and Its Segmented Memory Chapter 6 - System Following Your Instructions Meeting Machine Instructions up Close Chapter 7 - and Personal Chapter 8 - Our Object All Sublime Creating Programs that Work Dividing and Conquering Using Procedures and Macros to Battle Chapter 9 - Complexity Bits, Flags, Branches, and Tables Easing into Mainstream Chapter 10 - Assembly Programming Chapter 11 - Stringing Them Up Those Amazing String Instructions The Programmer's View of Linux Tools and Skills to Help You Write Chapter 12 - Assembly Code under a True 32-Bit OS Coding for Linux Applying What You've Learned to a True Chapter 13 - Protected Mode Operating System Conclusion - Not the End, But Only the Beginning Appendix A - Partial 8086/8088 Instruction Set Reference Appendix B - Segment Register Assumptions for Real Mode Segmented Model Appendix C - Web URLs for Assembly Programmers Appendix D - Segment Register Assumptions Appendix E - What's on the CD-ROM? Index List of Figures List of Tables Back Cover The bestselling guide to assembly language--now updated and expanded to include coverage of Linux. -

PROGRAMS for the COSMAC ELF INTERPRETERS Paul C. Moews

PROGRAMS FOR THE COSMAC ELF INTERPRETERS PAUL C. MOEWS - 1 - PROGRAMS FOR THE COSMAC ELF INTERPRETERS Paul C. Moews List of Sections 1. Introduction ………………………………………………………………………………………….... 3 2. A Demonstration Interpreter …………………………………………………………………………... 4 3. The CHIP-8 Language …………………………………………………………………………….…... 9 4. Hardware Differences between 1802 Computers ……………………………………………………... 13 5. A Complete ELF CHIP-8 Interpreter ……………………………………………………………….… 13 6. Extending the CHIP-8 Instruction Set ………………………………………………………………… 22 7. Appendix ……………………………………………………………………………………………… 28 List of Programs Machine Code 1. Demonstration Interpreter …………………………………………………………………………….. 8 2. Complete CHIP-8 Interpreter …………………………………………………………………………. 14 3. Additional Skip Instructions …………………………………………………………………………... 22 4. Multiply, Divide and 16 Bit Display Instructions …………………………………………………….. 23 5. Six Bit ASCII Symbols ……………………………………………………………………………….. 25 Interpretive Code 1. Addition (Demonstration Interpreter) …………………………………………………………………. 5 2. Subroutine Use (Demonstration Interpreter) ………………………………………………………….. 5 3. Addition Problems (Demonstration Interpreter) ……………………………………………………… 6 4. Addition Problems (Full Interpreter) ………………………………………………………………….. 10 5. Display ASCII Character (Full Interpreter) …………………………………………………………… 26 Copyright © 1979 by Paul C. Moews All rights reserved Published March, 1979 by Paul C. Moews Printed by Parousia Press, Storrs, Connecticut - 2 - Introduction This booklet’s purpose is to explain the construction and operation of an interpreter -

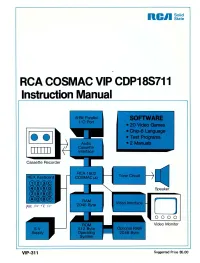

RCA COSMAC VIP CDP188711 Instruction Manual

Solid nell State RCA COSMAC VIP CDP188711 Instruction Manual ~ II IIIII 0000 Video Monitor VIP-311 Suggested Price $5.00 RCA COSMAC VIP CDP18S7i1 Instruction Manual RCA Solid State Division, Somerville, N. J. 08876 Copyright 1978 by RCA Corporation (All rights reserved under Pan-American Copyright Convention) Printed in USA/2-78 VIP-311 ACKNOWLEDGMENT COSMAC VIP has heen created by Joe Weisbecker of the RCA Laboratories, Princeton, N .J. so that everyone can have fun and useful per sonal computer experiences. The elegant and simple hardware system design and the powerful video output together with the customized CHIP-8 language interpreter constitute a fresh and promising approach to personal computers. If questions arise regarding the VIP software or hardware, write to VIP RCA Solid State Division Box 3200 Somerville, N.J. 08876 or telephone Area code 201 526-6141 Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringe ment.s of patents or ~ther rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA. Trademark(s) Registered (f) Marca(s) Registrada(s) __________________________________________________________________-3 Contents I. Getting Started ........................................................... 5 What This Manual Covers .............................................. 5 'The Power Supply ..................................................... 6 -

Cdp1802a, Cdp1802ac, Cdp1802bc

TM CDP1802A, CDP1802AC, CDP1802BC March 1997 CMOS 8-Bit Microprocessors Features Description • Maximum Input Clock Maximum Frequency Options The CDP1802 family of CMOS microprocessors are 8-bit At VDD = 5V register oriented central processing units (CPUs) designed - CDP1802A, AC . 3.2MHz for use as general purpose computing or control elements in - CDP1802BC . 5.0MHz a wide range of stored program systems or products. • Maximum Input Clock Maximum Frequency Options The CDP1802 types include all of the circuits required for At VDD = 10V fetching, interpreting, and executing instructions which have - CDP1802A, AC . 6.4MHz been stored in standard types of memories. Extensive • Minimum Instruction Fetch-Execute Times input/output (I/O) control features are also provided to facili- tate system design. At VDD = 5V - CDP1802A, AC . 5.0µs The 1800 series architecture is designed with emphasis on - CDP1802BC . 3.2µs the total microcomputer system as an integral entity so that systems having maximum flexibility and minimum cost can • Any Combination of Standard RAM and ROM Up to be realized. The 1800 series CPU also provides a synchro- 65,536 Bytes nous interface to memories and external controllers for I/O •8-Bit Parallel Organization With Bidirectional Data Bus devices, and minimizes the cost of interface controllers. Fur- and Multiplexed Address Bus ther, the I/O interface is capable of supporting devices oper- ating in polled, interrupt driven, or direct memory access • 16 x 16 Matrix of Registers for Use as Multiple modes. Program Counters, Data Pointers, or Data Registers The CDP1802A and CDP1802AC have a maximum input •On-Chip DMA, Interrupt, and Flag Inputs clock frequency of 3.2MHz at VDD = 5V. -

The 1802 Membership Card

The 1802 Membership Card For me and you and the 1802 TMSI c/o Lee Hart 814 8th Ave N Sartell MN 56377 (USA) [email protected] http://www.sunrise-ev.com/membershipcard.htm Rev. J2 -- last revised: March 24, 2019 1 What the heck is this? It's an adventure, by cracky! The Membership Card is your ticket to the weird and wonderful world of microcomputing. Our guide will be the COSMAC 1802, perhaps the oddest and most entertaining microprocessor yet invented. I hope you'll find this manual to be equally odd and entertaining. The COSMAC 1802 was created in the 1970's at the dawn of the microcomputer revolution, by Joseph Weisbecker <https://en.wikipedia.org/wiki/Joseph_Weisbecker> of RCA Corporation. It used their new CMOS fabrication process, for very low power consumption, high noise immunity, and was very simple to use. It was intended for military and aerospace; applications too tough for other microcomputers to survive. But Joe was a hacker at heart. He wrote a series of articles starting in the August 1976 issue of Popular Electronics magazine called "Build the COSMAC ELF". It described a simple low-cost computer, using the 1802 microprocessor. At the time, microcomputer systems cost hundreds to thousands of dollars. (Hmm... they still do today!) But Weisbecker's ELF cost about $80! Yet, it was an honest-to-goodness real live computer, able to do anything its much bigger cousins could do -- albeit a bit slower and cruder. It was the ideal computer trainer. Hobbyists built thousands of ELFs, learning about computer design, construction, and programming in the process. -

The 1802 Membership Card

The 1802 Membership Card For me and you and the 1802 TMSI c/o Lee Hart 814 8th Ave N Sartell MN 56377 (USA) [email protected] http://www.sunrise-ev.com/membershipcard.htm Rev. JK -- last revised: 10/25/2018 1 What the heck is this? It's an adventure, by cracky! The Membership Card is your ticket to the weird and wonderful world of microcomputing. Our guide will be the COSMAC 1802, perhaps the oddest and most entertaining microprocessor yet invented. I hope you'll find this manual to be equally odd and entertaining. The COSMAC 1802 was created in the 1970's at the dawn of the microcomputer revolution, by Joseph Weisbecker <https://en.wikipedia.org/wiki/Joseph_Weisbecker> of RCA Corporation. It used their new CMOS fabrication process, for very low power consumption, high noise immunity, and was very simple to use. It was intended for military and aerospace; applications too tough for other microcomputers to survive. But Joe was a hacker at heart. He wrote a series of articles starting in the August 1976 issue of Popular Electronics magazine called "Build the COSMAC ELF". It described a simple low-cost computer, using the 1802 microprocessor. At the time, microcomputer systems cost hundreds to thousands of dollars. (Hmm... they still do today!) But Weisbecker's ELF cost about $80! Yet, it was an honest-to-goodness real live computer, able to do anything its much bigger cousins could do -- albeit a bit slower and cruder. It was the ideal computer trainer. Hobbyists built thousands of ELFs, learning about computer design, construction, and programming in the process. -

The Early Model Personal Computer Contest Oliver Strimpei

3 2 1 D MK0096 t.. ,.1.) ::l''l:1±j~ RAM NOTES: (c ... tlnued Ir~m .h., JIll ,. UNiT. AS SU P PLIEO, IN_ CLUDES" UCl MICR,O PROCESSOR, AND SOLDER JUMPERS AT 80TH POINTS MA ltltEO "~SOl". AND 1tA5 OM ITTED ,.,LL tOMPON_ tNT5 SHOWN WITHI N THE DOTTED BOX. IF' A UOG IS SU.8$TITl1TEO FOR THE c UOZ IT IS NECESSARY TO u.;STAt.1. ALI. COM PON_ £NTS SHOWN. AND TO BR.EAK BOTH SOLDER, IUUDGES NOTEO " 6'>02". 8. UNIT [S SUPPLIED WI TH: Y J."'p... d to eSF Z '."'p",.d to CS[) W '."'p«od 'oal ..... X Jump.tod tOes" R. 5, " no! T. ARt: USI:R S ELECTABl.E OllP SE LXCTS. (4K III..OCKS) .. KYBD ~ OS P AI\.£ INTER RUPT OUTPIITS F ROM PIA. POINTS LABELEO " 111,0". " "NMt" ARE INTERRIIPT NOf('" • INPUTS FROM MIC RO • , PROCESSOR. FOR NOR_ M AL OPERATION NO JUMPE RS A RE R£QIIJlU:O. K£YIIOA IU) SOCKE T, ( B.), '". PIN I S, 18 1T Sf, SHOU\"D 8t JUM PtRtD T O V oe t+ SV ), rOR NORMAL B O P ERATION W[TH SUP PLIED SOF TWARE. NOTE 12 II. PROMS ARE U6 ••. AND MAY liE ONE OF THE FOL.L.OWING TYPES, SIGNETICS USIl9. HARRIS HIOZ4. INTELIM"'I 1601. 12. VOLTAGES (+12. -HlON E Jx;E CONNECTOR ARt UNREGUI..ATto. F II..TERED 0. C • • AND SHOULD NOT lit USED WITHOUT ADDED REGULATION. I I. IF DIotA REQUIRED. IlREAK JUMPtR SHOWN. USt T4SU' AT POSITIONS II~ . 116 . 81. A:<D III. -

Popular Electronics AUGUST 1976

Popular Electronics AUGUST 1976 Build The COSMAC "ELF" A Low-Cost Experimenter's Microcomputer BY JOSEPH WEISBECKER Part 1: Simple-to-build computer trainer can be expanded for advanced applications Part 2: Some hardware improvements and more programming details Part 3: How to expand memory, plus more programs Part4: Build the PIXIE Graphic Display - Adding one chip to the Elf provides complete video interface and animated graphicscapability for less than $25 1 Build The COSMAC "ELF" A Low-Cost Experimenter's Microcomputer Part 1 PE Tested Simple-to-build computer trainer can be expanded for advanced applications. BY JOSEPH WEISBECKER There are basically two ways in which you can get involved with microcomputers on the nonprofessional level. You can buy one of several reasonably priced hobby computer kits, add a TV or typewriter terminal, and learn to use high-level language. On the other hand, you can build your own inexpensive system from scratch. This permits you to experiment with simple applications that do not require an expensive terminal or a large memory. You can communicate with the computer in a relatively simple language. The "Elf" microcomputer project gives you the latter category of computer system -- for about $80. It is an excellent hardware and software trainer that uses machine language and can be easily expanded to do just about anything a full-blown microcomputer can. Packaging, however, is up to you. 2 The basic Elf has toggle-switch input, hex LED display, 256 bytes of RAM, four input lines and a latched output line. It can be used to play games, sequence lights, control motors, generate test pulses, count or time events, monitor intruder-alert devices, etc. -

Retrobrew Computers Forum After That, I Decided to Start Building "New" Vintage Stuff and Discovered the ECB Z80 Board Built by Andrew Lynch

Subject: Welcome to the new RBC Forum & introductions Posted by Andrew B on Sun, 01 Nov 2015 04:21:12 GMT View Forum Message <> Reply to Message Hello fellow homebrew computer enthusiasts! Welcome to the new RBC forum. I'll be making a few threads to cover different topics, but I thought it might be fun to start the next phase of our group with some new introductions for everyone. I'm only 30 so I missed the eras of the S-100-type compueters and the early PCs, but my the first computer my family had was an IBM 5150 that a friend gave us (formerly owned by someone who had worked at IBM's chip fab in Burlington, VT) It had all of the manuals and original IBM software, so it gave me a pretty good start on retro computers. We progressed through another used 8088 (an Epson Equity 1 with the full 640k and CGA) and a Northgate 286, before I finally convinced my family to buy a brand new PC. Even after we had a new family PC, the first PC I had that was just mine was a Packard Bell 486. So I've used a range of different eras of hardware. The programming skills I learned in BASICA eventually go upgraded to QuickBASIC, then in college to MATLAB and Python. My work is as a mechanical/propulsion engineer designing/building spacecraft subsystems (there's some parts I built when I was at JPL on Mars right now with the Curiosityrover , and now I'm working on the new Dragon 2 crewed spacecraft at SpaceX), but I've gotten a lot out of the skills the original PC gave me in terms of not being scared to write some code to make a job easier or build a board to interface mechanical hardware to electrical hardware.