A CMOS, Self Calibrating, 100Mhz RC-Oscillator for ASIC Applications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

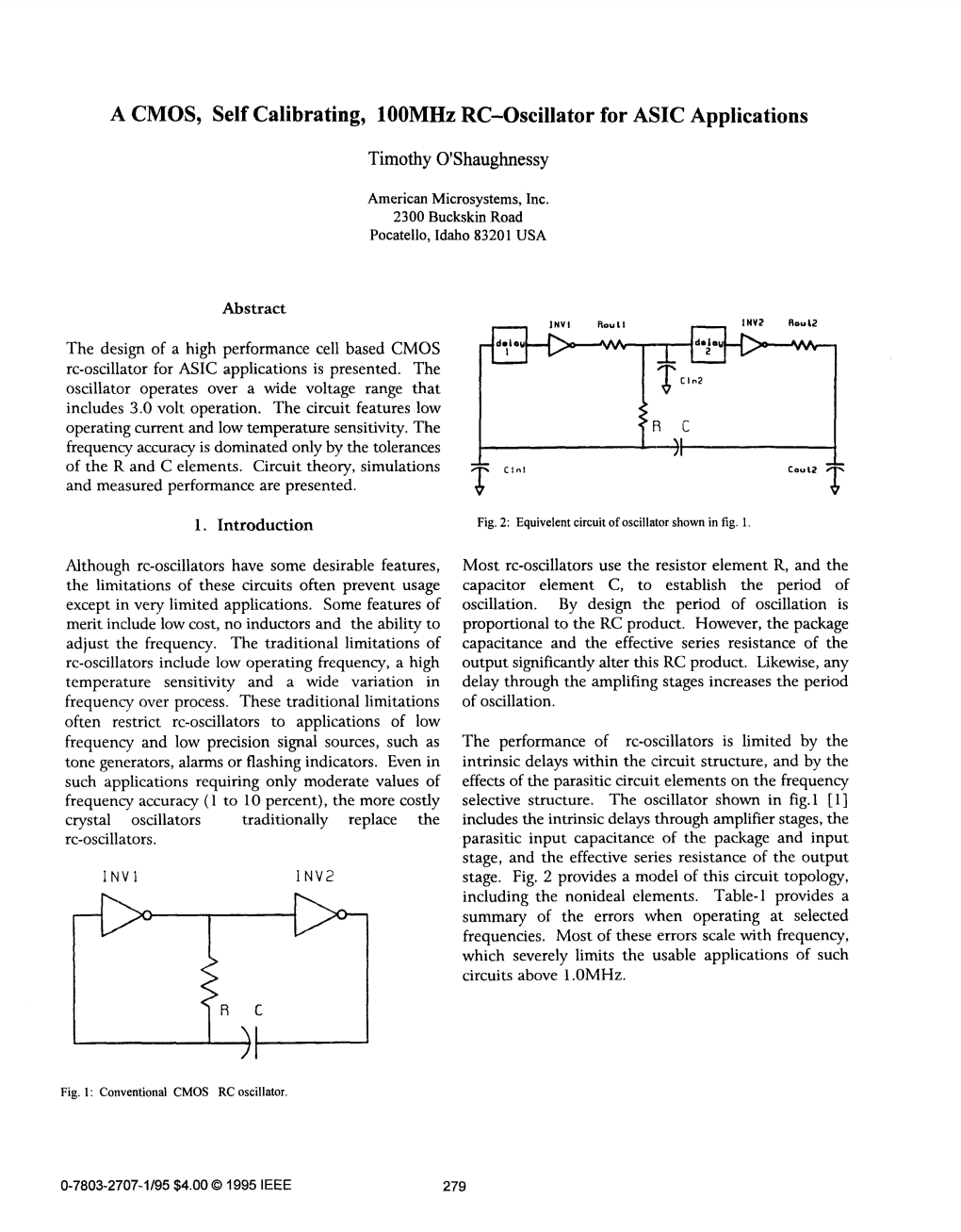

Oscillator Design

Oscillator Design •Introduction –What makes an oscillator? •Types of oscillators –Fixed frequency or voltage controlled oscillator –LC resonator –Ring Oscillator –Crystal resonator •Design of oscillators –Frequency control, stability –Amplitude limits –Buffered output –isolation –Bias circuits –Voltage control –Phase noise 1 Oscillator Requirements •Power source •Frequency-determining components •Active device to provide gain •Positive feedback LC Oscillator fr = 1/ 2p LC Hartley Crystal Colpitts Clapp RC Wien-Bridge Ring 2 Feedback Model for oscillators x A(jw) i xo A (jw) = A f 1 - A(jω)×b(jω) x = x + x d i f Barkhausen criteria x f A( jw)× b ( jω) =1 β Barkhausen’scriteria is necessary but not sufficient. If the phase shift around the loop is equal to 360o at zero frequency and the loop gain is sufficient, the circuit latches up rather than oscillate. To stabilize the frequency, a frequency-selective network is added and is named as resonator. Automatic level control needed to stabilize magnitude 3 General amplitude control •One thought is to detect oscillator amplitude, and then adjust Gm so that it equals a desired value •By using feedback, we can precisely achieve GmRp= 1 •Issues •Complex, requires power, and adds noise 4 Leveraging Amplifier Nonlinearity as Feedback •Practical trans-conductance amplifiers have saturating characteristics –Harmonics created, but filtered out by resonator –Our interest is in the relationship between the input and the fundamental of the output •As input amplitude is increased –Effective gain from input -

Ultra Low Power RC Oscillator for System Wake-Up Using Highly

Ultra Low Power RC Oscillator for System wake-up using highly precise Auto-Calibration Technique Joonhyung, Lim#1, Kwangmook, Lee#2, Koonsik, Cho#3 # Ubiquitous Conversion Team, Samsung Electro-Mechanics, Suwon, Gyunggi-Do, Korea, 443-743 [email protected], [email protected], [email protected] Abstract— An ultra low power RC oscillator for system wake-up A. The design of RC oscillator is implemented using 0.18um CMOS process. The modern mobile systems need system clock which consumes low power and thus saves limited battery power in order to wake up from sleep-mode. A RC oscillator operates in the subthreshold region to reduce current consumption. The output frequency of RC oscillator is very weakly dependent on process and temperature variation using auto-calibration. This RC oscillator is featured as follows: the current consumption is 0.2 ㎂; the supply voltage is 1.8V; the output frequency is 31.25 KHz with 1.52(Relative 3σ)% accuracy after calibration; it has only 0.4%/℃ temperature coefficient; its size is 190 um x 80 um exclude bonding pad. I. INTRODUCTION Many applications, such as PDA, mobile communication devices need to operate with low power consumption and low supply voltage to fulfil the requirement of long-term operation. For such System-on-Chips (SoCs), embedded a system wake up circuit is necessary [1]. Several analogue and digital blocks such as clock generator, timer and SRAM for retention must be activated to wake system up from a sleep-mode. Especially, a clock generator, which is the heart of digital circuits, will output unknown waveform of clock and the system will enter Fig. -

Simple Two-Transistor Single-Supply Resistor-Capacitor Chaotic Oscillator Lars Keuninckx, Guy Van Der Sande and Jan Danckaert†

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II, VOL. X, NO. Y, DECEMBER 2015 1 Simple Two-Transistor Single-Supply Resistor-Capacitor Chaotic Oscillator Lars Keuninckx, Guy Van der Sande and Jan Danckaerty Abstract—We have modified an otherwise standard one- adding a dimension to a predominantly two-dimensional limit transistor self-biasing resistor-capacitor phase-shift oscillator to cycle oscillator. In other cases, notably the Collpits oscilla- induce chaotic oscillations. The circuit uses only two transistors, tor [7], a chaotic regime is already present for certain values no inductors, and is powered by a single supply voltage. As such it is an attractive and low-cost source of chaotic oscillations for of the design parameters. Others directly translate a known many applications. We compare experimental results to Spice chaotic system of differential equations to electronics. The simulations, showing good agreement. We qualitatively explain necessary nonlinear terms are implemented by using dedicated the chaotic dynamics to stem from hysteretic jumps between analog multipliers as in reference [8] or operational amplifier unstable equilibria around which growing oscillations exist. based piece wise continious functions [9]. Being able to Index Terms—chaos, oscillator. nonlinear dynamics, RC- avoid operational amplifiers and dedicated multipliers is a ladder. plus in terms of cost and circuit complexity, as there is Copyright (c) 2014 IEEE. Personal use of this material is no connection between complexity -in terms of used parts- permitted. However, permission to use this material for any of the circuit and complexity of the chaotic oscillations -in other purposes must be obtained from the IEEE by sending terms of measurable quantitative properties such as entropy, an email to [email protected] attractor dimension, spectral content etc. -

Oscillator Design Considerations

AN0016.0: Oscillator Design Considerations This application note provides an introduction to the oscillators in MCU Series 0 or Wireless MCU Series 0 devices and provides KEY POINTS guidelines in selecting correct components for their oscillator cir- • Crystal oscillators are more precise and cuits. stable, but are more expensive and start up more slowly than RC and ceramic The MCU Series 0 or Wireless MCU Series 0 devices contain two crystal oscillators: oscillators. one low speed (32.768 kHz) and one high speed (4-50 MHz depending on the device, • Learn what parameters are important see datasheet for more information). Topics covered include oscillator theory and some when selecting an oscillator. recommended crystals for these devices. • Learn how to reduce power consumption when using an external oscillator. Reactance f S f A Frequency silabs.com | Building a more connected world. Rev. 1.30 AN0016.0: Oscillator Design Considerations Device Compatibility 1. Device Compatibility This application note supports multiple device families, and some functionality is different depending on the device. MCU Series 0 consists of: • EFM32 Gecko (EFM32G) • EFM32 Giant Gecko (EFM32GG) • EFM32 Wonder Gecko (EFM32WG) • EFM32 Leopard Gecko (EFM32LG) • EFM32 Tiny Gecko (EFM32TG) • EFM32 Zero Gecko (EFM32ZG) • EFM32 Happy Gecko (EFM32HG) Wireless MCU Series 0 consists of: • EZR32 Wonder Gecko (EZR32WG) • EZR32 Leopard Gecko (EZR32LG) • EZR32 Happy Gecko (EZR32HG) silabs.com | Building a more connected world. Rev. 1.30 | 2 AN0016.0: Oscillator Design Considerations Oscillator Theory 2. Oscillator Theory 2.1 What is an Oscillator? An oscillator is an electronic circuit which generates a repetitive, or periodic, time-varying signal. -

A 1.8 V 18.13 Mhz Inverter-Based On-Chip RC Oscillator with Flicker Noise Suppression Using Logic Transition Voltage Feedback

electronics Article A 1.8 V 18.13 MHz Inverter-Based On-Chip RC Oscillator with Flicker Noise Suppression Using Logic Transition Voltage Feedback Junsoo Ko and Minjae Lee * School of Electrical Engineering and Computer Science, Gwangju Institute of Science and Technology, Gwangju 61005, Korea; [email protected] * Correspondence: [email protected]; Tel.: +81-62-715-2205 Received: 21 October 2019; Accepted: 11 November 2019; Published: 15 November 2019 Abstract: An inverter-based on-chip resistor capacitor (RC) oscillator with logic transition voltage (LTV) tracking feedback for circuit delay compensation is presented. In order to achieve good frequency stability, the proposed technique considers the entire inverter chain as a comparator block and changes the LTV to control the oscillation frequency. Furthermore, the negative feedback structure also reduces low-frequency offset phase noise. With a 1.8 V supply and at room temperature, the suggested oscillator operates at 18.13 MHz, consuming 245.7 µW. Compared to the free-running case, the proposed technique reduces phase noise by 7.7 dB and 5.45 dB at 100 Hz and 1 kHz, respectively. The measured phase noise values are 60.09 dBc/Hz at 1 kHz with a figure of merit − (FOM) of 151.35 dB/Hz, and 106.27 dBc/Hz at 100 KHz with an FOM of 157.53 dBc/Hz. The proposed − oscillator occupies 0.056 mm2 in a standard 0.18 µm CMOS process. Keywords: RC on-chip oscillator; low phase noise; inverter-based; logic transition voltage tracking 1. Introduction As smart devices become more popular and the market demand for wearable devices grows, the need for low-power, on-chip resistor capacitor (RC) oscillators in a standard CMOS process is increasing, to address the cost and board area issues in external crystal oscillators. -

RC Phase-Shift Network

RC Phase-Shift Network In a Resistance-Capacitance Oscillator or simply an RC Oscillator, we make use of the fact that a phase shift occurs between the input to a RC network and the output from the same network by using RC elements in the feedback branch, for example. The circuit on the left shows a single resistor-capacitor network whose output voltage “leads” the input voltage by some angle less than 90o. An ideal single-pole RC circuit would produce a phase shift of exactly 90o, and because 180o of phase shift is required for oscillation, at least two single-poles must be used in an RC oscillator design. However in reality it is difficult to obtain exactly 90o of phase shift so more stages are used. The amount of actual phase shift in the circuit depends upon the values of the resistor and the capacitor, and the chosen frequency of oscillations with the phase angle ( Φ ) being given as: RC Phase Angle Where: XC is the Capacitive Reactance of the capacitor, R is the Resistance of the resistor, and ƒ is the Frequency. In our simple example above, the values of R and C have been chosen so that at the required frequency the output voltage leads the input voltage by an angle of about 60o. Then the phase angle between each successive RC section increases by another 60o giving a phase difference between the input and output of 180o (3 x 60o) as shown by the following vector diagram. Vector Diagram Then by connecting together three such RC networks in series we can produce a total phase shift in the circuit of 180o at the chosen frequency and this forms the bases of a “phase shift oscillator” otherwise known as a RC Oscillator circuit. -

CHAPTER Feedback Amplifier & Oscillators

Analog Circuits Day-12 Oscillators Introduction to Feedback: The phenomenon of feeding a portion of the output signal back to the input circuit is known as feedback. The effect results in a dependence between the output and the input and an effective control can be obtained in the working of the circuit. Feedback is of two types. • Negative Feedback • Positive Feedback Negative or Degenerate feedback: • In negative feedback, the feedback energy (voltage or current), is out of phase with the input signal and thus opposes it. • Negative feedback reduces gain of the amplifier. It also reduce distortion, noise and instability. • This feedback increases bandwidth and improves input and output impedances. • Due to these advantages, the negative feedback is frequently used in amplifiers. NegativeFeedback Positive or regenerate feedback: • In positive feedback, the feedback energy (voltage or currents), is in phase with the input signal and thus aids it. Positive feedback increases gain of the amplifier also increases distortion, noise and instability. • Because of these disadvantages, positive feedback is seldom employed in amplifiers. But the positive feedback is used in oscillators. Positive Feedback In the above figure, the gain of the amplifier is represented as A. The gain of the amplifier is the ratio of output voltage Vo to the input voltage Vi. The feedback network extracts a voltage Vf = β Vo from the output Vo of the amplifier. This voltage is subtracted for negative feedback, from the signal voltage Vs. Now, Vi=Vs + Vf =Vs+βVo The quantity β = Vf/Vo is called as feedback ratio or feedback fraction. The output Vo must be equal to the input voltage (Vs + βVo) multiplied by the gain A of the amplifier. -

A 120Nw 18.5Khz RC Oscillator with Comparator Offset Cancellation for ±0.25% Temperature Stability

A 120nW 18.5kHz RC oscillator with comparator offset cancellation for ±0.25% temperature stability The MIT Faculty has made this article openly available. Please share how this access benefits you. Your story matters. Citation Paidimarri, A., D. Griffith, A. Wang, A. P. Chandrakasan, and G. Burra. “A 120nW 18.5kHz RC Oscillator with Comparator Offset Cancellation for ±0.25% Temperature Stability.” 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers (February 2013). As Published http://dx.doi.org/10.1109/ISSCC.2013.6487692 Publisher Institute of Electrical and Electronics Engineers (IEEE) Version Author's final manuscript Citable link http://hdl.handle.net/1721.1/92830 Terms of Use Creative Commons Attribution-Noncommercial-Share Alike Detailed Terms http://creativecommons.org/licenses/by-nc-sa/4.0/ 10.7 A 120nW 18.5kHz RC Oscillator with Comparator Offset to-rail glitches at the output of the inverters. In order to prevent these glitches, Cancellation for ±0.25% Temperature Stability and limit cycling, the first buffer stage connected to the comparator is a Schmitt trigger, implemented in a digital fashion. A small hysteresis minimizes asymmetry Arun Paidimarri 1, Danielle Griffith 2, Alice Wang 3, Anantha Chandrakasan 1 in the switching point of the comparator in the two phases. Weak high-VT transistors provide a hysteresis of a few 10s of mV, which is still sufficient to and Gangadhar Burra 2 eliminate glitches. The Schmitt trigger and subsequent inverters add <10ns to the overall delay, and hence do not affect temperature stability of the oscillator. 1 Massachusetts Institute of Technology, Cambridge, MA 2 Texas Instruments, Dallas, TX The oscillator was fabricated in a 65nm CMOS process. -

RC PHASE SHIFT OSCILLATOR USING BJT AIM to Design RC Phase Shift Oscillator

Experiment No. 12 RC PHASE SHIFT OSCILLATOR USING BJT AIM To design RC phase shift oscillator. THEORY An oscillator is essentially a source of emf. Its output may be a sine wave, a square wave, a triangular wave or a ramp. It is possible to vary the frequency and amplitude of the output. In this experiment we will be concerned only with sine wave oscillators. Feedback is said to exist in an amplifier if a part of its output is brought back into the input circuit. Consider the situation in figure 1. A fraction β (β < 1) of the output Vo is brought back into the input circuit. The net input Vi to the amplifier can then be written in two different ways. Fig 1. Basic oscillator block diagram VVi s V o (1) where Vs is an external input In equation (1) the feedback is said to be positive. Both Vs and βVo drive the input terminal. So, this is positive feedback. If A is the voltage gain of the amplifier. Vo AV i (2) From equation (1) and (2) V o V V A s o Hence gain Ar of the whole circuit including the feedback network is given by Vo A Ar Vs (1 A ) Thus, positive feedback increases the gain from A to Ar. If Vs is reduced to 0 and Vo made equal to Vi, we get an amplifier that supplies its own input. An output voltage is obtained even in the absence of an external input. This happens when A 1. An amplifier that supplies its own input is an oscillator. -

Microwave Oscillator

OPERATING INSTRUCTIONS TYPE 1360-A MICROWAVE OSCILLATOR ...... w 0 "'I )> GENERAL RADIO COMPANY A O·PERATING INSTRUCTIONS TYP·E 1360-A MICROWAVE OSCILLATOR Form 1360-0100-A April, 1962 Copyright 1962 by General Radio Company West Concord, Massachusetts, USA GENERAL R A D I 0 COMPANY WEST CONCORD, MASSACHUSETTS, USA TABLE OF CONTENTS Section 1. INTRODUCTION . 1 1.1 Purpose. • . 1 1.2 Description . 1 1.3 Accessories. 2 1. 4 Mounting . 2 Section 2. OPERATING PROCEDURE . 2 2.1 Installation 2 2.2 Operation. • . 2 2.3 Modulation . • . 3 Section 3. PRINCIPLES OF OPERATION 4 3.1 Reflex Klystron Oscillator 4 3.2 Electronic Circuit . 4 3. 3 Output System . • . 6 Section 4. SERVICE AND MAINTENANCE 7 4.1 General. • . 7 4.2 Removal of Instrument from Cabinet. 7 4.3 Routine Maintenance . 7 4.4 Trouble-Shooting . 8 4.5 Tracking Adjustment. 9 4.6 Mechanical Alignment of Oscillator 9 4. 7 Klystron Replacement . 10 4.8 Detector . • . • . 10 4.9 Table of Voltages and Resistances. 10 Figure 1. Panel view of the Type 1360-A Microwave Oscillator. SPECIFICATim-IS FREQUENCY Square-Wave: 50 cps to 200 kc, 12-v (rms) sine wave or 20-v (peak-to-peak) square wave; 20% Range: 1.7 to 4.1 Gc in two ranges, 1.7 to 2.8 Gc minimum duty cycle from external source. and 2.6 to 4.1 Gc. Input impedance greater than 100 kilohms. Fine Frequency Control (LF): Order of 1 Me, but Pulse: Rise and fall times approximately 0.2 not functioning for square-wave modulation. -

Design and Performance Analysis of a Twin T-Bridge RC Harmonic Oscillation Generator with an Operational Amplifier

Indonesian Journal of Electrical Engineering and Informatics (IJEEI) Vol. 7, No. 2, June 2019, pp. 338~344 ISSN: 2089-3272, DOI: 10.11591/ijeei.v7i2.694 338 Design and performance analysis of a twin T-bridge RC harmonic oscillation generator with an operational amplifier Boyan Karapenev Department of the Communication Equipment and Technologies, Technical University of Gabrovo, Bulgaria Article Info ABSTRACT Article historys: This paper presents the special features of harmonic generators and their widespread use and in particular the design, simulation and experimental Received Nov 9, 2018 studies of a twin T-bridge RC generator with an operational amplifier. Revised Apr 25, 2019 The results obtained are analyzed and compared. For the particular Accepted May 20, 2019 implementation, the frequency error varies from 4 % in experimental studies to 6.7 % in the simulation, and in this case an average value of 5.35 % can be assumed. Keywords: Analysis Design RC harmonic oscillation generator Studies Copyright © 2019 Institute of Advanced Engineering and Science. Twin T-bridge All rights reserved. Corresponding Author: Boyan Karapenev, Department of the Communication Equipment and Technologies, Technical University of Gabrovo, Ul. "Hadji Dimitar" 4, 5300 Gabrovo Center, Gabrovo, Bulgaria. Email: [email protected] 1. INTRODUCTION The development of technology over the last decades has led to the need to employ electronics in an increasing proportion of human activities. This necessity induces a constant improvement of the existing and the creation of new electronic equipment, where electronic generators find a wide application as a primary source of electrical signals. Electronic generators are also very useful in communications [1-3]. -

INSTITUTION Controlledoscillators. Each Lesson Follows a Typical

DOCUMENT RESUME ED 190 906 CE 026 591 TITLE ' Military Curricula'for Vocational & Technical . Education. Baied Electricity and Electronics*. CANTRAC A-100%0010. Module 32: Intermediate Oscillators. Study Booklet. INSTITUTION Chief of Naial Education and Training Support, Pensacola, Fla.: Ohio State Univ., Columbus. National Center for Research in Vocational Education. '. FEPORT No CMTT-E-050 rut DATE Jul BO NOTE 262p.:Forfrelateddocuments see CE 026 560-593. --, , EDRS PRICE MFO1 /PC11 Plus Postage. DESCFIFTORS . *Electricty: *Electronics: Individualized Instruction: Learning Activities: Learning Modules: Postsecondary Education: Programed Instruction:' *Technical Education IDENTIFIERS Military COrriculum Project: *Oscillators ABSTRACT This individualized learning module on intermediate oscillators is one in a series of modules for a course in basic electricity and electronics. The course is one of a number of military-developed curriculum packages selected for adaptation to vocational instructional and curriculum develbpsent in a civilian setting. Five lessons are included in the module: (1) Hartley . Oscillators,(2) Resistiye Capacitive Phase Shift Oscillators, (21 Wien.-Bridge Cscillators, (U) Blocking Oscillators, and(5) Crystal ControlledOscillators. Each lesson follows a typical format including a lesson overview, a list of study resources, the lesson content, a programmed instruction sections, and .a lesson summary. (Progress checks and other supplementary material are provided for each lesson in a students guide, CE 026 590.1 (LEA) i' *********************************************************************** * Reproductions supplied by EDRS are the best that can be jade * * from the original document. * *********************************************************************** rd. .1770.1114.131Pr Ara:AIL* %IR 6 10 411. t v-- . C:k LAJ CHIEF OF NAVAL EDUCATION AND TRAINING.1, ilitaryurrla CNTT-E-054. \\.. 4- al JULY 1980 we' Technical Education I BASIC ELECTRICITY AND ELECTRONICS'.