Oscillator Design

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Ariel Moss EE 254 Project 6 12/6/13 Project 6: Oscillator Circuits The

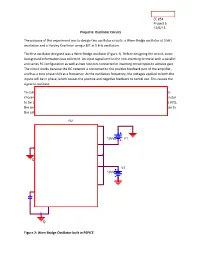

Ariel Moss EE 254 Project 6 12/6/13 Project 6: Oscillator Circuits The purpose of this experiment was to design two oscillator circuits: a Wien-Bridge oscillator at 3 kHz oscillation and a Hartley Oscillator using a BJT at 5 kHz oscillation. The first oscillator designed was a Wien-Bridge oscillator (Figure 1). Before designing the circuit, some background information was collected. An input signal sent to the non-inverting terminal with a parallel and series RC configuration as well as two resistors connected in inverting circuit types to achieve gain. The circuit works because the RC network is connected to the positive feedback part of the amplifier, and has a zero phase shift at a frequency. At the oscillation frequency, the voltages applied to both the inputs will be in phase, which causes the positive and negative feedback to cancel out. This causes the signal to oscillate. To calculate the time constant given the cutoff frequency, Calculation 1 was used. The capacitor was chosen to be 0.1µF, which left the input, series, and parallel resistors to be 530Ω and the output resistor to be 1.06 kHz. The signal was then simulated in PSPICE, and after adjusting the output resistor to 1.07Ω, the circuit produced a desired simulation with time spacing of .000335 seconds, which was very close to the calculated time spacing. (Figures 2-3 and Calculations 2-3). R2 1.07k 10Vdc V1 R1 LM741 4 2 V- 1 - OS1 530 6 OUT 0 3 5 + 7 OS2 U1 V+ V2 10Vdc Cs Rs 0.1u 530 Cp Rp 0.1u 530 0 Figure 2: Wien-Bridge Oscillator built in PSPICE Ariel Moss EE 254 Project 6 12/6/13 Figure 3: Simulation of circuit Next the circuit was built and tested. -

Chapter 19 - the Oscillator

Chapter 19 - The Oscillator The Electronics Curse “Your amplifiers will oscillate, your oscillators won't!” Question, What is an Oscillator? A Pendulum is an Oscillator... “Oscillators are circuits that are used to generate A.C. signals. Although mechanical methods, like alternators, can be used to generate low frequency A.C. signals, such as the 50 Hz mains, electronic circuits are the most practical way of generating signals at radio frequencies.” Comment: Hmm, wasn't always. In the time of Marconi, generators were used to generate a frequency to transmit. We are talking about kiloWatts of power! e.g. Grimeton L.F. Transmitter. Oscillators are widely used in both transmitters and receivers. In transmitters they are used to generate the radio frequency signal that will ultimately be applied to the antenna, causing it to transmit. In receivers, oscillators are widely used in conjunction with mixers (a circuit that will be covered in a later module) to change the frequency of the received radio signal. Principal of Operation The diagram below is a ‘block diagram’ showing a typical oscillator. Block diagrams differ from the circuit diagrams that we have used so far in that they do not show every component in the circuit individually. Instead they show complete functional blocks – for example, amplifiers and filters – as just one symbol in the diagram. They are useful because they allow us to get a high level overview of how a circuit or system functions without having to show every individual component. The Barkhausen Criterion [That's NOT ‘dog box’ in German!] Comment: In electronics, the Barkhausen stability criterion is a mathematical condition to determine when a linear electronic circuit will oscillate. -

Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University

Marquette University e-Publications@Marquette Master's Theses (2009 -) Dissertations, Theses, and Professional Projects Analysis of BJT Colpitts Oscillators - Empirical and Mathematical Methods for Predicting Behavior Nicholas Jon Stave Marquette University Recommended Citation Stave, Nicholas Jon, "Analysis of BJT Colpitts sO cillators - Empirical and Mathematical Methods for Predicting Behavior" (2019). Master's Theses (2009 -). 554. https://epublications.marquette.edu/theses_open/554 ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR by Nicholas J. Stave, B.Sc. A Thesis submitted to the Faculty of the Graduate School, Marquette University, in Partial Fulfillment of the Requirements for the Degree of Master of Science Milwaukee, Wisconsin August 2019 ABSTRACT ANALYSIS OF BJT COLPITTS OSCILLATORS – EMPIRICAL AND MATHEMATICAL METHODS FOR PREDICTING BEHAVIOR Nicholas J. Stave, B.Sc. Marquette University, 2019 Oscillator circuits perform two fundamental roles in wireless communication – the local oscillator for frequency shifting and the voltage-controlled oscillator for modulation and detection. The Colpitts oscillator is a common topology used for these applications. Because the oscillator must function as a component of a larger system, the ability to predict and control its output characteristics is necessary. Textbooks treating the circuit often omit analysis of output voltage amplitude and output resistance and the literature on the topic often focuses on gigahertz-frequency chip-based applications. Without extensive component and parasitics information, it is often difficult to make simulation software predictions agree with experimental oscillator results. The oscillator studied in this thesis is the bipolar junction Colpitts oscillator in the common-base configuration and the analysis is primarily experimental. The characteristics considered are output voltage amplitude, output resistance, and sinusoidal purity of the waveform. -

Lec#12: Sine Wave Oscillators

Integrated Technical Education Cluster Banna - At AlAmeeria © Ahmad El J-601-1448 Electronic Principals Lecture #12 Sine wave oscillators Instructor: Dr. Ahmad El-Banna 2015 January Banna Agenda - © Ahmad El Introduction Feedback Oscillators Oscillators with RC Feedback Circuits 1448 Lec#12 , Jan, 2015 Oscillators with LC Feedback Circuits - 601 - J Crystal-Controlled Oscillators 2 INTRODUCTION 3 J-601-1448 , Lec#12 , Jan 2015 © Ahmad El-Banna Banna Introduction - • An oscillator is a circuit that produces a periodic waveform on its output with only the dc supply voltage as an input. © Ahmad El • The output voltage can be either sinusoidal or non sinusoidal, depending on the type of oscillator. • Two major classifications for oscillators are feedback oscillators and relaxation oscillators. o an oscillator converts electrical energy from the dc power supply to periodic waveforms. 1448 Lec#12 , Jan, 2015 - 601 - J 4 FEEDBACK OSCILLATORS FEEDBACK 5 J-601-1448 , Lec#12 , Jan 2015 © Ahmad El-Banna Banna Positive feedback - • Positive feedback is characterized by the condition wherein a portion of the output voltage of an amplifier is fed © Ahmad El back to the input with no net phase shift, resulting in a reinforcement of the output signal. Basic elements of a feedback oscillator. 1448 Lec#12 , Jan, 2015 - 601 - J 6 Banna Conditions for Oscillation - • Two conditions: © Ahmad El 1. The phase shift around the feedback loop must be effectively 0°. 2. The voltage gain, Acl around the closed feedback loop (loop gain) must equal 1 (unity). 1448 Lec#12 , Jan, 2015 - 601 - J 7 Banna Start-Up Conditions - • For oscillation to begin, the voltage gain around the positive feedback loop must be greater than 1 so that the amplitude of the output can build up to a desired level. -

Oscillator Circuits

Oscillator Circuits 1 II. Oscillator Operation For self-sustaining oscillations: • the feedback signal must positive • the overall gain must be equal to one (unity gain) 2 If the feedback signal is not positive or the gain is less than one, then the oscillations will dampen out. If the overall gain is greater than one, then the oscillator will eventually saturate. 3 Types of Oscillator Circuits A. Phase-Shift Oscillator B. Wien Bridge Oscillator C. Tuned Oscillator Circuits D. Crystal Oscillators E. Unijunction Oscillator 4 A. Phase-Shift Oscillator 1 Frequency of the oscillator: f0 = (the frequency where the phase shift is 180º) 2πRC 6 Feedback gain β = 1/[1 – 5α2 –j (6α – α3) ] where α = 1/(2πfRC) Feedback gain at the frequency of the oscillator β = 1 / 29 The amplifier must supply enough gain to compensate for losses. The overall gain must be unity. Thus the gain of the amplifier stage must be greater than 1/β, i.e. A > 29 The RC networks provide the necessary phase shift for a positive feedback. They also determine the frequency of oscillation. 5 Example of a Phase-Shift Oscillator FET Phase-Shift Oscillator 6 Example 1 7 BJT Phase-Shift Oscillator R′ = R − hie RC R h fe > 23 + 29 + 4 R RC 8 Phase-shift oscillator using op-amp 9 B. Wien Bridge Oscillator Vi Vd −Vb Z2 R4 1 1 β = = = − = − R3 R1 C2 V V Z + Z R + R Z R β = 0 ⇒ = + o a 1 2 3 4 1 + 1 3 + 1 R4 R2 C1 Z2 R4 Z2 Z1 , i.e., should have zero phase at the oscillation frequency When R1 = R2 = R and C1 = C2 = C then Z + Z Z 1 2 2 1 R 1 f = , and 3 ≥ 2 So frequency of oscillation is f = 0 0 2πRC R4 2π ()R1C1R2C2 10 Example 2 Calculate the resonant frequency of the Wien bridge oscillator shown above 1 1 f0 = = = 3120.7 Hz 2πRC 2 π(51×103 )(1×10−9 ) 11 C. -

Ultra Low Power RC Oscillator for System Wake-Up Using Highly

Ultra Low Power RC Oscillator for System wake-up using highly precise Auto-Calibration Technique Joonhyung, Lim#1, Kwangmook, Lee#2, Koonsik, Cho#3 # Ubiquitous Conversion Team, Samsung Electro-Mechanics, Suwon, Gyunggi-Do, Korea, 443-743 [email protected], [email protected], [email protected] Abstract— An ultra low power RC oscillator for system wake-up A. The design of RC oscillator is implemented using 0.18um CMOS process. The modern mobile systems need system clock which consumes low power and thus saves limited battery power in order to wake up from sleep-mode. A RC oscillator operates in the subthreshold region to reduce current consumption. The output frequency of RC oscillator is very weakly dependent on process and temperature variation using auto-calibration. This RC oscillator is featured as follows: the current consumption is 0.2 ㎂; the supply voltage is 1.8V; the output frequency is 31.25 KHz with 1.52(Relative 3σ)% accuracy after calibration; it has only 0.4%/℃ temperature coefficient; its size is 190 um x 80 um exclude bonding pad. I. INTRODUCTION Many applications, such as PDA, mobile communication devices need to operate with low power consumption and low supply voltage to fulfil the requirement of long-term operation. For such System-on-Chips (SoCs), embedded a system wake up circuit is necessary [1]. Several analogue and digital blocks such as clock generator, timer and SRAM for retention must be activated to wake system up from a sleep-mode. Especially, a clock generator, which is the heart of digital circuits, will output unknown waveform of clock and the system will enter Fig. -

CLAPPS OSCILLATOR SHUBANGI MAHAJAN Indian Institute of Information Technology, Trichy

CLAPPS OSCILLATOR SHUBANGI MAHAJAN Indian Institute of Information Technology, Trichy INTRODUCTION Clapp oscillator is a variation Of Colpitts oscillator.The circuit differs from the Colpitts oscillator only in one respect; it contains one additional capacitor (C3) connected in series with the inductor. The addition of capacitor (C3) improves the frequency stability and eliminates the effect of transistor parameters and stray capacitances. Apart from the presence of an extra capacitor, all other components and their connections remain similar to that in the case of Colpitts oscillator. Hence, the working of this circuit is almost identical to that of the Colpitts, where the feedback ratio governs the generation and sustainability of the oscillations. However, the frequency of oscillation in the case of Clapp oscillator is given by fo=1/2π√L.C Where C=1/ (1/C1+1/C2+1/C3) Usually, the value of C3 is much smaller than C1 and C2. As a result of this, C is approximately equal to C3. Therefore, the frequency of oscillation, fo=1/2π√L.C3 Usually the value of C3 is chosen to be much smaller than the other two capacitors. Thus the net capacitance governing the circuit will be more dependent on it. A Clapp oscillator is sometimes preferred over a Colpitts oscillator for constructing a variable frequency oscillator. The Clapp oscillators are used in receiver tuning circuits as a frequency oscillator. These oscillators are highly reliable and are hence preferred inspite of having a limited range of frequency of operation. SCHEMATIC DIAGRAM Figure 1: Schematic diagram of clap oscillator NgSpice Plots: Figure 2: Output Plot PYTHON PLOT: Figure 3: output plot REFERENCES • https://www.tutorialspoint.com/sinusoidal_oscillators/sinusoidal_clapp_oscillat or.htm • https://www.electrical4u.com/clapp-oscillator/ . -

Analog IC Design - the Obsolete Book

Analog IC design - the obsolete book Ricardo Erckert July 2021 Contents 1 Preface 7 1.1 Using the book . 7 1.2 If you find mistakes . 8 1.3 Copying . 8 1.4 Warranty and Liability . 8 2 The top level of a chip 8 2.1 How to get the correct data of a chip . 8 2.1.1 Versioning tools . 9 2.2 System on a chip . 11 2.2.1 Where exactly is “ground”? . 12 2.2.2 Signals: If anything can go wrong it will! . 12 2.2.3 Timings . 14 2.3 Top level . 14 2.4 Hierarchy of the chip . 15 2.4.1 Analog on top . 15 2.5 Down at the bottom . 16 2.5.1 Electric . 16 2.5.2 Xcircuit . 17 3 From wafer to chip 18 3.1 Choice of the right substrate . 20 3.1.1 Junction isolated P- substrate . 20 3.1.2 Junction Isolated P+ substrate . 21 3.1.3 Junction isolated N- substrate . 22 3.1.4 Junction isolated N+ substrate . 22 3.1.5 Oxide isolated technology with N-tubs . 23 3.1.6 Oxide isolated technology with P-tubs . 26 3.2 Examples of more complex processes . 26 3.2.1 A bipolar process . 26 3.2.2 A BCD (bipolar, CMOS, DMOS) power process . 27 3.2.3 An isolated (ABCD - advanced BCD) power process . 28 3.2.4 A non volatile memory process . 29 3.2.5 State of the art (2020) digital processes . 29 3.2.6 Programmable chips . 29 4 Components 31 4.1 Wires . -

Hertly Oscillator

Name of Experiment: Construct a Hartley Oscillator and Determine its Frequency of Oscillation. Objectives: After completing this experiment we would able to learn: 1. How a tank circuit operates. 2. How it produces sinusoidal signal. 3. How a Hartley Oscillator operates. History: The Hartley oscillator was invented by Ralph V.L. Hartley while he was working for the Research Laboratory of the Western Electric Company. Hartley invented and patented the design in 1915 while overseeing Bell System's transatlantic radiotelephone tests; it was awarded patent number 1,356,763 on October 26, 1920. Theory: A Hartley oscillator is essentially any configuration that uses two series-connected coils and a single capacitor (see Colpitts oscillator for the equivalent oscillator using two capacitors and one coil). Although there is no requirement for there to be mutual coupling between the two coil segments, the circuit is usually implemented this way. It is made up of the following: • Two inductors in series, which need not be mutual • One tuning capacitor Advantages of the Hartley oscillator include: • The frequency may be adjusted using a single variable capacitor • The output amplitude remains constant over the frequency range • Either a tapped coil or two fixed inductors are needed Disadvantages include; Harmonic-rich content if taken from the amplifier and not directly from the LC circuit The basic LC Oscillator circuit is that they have no means of controlling the amplitude of the oscillations and also, it is difficult to tune the oscillator to the required frequency. If the cumulative electromagnetic coupling between L1 and L2 is too small there would be insufficient feedback and the oscillations would eventually die away to zero. -

RF Oscillators

Islamic University of Gaza Communications Engineering I (Lab.) Faculty of Engineering Prepared by: Electrical Department Eng. Mohammed K. Abu Foul Experiment # (1) RF Oscillators Prelab: 1. Describe the conditions of oscillation that the Colpitts oscillator and Hartley oscillator can operate in a proper way. 2. Try to design a Hartley oscillator as shown in figure 1.9 with 5 MHz output frequency, and then find the values of C3, L1 and L2. 3. Briefly describe the advantages of crystal oscillator. 4. Briefly describe the design concepts of voltage controlled oscillators. Experiment Objectives: 1. To understand the basic theory of oscillators. 2. To design and implement the Colpitts and Hartley oscillators. 3. To design and implement the crystal and voltage controlled oscillators. 4. To understand the measurement and calculation of the output frequency of oscillator. Experiment theory: Nowadays, wireless communication is widely used in and expanded rapidly. Therefore, RF oscillators become one of the important members in wireless communications. The characteristic of oscillator is that it can produce sinusoidal wave or square wave at output terminal without any input signal. So oscillator becomes an important role no matter for modulated signals or carrier signals. In this experiment, we will focus on the theory of feedback oscillators and the design and implementation of different kinds of oscillators. Besides, we can also learn to measure and calculate the output frequency of oscillators in this experiment. 1. The operation theory of oscillators. Figure 1.1 shows the basic block diagram of the oscillator circuit. It includes an amplifier and a resonator, which comprise the positive feedback network. -

Sinusoidal and Non- Sinusoidal Oscillators

CHAPTER65 Learning Objectives ➣ What is an Oscillator? SINUSOIDAL ➣ Classification of Oscillators ➣ Damped and Undamped AND NON- Oscillations ➣ Oscillatory Circuit ➣ Essentials of a Feedback LC SINUSOIDAL Oscillator ➣ Tuned Base Oscillator ➣ Tuned Collector Oscillator OSCILLATORS ➣ Hartley Oscillator ➣ FET Hartley Oscillator ➣ Colpitts Oscillator ➣ Clapp Oscillator ➣ FET Colpitts Oscillator ➣ Crystal Controlled Oscillator ➣ Transistor Pierce Cystal Oscillator ➣ FET Pierce Oscillator ➣ Phase Shift Principle ➣ RC Phase Shift Oscillator ➣ Wien Bridge Oscillator ➣ Pulse Definitions ➣ Basic Requirements of a Sawtooth Generator ➣ UJT Sawtooth Generator ➣ Multivibrators (MV) ➣ Astable Multivibrator An oscillator is an electronic device used for ➣ Bistable Multivibrator (BMV) the purpose of generating a signal. Oscillators ➣ Schmitt Trigger are found in computers, wireless receivers ➣ Transistor Blocking Oscillator and transmitters, and audiofrequency equipment particularly music synthesizers 2408 Electrical Technology 65.1. What is an Oscillator ? An electronic oscillator may be defined in any one of the following four ways : 1. It is a circuit which converts dc energy into ac energy at a very high frequency; 2. It is an electronic source of alternating cur- rent or voltage having sine, square or sawtooth or pulse shapes; 3. It is a circuit which generates an ac output signal without requiring any externally ap- Oscillator plied input signal; 4. It is an unstable amplifier. These definitions exclude electromechanical alternators producing 50 Hz ac power or other devices which convert mechanical or heat energy into electric energy. 65.2. Comparison Between an Amplifier and an Oscillator As discussed in Chapter-10, an amplifier produces an output signal whose waveform is similar to the input signal but whose power level is generally high. -

Oscilators Simplified

SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN SIMPLIFIED WITH 61 PROJECTS DELTON T. HORN TAB BOOKS Inc. Blue Ridge Summit. PA 172 14 FIRST EDITION FIRST PRINTING Copyright O 1987 by TAB BOOKS Inc. Printed in the United States of America Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein. Library of Cangress Cataloging in Publication Data Horn, Delton T. Oscillators simplified, wtth 61 projects. Includes index. 1. Oscillators, Electric. 2, Electronic circuits. I. Title. TK7872.07H67 1987 621.381 5'33 87-13882 ISBN 0-8306-03751 ISBN 0-830628754 (pbk.) Questions regarding the content of this book should be addressed to: Reader Inquiry Branch Editorial Department TAB BOOKS Inc. P.O. Box 40 Blue Ridge Summit, PA 17214 Contents Introduction vii List of Projects viii 1 Oscillators and Signal Generators 1 What Is an Oscillator? - Waveforms - Signal Generators - Relaxatton Oscillators-Feedback Oscillators-Resonance- Applications--Test Equipment 2 Sine Wave Oscillators 32 LC Parallel Resonant Tanks-The Hartfey Oscillator-The Coipltts Oscillator-The Armstrong Oscillator-The TITO Oscillator-The Crystal Oscillator 3 Other Transistor-Based Signal Generators 62 Triangle Wave Generators-Rectangle Wave Generators- Sawtooth Wave Generators-Unusual Waveform Generators 4 UJTS 81 How a UJT Works-The Basic UJT Relaxation Oscillator-Typical Design Exampl&wtooth Wave Generators-Unusual Wave- form Generator 5 Op Amp Circuits