Microprocessors 1 Lecture

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Speed Negotiation Improvement for Hard Disk Drive Serial ATA Interface by Considering Host Compatibility

Speed Negotiation Improvement for Hard Disk Drive Serial ATA Interface by Considering Host Compatibility by Apisak Srihamat A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Microelectronics and Embedded Systems Examination Committee: Dr.Mongkol Ekpanyapong (Chairperson) Dr.Metthew N. Dailey Mak Chee Wai (External Expert) Nationality: Thai Previous Degree: Bachelor in Computer Engineering King Mongkut’s Institute of Technology, Ladkrabang, Thailand Scholarship Donor: Western Digital – AIT Fellowship Asian Institute of Technology School of Engineering and Technology Thailand December 2014 ACKNOWLEDGEMENTS First of all, I would like to thankful to Dr. Mongkol Ekpanyapong and Dr. Matthew N. Dailey who gave a very good guidance and support encouraged me to study and understand the objective, scope and limitations of this thesis. Then continue provide technical discussion to make me have clearer picture. I’m heartily thankful to Dr.Matthew N. Dailey, Dr.Manukid Parnichkun, and Dr.Metha Jeeradit who gave a very good suggestion during I study in AIT. I also would like to show my gratitude to Western Digital who gives me a time, support and job while I am studying master degree. Special appreciation goes to my supervisor at work, Mr. Petrus Hu, shouldering some of the responsibilities on my behalf in order to allow time for me to be away to complete my Masters study. The person I cannot forget, Mr. Mak Chee Wai as the external expert on the committee panel. He provided invaluable feedback, constant encouragement and support during my Masters study. I would like to thanks to my parents and family, who understand and allowed me to have extra time to work on this thesis. -

The System Bus

ELEC 379 : DESIGN OF DIGITAL AND MICROCOMPUTER SYSTEMS 1998/99 WINTER SESSION, TERM 1 The System Bus This lecture describes system buses. These are buses used to interface the CPU with memory and peripherals on separate PC cards. The ISA and PCI buses are used as examples. Introduction characteristics. We will look briefly at two examples of system To increase their flexibility, most general-purpose buses. The ISA (Industrial Standard Architecture) microcomputers include a system bus that allows bus is commonly used in IBM-PC compatibles and printed circuit boards (PCBs) containing memory or is one of the most widely-used system busses. The I/O devices to be connected to the CPU. This allows PCI (Peripheral Component Interconnect) bus is a microcomputer systems to be customized for differ- flexible high-performance peripheral bus that can ef- ent applications. The use of a standard bus also al- ficiently interconnect peripherals and processors of lows manufacturers to produce peripherals that will widely different speeds. work properly with other manufacturers’ computer systems. The system bus consists of a number of parallel Mechanical Characteristics conductors on a backplane or motherboard. There are a number of connectors or “slots” into which Low-cost consumer-grade buses use card-edge con- other PCBs containing memory and I/O devices can nectors to minimize the cost of the peripheral. The be plugged in. plug-in card has contact pads along the edges of the PCB. The motherboard has connectors on the moth- In most cases the system bus is very similar to the erboard that contact these pads. -

Firewire™ Reference Tutorial (An Informational Guide) January 22

FireWire™ Reference Tutorial (An Informational Guide) January 22, 2010 Abstract This document is a FireWire tutorial aimed at engineers that have no previous exposure or understanding of FireWire. Its purpose is to familiarize the reader with FireWire and to build a sound and complete understanding of how the FireWire bus operates from the experiences of expert members of the 1394 Trade Association. 1394 Trade Association Specifications, Tutorials and Guides are developed within 1394 Trade Working Groups of the 1394 Trade Association, a non-profit industry association devoted Association to the promotion of and growth of the market for IEEE 1394-compliant products. Participants in Working Groups serve voluntarily and without compensation from the Specification Trade Association. Most participants represent member organizations of the 1394 Trade Association. The work product developed within these working groups represent a consensus of the expertise represented by the participants. Use of a 1394 Trade Association document is wholly voluntary. The existence of a 1394 Trade Association document is not meant to imply that there are not other ways to produce, test, measure, purchase, market or provide other goods and services related to the scope of the 1394 Trade Association Specification. Furthermore, the viewpoint expressed at the time a document is accepted and issued is subject to change brought about through developments in the state of the art and comments received from users of the specification. Users are cautioned to check to determine that they have the latest revision of any 1394 Trade Association document. Comments for revision of 1394 Trade Association Documents are welcome from any interested party, regardless of membership affiliation with the 1394 Trade Association. -

(12) United States Patent (10) Patent No.: US 6,513,079 B1 Day (45) Date of Patent: Jan

USOO6513079B1 (12) United States Patent (10) Patent No.: US 6,513,079 B1 Day (45) Date of Patent: Jan. 28, 2003 (54) AUTOMATIC NEXUS RESTORE (56) References Cited (75) Inventor: Brian A. Day, Colorado Springs, CO U.S. PATENT DOCUMENTS (US) 5,276,662 A * 1/1994 Shaver, Jr. et al. 5.835,742 A * 11/1998 James et al. (73) Assignee: LSI Logic Corporation, Milpitas, CA 6,223,235 B1 * 4/2001 Cheng (US) * cited bwy examiner (*) Notice: Subject to any disclaimer, the term of this Primary Examiner-Gopal C. Ray patent is extended or adjusted under 35 (74) Attorney, Agent, or Firm-Carstens, Yee & Cahoon U.S.C. 154(b) by 0 days. LLP (57) ABSTRACT (21) Appl. No.: 09/991,063 When a specific pair of devices are Selected or reselected for (22) Filed: Nov. 21, 2001 communications acroSS a SCSI bus, a hardware State 7 machine in each device restores the communication param (51) Int. Cl." .......................... G06F 13/00; G06F 13/38 eters that have been previously negotiated for this pair of (52) -rr. 710/104; 710/313; 711/4 devices. This prevents the devices from wasting bus time for (58) Field of Search ................................ 710/1, 22, 33, the restoration. 710/104, 305,313; 711/4, 112: 365/50, 230.01; 369/176; 714/16 15 Claims, 3 Drawing Sheets SCSI Host Adapter (Device 1) 302 U.S. Patent Jan. 28, 2003 Sheet 1 of 3 US 6513,079 B1 Figure 1 - - - - - 106 |ROC - - inI r - 104 Host/ PC Cache? Audio Bridge Adapter 216 BuS 206 LAN Expansion Graphics Audio/Video SCSI Host BuS Adapter Bus Adapter Adapter Adapter 210 Interface 118 119 212 Keyboard Modem Memory and Mouse 222 224 Disk Tape CD-ROM Adapter 226 228 230 220 U.S. -

PCI (Peripheral Component Interconnect) VESA Local Bus

PCI (Peripheral Component Interconnect) PCI is an interconnection system between a microprocessor and attached devices in which expansion slots are spaced closely for high speed operation. Using PCI, a computer can support both new PCI cards while continuing to support ISA expansion cards, currently the most common kind of expansion card. Designed by Intel, the original PCI was similar to the VESA Local Bus. However, PCI 2.0 is no longer a local bus and is designed to be independent of microprocessor design. PCI is designed to be synchronized with the clock speed of the microprocessor, in the range of 20 to 33 Mhz. PCI is now installed on most new desktop computers, not only those based on Intel's Pentium processor but also those based on the PowerPC. PCI transmits 32 bits at a time in a 124-pin connection (the extra pins are for power supply and grounding) and 64 bits in a 188-pin connection in an expanded implementation. PCI uses all active paths to transmit both address and data signals, sending the address on one clock cycle and data on the next. Burst data can be sent starting with an address on the first cycle and a sequence of data transmissions on a certain number of successive cycles. VESA Local Bus (Video Electronics Standards Association Local Bus) VESA Local Bus (sometimes called the VESA VL bus) is a standard interface between your computer and its expansion slots that provides faster data flow between the devices controlled by the expansion cards and your computer's microprocessor. A "local bus" is a physical path on which data flows at almost the speed of the microprocessor, increasing total system performance. -

Spacecraft Interface Standards Analysis and Simple Breadboarding

Examensarbete LITH-ITN-ED-EX--05/003--SE Spacecraft Interface Standards Analysis and Simple Breadboarding Birgitta Ljunggren 2005-03-14 Department of Science and Technology Institutionen för teknik och naturvetenskap Linköpings Universitet Linköpings Universitet SE-601 74 Norrköping, Sweden 601 74 Norrköping LITH-ITN-ED-EX--05/003--SE Spacecraft Interface Standards Analysis and Simple Breadboarding Examensarbete utfört i Elektronikdesign vid Linköpings Tekniska Högskola, Campus Norrköping Birgitta Ljunggren Handledare Hans-Jakob Schneider Examinator Shaofang Gong Norrköping 2005-03-14 Datum Avdelning, Institution Date Division, Department Institutionen för teknik och naturvetenskap 2005-03-14 Department of Science and Technology Språk Rapporttyp ISBN Language Report category _____________________________________________________ Svenska/Swedish Examensarbete ISRN LITH-ITN-ED-EX--05/003--SE x Engelska/English B-uppsats _________________________________________________________________ C-uppsats Serietitel och serienummer ISSN x D-uppsats Title of series, numbering ___________________________________ _ ________________ _ ________________ URL för elektronisk version http://www.ep.liu.se/exjobb/itn/2005ed/003/ Titel Title Spacecraft Interface Standards Analysis and Simple Breadboarding Författare Author Birgitta Ljunggren Sammanfattning Abstract I detta examensarbete undersöks 12 olika data kommunikationsstandarder mellan vilka det också görs en jämförelse. Jämförelsen mål är att få reda på vilken eller vilka av standarderna som är bäst lämpade -

Universal Serial Bus Specification

Universal Serial Bus Specification Compaq Digital Equipment Corporation IBM PC Company Intel Microsoft NEC Northern Telecom Revision 1.0 January 15, 1996 Universal Serial Bus Specification Revision 1.0 Scope of this Revision The 1.0 revision of the specification is intended for product design. Every attempt has been made to ensure a consistent and implementable specification. Implementations should ensure compliance with this revision. Revision History Revision Issue Date Comments 0.7 November 11, 1994 Supersedes 0.6e. 0.8 December 30, 1994 Revisions to Chapters 3-8, 10, and 11. Added appendixes. 0.9 April 13, 1995 Revisions to all the chapters. 0.99 August 25, 1995 Revisions to all the chapters. 1.0 FDR November 13, 1995 Revisions to Chapters 1, 2, 5-11. 1.0 January 15, 1996 Edits to Chapters 5, 6, 7, 8, 9, 10, and 11 for consistency. Proposal for Universal Serial Bus Specification Copyright © 1996, Compaq Computer Corporation, Digital Equipment Corporation, IBM PC Company, Intel Corporation, Microsoft Corporation, NEC, Northern Telecom. All rights reserved. INTELLECTUAL PROPERTY DISCLAIMER THIS SPECIFICATION IS PROVIDED “AS IS” WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. A LICENSE IS HEREBY GRANTED TO REPRODUCE AND DISTRIBUTE THIS SPECIFICATION FOR INTERNAL USE ONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY OTHER INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED HEREBY. AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. -

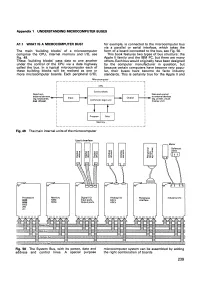

I I I I I I I Memo~ I L ~

Appendix 1 UNDERSTANDING MICROCOMPUTER BUSES A1.1 WHAT IS A MICROCOMPUTER BUS? for example, is connected to the microcomputer bus via a parallel or serial interface, which takes the The main 'building blocks' of a microcomputer form of a board connected to the bus, see Fig. 50. comprise the CPU, internal memory and I/O, see This book features two types of bus structure: the Fig. 49. Apple II family and the IBM PC, but there are many These 'building blocks' pass data to one another others. Each bus would originally have been designed under the control of the CPU via a data highway by the computer manufacturer in question, but called the bus. In a typical microcomputer each of because certain computers have become very popu these building blocks will be realised as one or lar, their buses have become de facto industry more microcomputer boards. Each peripheral (I/O), standards. This is certainly true for the Apple II and Microcomputer 1---------------------------, I CPU I I I I Control block I Data from Data and control external devices I I to external devices (eg. keyboards, (eg. printer, visual disk drives) I display unit) I I I I I I I Memo~ I L ~ Fig.49 The main internal units of the microcomputer User's Interface Motor Solenoid C)CI) o~ valve -Q)co> ~~ Processors Memo~ Digital 110 Analog 110 Peripheral Industrial 1/0 8088 RAM Input ports DACs interface 8086 ROM Output ports ADCs 6502 280 etc. Fig. 50 The System Bus, with its power, data and microcomputer system can be assembled by adding address and control lines. -

Part-34-Pci-And-Scsi-Buses.Pdf

University of Pune S.E. I.T. Subject code: 214442 Computer Organization Part 34 : PCI and SCSI Buses UNIT V Tushar B. Kute, Department of Information Technology, Sandip Institute of Technology & Research Centre, Nashik. http://tusharkute.com Standard I/O Interfaces Traditional (ISA) (with cache) High Performance Bus PCI Bus Peripheral Component Interconnect In early 1992, the Intel formed an another industrial group in relation to the PC bus. The main objective behind the formation of the group was to overcome the weakness in ISA and EISA buses. They designed the PCI specifications in June 1992 and updated in April 1993. Features Requires very few chips to implement. Uses the system bus to increase the bus clock speed. Ability to function with 64-bit data bus. High bandwidth, 33 MHz. Support of single and multiprocessor systems. Operate concurrently with the processor bus. Function as mezzanine or peripheral bus. Synchronous timings. Better system performance for high speed I/O subsystems such as AGP, NIC, disk controllers. Plug and Play. PCI in single processor system PCI in multi processor system PCI Connector PCI Bus Lines (required) Systems lines Including clock and reset Address & Data 32 time mux lines for address/data Interrupt & validate lines Interface Control Arbitration Not shared Direct connection to PCI bus arbiter Error lines PCI Bus Lines (Optional) Interrupt lines Not shared Cache support 64-bit Bus Extension Additional 32 lines Time multiplexed 2 lines to enable devices to agree to use 64-bit transfer JTAG/Boundary Scan For testing procedures PCI Commands Transaction between initiator (master) and target Master claims bus Determine type of transaction e.g. -

Universal Serial Bus Specification

Universal Serial Bus Specification Compaq Intel Microsoft NEC Revision 1.1 September 23, 1998 Universal Serial Bus Specification Revision 1.1 Scope of this Revision The 1.1 revision of the specification is intended for product design. Every attempt has been made to ensure a consistent and implementable specification. Implementations should ensure compliance with this revision. Revision History Revision Issue Date Comments 0.7 November 11, 1994 Supersedes 0.6e. 0.8 December 30, 1994 Revisions to Chapters 3-8, 10, and 11. Added appendixes. 0.9 April 13, 1995 Revisions to all the chapters. 0.99 August 25, 1995 Revisions to all the chapters. 1.0 FDR November 13, 1995 Revisions to Chapters 1, 2, 5-11. 1.0 January 15, 1996 Edits to Chapters 5, 6, 7, 8, 9, 10, and 11 for consistency. 1.1 September 23, 1998 Updates to all chapters to fix problems identified. Universal Serial Bus Specification Copyright © 1998, Compaq Computer Corporation, Intel Corporation, Microsoft Corporation, NEC Corporation. All rights reserved. INTELLECTUAL PROPERTY DISCLAIMER THIS SPECIFICATION IS PROVIDED “AS IS” WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. A LICENSE IS HEREBY GRANTED TO REPRODUCE AND DISTRIBUTE THIS SPECIFICATION FOR INTERNAL USE ONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY OTHER INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED HEREBY. AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. -

The I/O Subsystem Chapter Seven

The I/O Subsystem Chapter Seven 7.1 Chapter Overview A typical program does three basic activities: input, computation, and output. In this section we will discuss the other two activities beyond computation: input and output or I/O. This chapter concentrates on low-level CPU I/O rather than high level file or character I/O. This chapter discusses how the CPU transfers bytes of data to and from the outside world. This chapter discusses the mechanisms and performance issues behind the I/O. 7.2 Connecting a CPU to the Outside World Most I/O devices interface to the CPU in a fashion quite similar to memory. Indeed, many devices appear to the CPU as though they were memory devices. To output data to the outside world the CPU simply stores data into a "memory" location and the data magically appears on some connectors external to the computer. Simi- larly, to input data from some external device, the CPU simply transfers data from a "memory" location into the CPU; this "memory" location holds the value found on the pins of some external connector. An output port is a device that looks like a memory cell to the computer but contains connections to the out- side world. An I/O port typically uses a latch rather than a flip-flop to implement the memory cell. When the CPU writes to the address associated with the latch, the latch device captures the data and makes it available on a set of wires external to the CPU and memory system (see Figure 7.1).