Altivec Vector Processor, Part 2: Enhancements

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

CPU ボードカタログ サポート CPU Intel :Core I7、Xeon-E5 Freescale :T4240、P4080、MPC8640D AMD :Radeon HD 6970M、HD 7970M GPGPU NVIDIA :Fermi、Kepler Architecture GPGPU

組込みシステム向け CPU ボードカタログ サポート CPU Intel :Core i7、Xeon-E5 Freescale :T4240、P4080、MPC8640D AMD :Radeon HD 6970M、HD 7970M GPGPU NVIDIA :Fermi、Kepler Architecture GPGPU サポートバス規格 OpenVPX VME/VXS CompactPCI PMC/XMC ATCA/AMC PCI Express 403102 Ⓒ MISH International Co., Ltd. MISH International Co., Ltd. ミッシュインターナショナルでは CPU ボードをスピーディに 導入頂けますよう、次のような サービスを提供しております CPU ボードのお貸出しサービス CPU ボードの性能評価検証サービス ミッシュインターナショナルでは、ユーザが実際に製品を導入する前に性能評価を実施していただけ ミッシュインターナショナルでは、専門の CPU ボードサポート技術者がお客様のご要望に応じて CPU ますよう各種評価用 CPU ボードをお貸出ししています。お貸出し時には、リアルタイム OS を含めた ボードの性能を評価・検証させていただきます。たとえばFFT の処理速度やボード間のデータ転送スピー CPU ボードに関するトータルな技術サポートを行っております。 ドの測定などユーザがシステムインテグレーションする上で必要なデータを検証の上、レポートさせて いただきます。(お客様のご要望内容によっては別途有償の場合もあります) CPU ボードの技術サポート ミッシュインターナショナルでは、専門のCPU ボードサポート技術者が導入前はもちろん、導入後もハー ド・ソフトの両面からお客様の技術サポートをいたします。CPU ボードのドライバソフトウェアやアプ リケーションの開発方法等をトータルにバックアップいたします。また、リアルタイム OS を含んだシ CPU ボード用フレームワークソフトウェアの開発サービス ステムインテグレーッションに関するアドバイスも対応しています。 CPU ボードを含んだ組込み用システムを構 築する上では、CPU ボードのハード・ソフ トに関する技術的な知識経験はもちろんです が、CPU ボード以外の A/D、D/A、DIO ボー ド等の各種 I/O ボードとのシームレスな高速 データ通信やリアルタイム OS を使用したイ ンテグレーションが必要です。当社では複数 のボードを使ったマルチ CPU ボードシステ ムやレーダ、ソナー、移動体通信等の無線信 号のリアルタイム処理等をトータルにサポートしています。全体的なデータのパスをサポートした『フ レームワークソフトウェア』の開発もお手伝いしています。ユーザは『フレームワークソフトウェア』 の開発を当社へ外注することにより、アプリケーションソフトウェアの開発や FPGA の開発に専念する ことが出来ます。(お客様のご要望内容によっては別途有償の場合もあります) インテル製 プロセッサ搭載 CPU ボード ボード CPU スピード 拡張 USB 耐環境 型名 プロセッサ メモリ NVRAM Ethernet インテル製 プロセッサ Core i7(Ivy Bridge)、 タイプ (Max) メザニン 2.0 仕様 Xeon E5-2648L x 2 32GB DDR3- 8MB NOR 1000BASE-T x 1 Level HDS6601 6U VPX 1.8GHz - 3 Xeon(8 Core) 搭載 CPU ボード (Sandy Bridge) -

Abaco Systems / SBS CM6 Series Datasheet

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the Abaco Systems / SBS CTM19 at our website: Click HERE DATASHEET CM6 PowerPC® MPC 8641D 3U CompactPCI™ Embedded Computer The CM6 is a 3U CompactPCI CPU board are addressed with an optional extended with integrated dual core or single core temperature range of -40 °C to +85 °C and FEATURES: Freescale MPC8641 processor. The conformal coating. Shock and vibration • Freescale™ PowerPC® MPC8641 MPC8641D follows the system on a chip immunity is designed in with stiffener bars, in single or dual core with approach by integrating the memory wedge locks and conduction cooling. AltiVec™ controller, Ethernet channels, PCI Express as • Freescale 8640/8640D ready well as UARTs and timers. The CM6 provides a unique feature set, including up to 1 Gbyte of DDR2 SDRAM • Up to 1333 MHz The processor includes one or two execution with ECC, system and non-system mode • Integrated 64 Kbyte L1 and 1 cores in a single processor case, each core support for the CPCI backplane, one PMC Mbyte L2 cache per core with its own L1 and L2 cache including interface (64-bit/100 MHz). -

Qoriq: High End Industrial and Networking Processing

TM TechDays 2013 Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorIQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MagniV, MXC, Platform in a Package, Processor Expert, QorIQ Qonverge, Qorivva, QUICC Engine, Ready Play, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, VortiQa and Xtrinsic are PowerQUICC, QorIQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, trademarks of Freescale Semiconductor, Inc. All other product or service names are the BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MagniV, MXC, Platform in a Package, Processor Expert, QorIQ Qonverge, Qorivva, QUICC Engine, TM property of their respective owners. © 2012 Freescale Semiconductor, Inc. 1 Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All . other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc. 2013 2011 QorIQ Qonverge QorIQ next-generation platform launch platform based T series 28nm on Layerscape architecture 2008 QorIQ Multicore Platform launch (P series) Accelerating the P series 45nm Network’s IQ 2004 Dual-core -

SEWIP Program Leverages COTS P 36 P 28 an Interview with Deon Viergutz, Vice President of Cyber Solutions at Lockheed Martin Information Systems & Global Solutions

@military_cots John McHale Obsolescence trends 8 Special Report Shipboard displays 44 Mil Tech Trends Predictive analytics 52 Industry Spotlight Aging avionics software 56 MIL-EMBEDDED.COM September 2015 | Volume 11 | Number 6 RESOURCE GUIDE 2015 P 62 Navy SEWIP program leverages COTS P 36 P 28 An interview with Deon Viergutz, Vice President of Cyber Solutions at Lockheed Martin Information Systems & Global Solutions Military electronics market overview P 14 Volume 11 Number 6 www.mil-embedded.com September 2015 COLUMNS BONUS – MARKET OVERVIEW Editor’s Perspective 14 C4ISR funding a bright spot in military 8 Tech mergers & military electronics electronics market obsolescence By John McHale, Editorial Director By John McHale Q&A EXECUTIVE OUTLOOK Field Intelligence 10 Metadata: When target video 28 Defending DoD from cyberattacks, getting to data is not enough the left of the boom By Charlotte Adams 14 An interview with Deon Viergutz, Vice President of Cyber Solutions at Lockheed Martin Information Mil Tech Insider Systems & Global Solutions 12 Broadwell chip boosts GPU performance for COTS SBCs 32 RF and microwave innovation drives military By Aaron Frank radar and electronic warfare applications An interview with Bryan Goldstein, DEPARTMENTS General Manager of the Aerospace and Defense, Analog Devices 22 Defense Tech Wire By Mariana Iriarte SPECIAL REPORT 60 Editor’s Choice Products Shipboard Electronics 112 University Update 36 U.S. Navy’s electronic warfare modernization On DARPA’s cybersecurity radar: 36 effort centers on COTS Algorithmic and side-channel attacks By Sally Cole, Senior Editor By Sally Cole 114 Connecting with Mil Embedded 44 Key to military display technologies: Blog – The fascinating world of System integration By Tom Whinfrey, IEE Inc. -

Embedded Computing Product Guide Our Customers Operate in Many Diverse Markets

Embedded Computing for Business-Critical Continuity™ Embedded Computing Product Guide Our customers operate in many diverse markets. What unites them is a need to work with a company that has an outstanding record as a reliable supplier. That’s Emerson Network Power. That’s the critical difference. The Embedded Computing business of Emerson Network Power enables original equipment manufacturers and systems integrators to develop better products quickly, cost effectively and with less risk. Emerson is a recognized leading provider of embedded computing solutions ranging from application-ready platforms, embedded PCs, enclosures, motherboards, blades and modules to enabling software and professional services. For nearly 30 years, we have led the ecosystem required to enable new technologies to succeed including defining open specifications and driving industry-wide interoperability. This makes your integration process straightforward and allows you to quickly and easily build systems that meet your application needs. Emerson’s engineering and technical support is backed by world-class manufacturing that can significantly reduce Table of Contents your time-to-market and help you gain a clear competitive edge. And, as part of Emerson, the Embedded Computing 4 AdvancedTCA Products business has strong financial credentials. 9 Commercial ATCA Products Let Emerson help you improve time-to-market and shift 10 Motherboard & COM Products your development efforts to the deployment of new, 14 RapiDex™ Board Customization value-add features and services that create competitive 15 OpenVPX Products advantage and build market share. With Emerson behind you, anything is possible. 16 VME Products 18 CompactPCI Products 20 Solution Services 21 Innovation Partnership Program 22 Terms & Conditions 2 Our leadership and heritage includes embedded computing solutions for military, aerospace, government, medical, automation, industrial and telecommunications applications. -

Dual-Core ARM Cortex-A7 • 2 X ARM Cortex A7 Cpus, up to 1.0Ghz

Технологии QNX и КПДА в России Москва, 13 апреля 2017 Микропроцессоры NXP c с поддержкой технологий QNX для промышленных, сетевых, автомобильных приложений. Семейства QorIQ, i.MX и S32V. Александр Акименко, Группа компаний Симметрон Программа презентации • i.MX 6QuadPlus/6DualPlus – флагман линейки i.MX • i.MX 7 – энергоэффективное решение для IoT • Анонс процессоров i.MX 8 – взгляд в будущее линейки i.MX • LS1012A – самый маленький и самый энергоэффективный 64- битный процессор • LS1020A/21A/22A – двухъядерные процессоры с широким набором периферии для IoT и промышленных приложений • LS1023A/43A – 64-разрядные процессоры с поддержкой 10Gbps Ethernet • S32V – процессоры для реализации функций ADAS в автомобильной электронике 1 i.MX 6QuadPlus/6DualPlus (upgraded i.MX 6Quad/6Dual) QNX SDP 7.0 Specifications: BSP available • CPU: i.MX 6QuadPlus: 4x Cortex-A9 @ 800MHz/852MHz/1GHz/1.2GHz i.MX 6DualPlus: 2x Cortex-A9 @ 800MHz/852MHz/1GHz/1.2GHz • Process: 40nm • Package: 21x21 0.8mm Flip-chip BGA • Temp Range (Tj): • Auto -40 to 125C • Industrial -40 to 105C • Extended Commercial -20 to 105C • Qual Tiers: Commercial, Automotive, Industrial • Pin compatible with i.MX 6Quad and i.MX 6Dual • Up to 10,000 DMIPS 2 i.MX Processor Roadmap 6QuadPlus i.MX 8 family 6Quad Advanced Graphics and Performance ARM ® v8-A (32-bit/ 64-bit) 6DualPlus i.MX 8M family pin Compatible pin 6Dual - Advanced Audio and Video to - ARM ® v8-A 6DualLite (32-bit/ 64-bit) Pin 6Solo i.MX 8X family Safety Critical & Efficient Performance 6SoloX ® ARM v8-A (32-bit/ 64-bit) Software Compatible Software 6SoloLite 6UltraLite i.MX 7 Power Efficiency & BOM Cost Optimizations ® 6ULL ARM v7-A (32-bit) ® ARM v7-A 3 i.MX 7Dual/7Solo QNX SDP 7.0 BSP Specifications: available . -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

Freescale Qoriq P4080 DMA-DDR Performance Analysis

TM Wai Chee Wong Sr.Member of Technical Staff Freescale Semiconductor Raghu Binnamangalam Sr.Technical Marketing Engineer Cadence Design Systems Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, t he Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorIQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, QorIQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc. DAC 2013, Austin, TX • Company Overview • Use of emulation at Freescale • Palladium usage for emulation model under test • Performance case studies • Experiences using Palladium system • Summary Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorIQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a TM 2 Package, Processor Expert, QorIQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc. • Global leader in embedded -

Vybrid Controllers Technical Overview

TM June 2013 Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C- Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, Qorivva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorIQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc. • Overview of Vybrid Family • Vybrid Tower Board • Vybrid System Modules • QuadSPI Flash • Vybrid Clock System • Vybrid Power System • Vybrid Boot Operation • High Assurance Boot • Vybrid Trusted Execution • LinuxLink and MQX Embedded Software • DS-5 compiler TM Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, Qorivva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. 2 Airfast, BeeKit, BeeStack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorIQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc. TM Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C- Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, Qorivva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. -

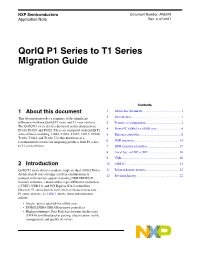

AN5079, Qoriq P1 Series to T1 Series Migration Guide

NXP Semiconductors Document Number: AN5079 Application Note Rev. 0, 07/2017 QorIQ P1 Series to T1 Series Migration Guide Contents 1 About this document 1 About this document............................................... 1 This document provides a summary of the significant 2 Introduction.............................. .............................. 1 differences between QorIQ P1 series and T1 series devices. 3 Feature-set comparison................... ........................2 The QorIQ P1 series devices discussed in this document are P1010, P1020, and P1022. These are compared with QorIQ T1 4 PowerPC e500v2 vs e5500 core..............................4 series devices including T1024, T1014, T1023, T1013, T1040, 5 Ethernet controller...................................................8 T1020, T1042, and T1022. Use this document as a recommended resource for migrating products from P1 series 6 POR sequence....................................................... 14 to T1 series devices. 7 DDR memory controller................ .......................17 8 Local bus - eLBC vs IFC...................................... 18 9 USB.......................................................................20 2 Introduction 10 eSDHC...................................................................21 QorIQ P1 series devices combine single or dual e500v2 Power 11 Related documentation..........................................22 Architecture® core offering excellent combinations of 12 Revision history.................................................... 22 protocol -

Power Architecture® Roadmap

TM Nikolay Guenov Rich Schnur Matt Short NPD June 2012 Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorIQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MagniV, MXC, Platform in a Package, Processor Expert, QorIQ Qonverge, Qorivva, QUICC Engine, Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc. Overview • QorIQ Portfolio Overview • Market Overview • Roadmap • What’s new? (P5040, T2080, T1040) • Announcing our next generation networking architecture • Enablement Product Deep Dive • P5040/P5021 • T4240 • T2080 • T1042 The Next Generation – Initial Products Summary Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorIQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MagniV, MXC, Platform in a Package, Processor Expert, QorIQ Qonverge, Qorivva, QUICC Engine, TM 2 Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service -

® OS-9 RTOS for Power PC Based Systems Deterministic - Efficient - Scalable - Fast Booting

MICROWARE® RTOS OS-9 for Power PC based systems Deterministic - Efficient - Scalable - Fast Booting Embedded systems span a myriad of applications, . High availability - OS-9 has the ability to add, ranging from simple microcontrollers to sophisticated remove, and replace individual components in medical imaging systems to complex industrial the system while on-line and in-use. This results applications. At the heart of these diverse applications in a high degree of system availability, even is an operating system (OS) - a software foundation during maintenance. Proven over 30 years in that delivers a common set of services helping mission critical devices around the world. software developers deliver their product to market more quickly. Enter Microware OS‐9, the high‐ performance, high‐availability real‐time operating system platform from MicroSys. The Microware OS‐9 RTOS has been deployed and proven in thousands of products worldwide and represented hundreds of embedded applications, including industrial automation and control and automotive and medical instrumentation. WHY MICROWARE OS-9 Microware OS-9 compact, high- performance multi-user, multi- tasking real-time kernel is a proven foundation for time-to-revenue success. OS-9 is a full-featured operating system framework, . Hard Real-Time Performance - Unlike Windows including the OS kernel, kernel services, and industry- and Linux-based systems, Microware OS-9 was standard APIs, middleware, and a complete IDE-based conceived from the ground up to meet the development framework. high-performance and reliability requirements of time-critical embedded applications. REDUCE RISK FAST BOOTING . High reliability - the OS-9 secure process model, real-time operating system (RTOS) provides .