Interview with Steve Swanson

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Jim Handy Jim.Handy(At)Objective-Analysis.Com PO Box 440, Los Gatos, CA 95031-0440, USA +1 (408) 356-2549

Jim Handy Jim.Handy(at)Objective-Analysis.com PO Box 440, Los Gatos, CA 95031-0440, USA +1 (408) 356-2549 Experience Experienced in Trial & Deposition Testimony, Expert Reports, etc. Highly published and widely quoted as a key semiconductor industry analyst. 37-year semiconductor industry veteran. Honorary Member: Storage Networking Industry Association (SNIA) Deep technical understanding and design background. Highly analytical. Excellent communications skills: oral, written, and presentation. Author of key reference design work: “The Cache Memory Book” Harcourt Brace, 1993 Patent holder in cache memory design Expert Experience Trial Testimony In Re: Spansion et al Federal Bankruptcy Court of Delaware Docket No: 09-10690, (Hon. Kenneth Carey). 11/30/09 Netlist, Inc. (Plaintiff) vs. Diablo Technologies, Inc. (Defendant), US District Court, Northern District of CA, Case No. 13-CV-05962 YGR, (Hon. Yvonne Gonzalez Rogers), 3/13/15 Deposition Testimony In Re: Spansion et al Federal Bankruptcy Court of Delaware Docket No: 09-10690, (Hon. Kenneth Carey). 11/24/09 In Re: SRAM, 07-CV-1819-CW (N.D. Cal.), 3/25/10 Expert Reports Expert Rebuttal Report - In Re: Spansion et al Federal Bankruptcy Court of Delaware Docket No: 09-10690, (Hon. Kenneth Carey). 11/20/09 (8 pages) Expert Report - In Re: SRAM, 07-CV-1819-CW (N.D. Cal.), 1/25/10 (13 pages) Expert Report - In Re: Qimonda Richmond, LLC, et al., Case No. 09-10589 (MFW) 2/6/12 (30 pages) Expert Report - Netlist, Inc. (Plaintiff) vs. Diablo Technologies, Inc. (Defendant), US District Court, Northern District of CA, Case No. 13-CV-05962 YGR, (Hon. -

IDC Vendor Profile Of

VENDOR PROFILE SVP.11: Texas Memory Systems Delivering on the SSD Promise Jeff Janukowicz IDC OPINION The solid state drive (SSD) market is full of activity, with companies large and small announcing products that carry a promise of impressive performance gains, low power consumption, and cost-effective solutions when compared with the 50-year-old mechanical hard disk drive (HDD). Yet, for one company, Texas Memory Systems (TMS), with over 30 years of experience and 15 generations of SSD products, delivering on the promise of SSDs is nothing new. For some companies, they are just entering the SSD market by announcing their intentions or partners and realizing revenue is still a future event. TMS, on the other hand, is growing its RamSan SSD business with sales to end users through OEM, reseller, and direct channels and has positioned itself well within what IDC believes is a fast-growing market. TMS specializes in providing low-latency, high-bandwidth, I/O-intensive storage systems. TMS strengths include: Solid engineering focus. SSDs are advanced storage solutions that require both innovation and detailed knowledge to integrate solid state memory, memory management, controllers, and backplanes into a storage system without sacrificing performance. TMS does most of its engineering internally. Over 50% of its employees are engineers with an average of 5+ years of software experience and 10+ years of hardware experience at TMS designing SSD solutions for enterprise customers. This level of technical expertise is vital to deliver on the promise of SSDs, to iterate products rapidly in a competitive marketplace and, perhaps most important, to support enterprise customers. -

Your Guide to All-Flash Storage, How It Stacks up Against Hybrid and Pcie, and How to Measure the Benefits

All-Flash: The Essential Guide All-Flash: The Essential Guide Your guide to all-flash storage, how it stacks up against hybrid and PCIe, and how to measure the benefits All-Flash: The Essential Guide In this e-guide In this e-guide: All-flash array roundup 2016: Computer Weekly keeps its finger on the pulse in the world of The big six data storage, with regular news, features and practical articles. This guide offers a comprehensive survey of the all- All-flash storage roundup flash array market. We look at all-flash products from the big 2016: The startups six storage vendors and the startups and specialists. Plus, we give the lowdown on all-flash vs hybrid flash arrays and all- Hybrid flash vs all-flash storage: When is some flash flash vs server-side PCIe SSD. Finally, we look at the not enough? shortcomings of measuring the value of flash by metrics designed for spinning disk and suggest practical alternatives. PCIe SSD vs all-flash for enterprise storage How to measure flash storage's true value Antony Adshead, Storage editor Page 1 of 32 All-Flash: The Essential Guide In this e-guide All-flash array roundup 2016: The big six All-flash array roundup 2016: Chris Evans, Contributor The big six In all-flash storage 2015 was year of consolidation, incremental improvement All-flash storage roundup and price reduction from the big six storage suppliers. 2016: The startups In a short space of time, the big six storage providers have built out their flash product offerings into mature and scalable platforms. -

V-Series Implementation Guide Ramsan Storage

V-Series Systems Implementation Guide for RamSan Storage NetApp, Inc. 495 East Java Drive Sunnyvale, CA 94089 U.S.A. Telephone: +1 (408) 822-6000 Fax: +1 (408) 822-4501 Support telephone: +1 (888) 4-NETAPP Documentation comments: [email protected] Information Web: http://www.netapp.com Part number: 210-04513_A0 July 2009 Copyright and trademark information Copyright Copyright © 1994-2009 NetApp, Inc. All rights reserved. Printed in the U.S.A. information Software derived from copyrighted NetApp material is subject to the following license and disclaimer: THIS SOFTWARE IS PROVIDED BY NETAPP “AS IS” AND WITHOUT ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, WHICH ARE HEREBY DISCLAIMED. IN NO EVENT SHALL NETAPP BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. NetApp reserves the right to change any products described herein at any time, and without notice. NetApp assumes no responsibility or liability arising from the use of products described herein, except as expressly agreed to in writing by NetApp. The use or purchase of this product does not convey a license under any patent rights, trademark rights, or any other intellectual property rights of NetApp. -

Spc Benchmark 1™ Executive Summary Texas Memory Systems, Inc

SPC BENCHMARK 1™ EXECUTIVE SUMMARY TEXAS MEMORY SYSTEMS,INC. TEXAS MEMORY SYSTEMS RAMSAN-630 SPC-1 V1.12 Submitted for Review: May 10, 2011 Submission Identifier: A00105 EXECUTIVE SUMMARY Page 2 of 7 EXECUTIVE SUMMARY Test Sponsor and Contact Information Test Sponsor and Contact Information Texas Memory Systems, Inc. – http://www.ramsan.com Test Sponsor Timothy Logan – [email protected] Primary Contact 10777 Westheimer, Ste. 600 Houston, TX 77042 Phone: (713) 266-3200 FAX: (713) 266-0332 Texas Memory Systems, Inc. – http://www.ramsan.com Test Sponsor Jamon Bowen – [email protected] Alternate Contact 10777 Westheimer, Ste. 600 Houston, TX 77042 Phone: (713) 266-3200 FAX: (713) 266-0332 Auditor Storage Performance Council – http://www.storageperformance.org Walter E. Baker – [email protected] 643 Bair Island Road, Suite 103 Redwood City, CA 94063 Phone: (650) 556-9384 FAX: (650) 556-9385 Revision Information and Key Dates Revision Information and Key Dates SPC-1 Specification revision number V1.12 SPC-1 Workload Generator revision number V2.1.0 Date Results were first used publicly May 10, 2011 Date the FDR was submitted to the SPC May 10, 2011 Date the priced storage configuration is available for currently available shipment to customers Date the TSC completed audit certification May 10, 2011 SPC BENCHMARK 1™ V1.12 EXECUTIVE SUMMARY Submission Identifier: A00105 Texas Memory Systems, Inc. Submitted for Review: MAY 10, 2011 Texas Memory Systems RamSan-630 EXECUTIVE SUMMARY Page 3 of 7 Tested Storage Product (TSP) Description The Texas Memory Systems’ RamSan-630 rack mounted SLC NAND Flash system is a 3U enterprise class designed solid state disk offering scalable performance and affordable high capacity. -

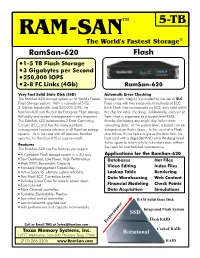

Texas Memory Systems Ramsan-620 Data Sheet

Preliminary RAM-SAN™ 5-TB The World's Fastest Storage ® RamSan-620 Flash 1-5 TB Flash Storage 3 Gigabytes per Second 250,000 IOPS 2-8 FC Links (4Gb) RamSan-620 Very Fast Solid State Disk (SSD) Automatic Error Checking The RamSan-620 storage system is the World's Fastest Storage data integrity is provided by the use of SLC Flash Storage system. With a capacity of 5-TB, Flash chips with two independent methods of ECC. 3-GB/sec bandwidth, and 250,000 IOPS, the Each Flash chip incorporates an ECC data field within RamSan-620 sets the bar for Enterprise Flash storage. the chip for initial checking. Additionally, each set of Reliability and system management is very important. flash chips is organized as a board-level RAID; The RamSan-620 incorporates 2 Error Correcting thereby eliminating any single chip failure from Circuits (ECC) and has the many standard corrupting data. At the system-level, a board can be management features inherent in all RamSan storage designated an Active Spare. In the event of a Flash systems. As is the case with all previous RamSan chip failure, Active Spare migrates the data from the systems, the RamSan-620 is easy to install. flash card with a degraded RAID onto the designated Active Spare to return to fully redundant state without Features the need for unscheduled maintenance. The RamSan-620 has the features you expect: ! A Complete Flash storage system in a 2U rack Applications for the RamSan-620 ! Low Overhead, Low Power, High Performance Databases Hot Files ! High IOPS, Bandwidth, Capacity ! Standard Management -

Validating You IO Subsystem

Validating your IO Subsystem Coming Out of the Black Box Mike Ault, Oracle Guru, TMS, Inc. A Texas Memory Systems Presentation The Black Box For most people the IO subsystem for their servers is a black box. The capacity (as defined in megabytes) is easy to confirm The performance (defined by input and output operations per second (IOPS) and latency (milliseconds, ms) may be more difficult to determine. In this paper we will explore different methodologies to obtain the IOPS and latency for your application. A Texas Memory Systems Presentation IO Is not a Black Box We are led to believe that the entire IO subsystem is out of our hands The details of the IO subsystem will make or break your database performance. Eventually almost all performance issues are traced to IO issues. A Texas Memory Systems Presentation IO is Not a Black Box Inside Oracle, views such as v$filestat and v$tempstat provide cumulative information about IO operations Using some simple queries you can determine long term averages for IOPS and latency for the files in your system. To get more granular data, tools such as Statspack and AWR must be used A Texas Memory Systems Presentation Example IO Script column sum_io1 new_value st1 noprint column sum_io2 new_value st2 noprint column sum_io new_value divide_by noprint rem select nvl(sum(a.phyrds+a.phywrts),0) sum_io1 from sys.v_$filestat a; select nvl(sum(b.phyrds+b.phywrts),0) sum_io2 from sys.v_$tempstat b; select &st1+&st2 sum_io from dual; rem ttitle 'File IO Statistics Report' spool fileio A Texas Memory -

Enterprise Flash Array Storage

EFA Enterprise Flash Array Storage A Peek Into What Real Users Think December 2016 Enterprise Flash Array Storage Contents Vendor Directory 3 Top 10 Vendors 4 - 5 Top 5 Solutions by Ranking Factor 6 Focus on Solutions HPE 3PAR Flash Storage 7 - 9 Tintri VMstore 10 - 12 NetApp All Flash FAS 13 - 15 Pure Storage 16 - 18 Nimble Storage 19 - 21 EMC VNX 22 - 24 Kaminario K2 25 - 27 SolidFire 28 - 30 IBM FlashSystem 31 - 32 NetApp EF-Series All Flash Arrays 33 - 35 About This Report and IT Central Station 36 2 Enterprise Flash Array Storage Vendor Directory Dell EMC Dell EMC XtremIO Flash Storage NetApp SolidFire Dell EMC EMC VNX NetApp NetApp EF-Series All Flash Arrays Dell EMC EMC Unity NexGen Storage NexGen Storage Dell EMC EMC DSSD D5 Nimble Storage Nimble Storage E8 Storage E8 Storage Nimbus Data Nimbus Data Gemini All-Flash Arrays Elastifile Elastifile Oracle Oracle FS1 Flash Storage System Hewlett Packard HPE 3PAR Flash Storage Pure Storage Pure Storage Enterprise Reduxio Reduxio Hitachi Hitachi Virtual Storage Platform SanDisk SanDisk InfiniFlash System Hitachi Hitachi Universal Storage VM SanDisk Fusion-io IBM IBM FlashSystem Tegile Tegile IBM IBM Storwize Tintri Tintri VMstore Kaminario Kaminario K2 Violin Memory Violin Memory NetApp NetApp All Flash FAS © 2016 IT Central Station To read more reviews about Enterprise Flash Array Storage, please visit: http://www.itcentralstation.com/category/enterprise-flash-array-storage 3 Enterprise Flash Array Storage Top Enterprise Flash Array Storage Solutions Over 127,030 professionals have used IT Central Station research on enterprise tech. Here are the top Enterprise Flash Array Storage vendors based on product reviews, ratings, and comparisons. -

Essential Guide to Solid-State Drives

Managing the information that drives the enterprise STORAGE ESSENTIAL GUIDE TO Solid-State Drives Solid-state drive technologies that will have the most impact for enterprise data storage administrators are highlighted in this guide. INSIDE 6 SSD trends 13 Wide stripe before you dive into SSD 16 DRAM SSD leaves FC in the dust 18 MLC NAND flash 22 When to recommend SSD 27 Vendor resources 1 , editorial | rich castagna s e c r u o s e r r The state of storage o d n e Solid-state storage is poised to revolutionize V data center storage with new and inventive implementations of NAND flash already available. D S S g n i d n e T’S SMALL, it runs cool, it’s power efficient and it’s lightning fast. There’s m an awful lot to like about solid-state storage. Put it head-to-head with m o traditional spinning media and it wins on nearly all counts, with admit- c e tedly some not yet fully resolved issues related to long-term reliability R and price. Still, few would question that solid-state is the direction that enterprise storage is headed. The real question is just how soon the transition from mechanical storage to solid The real question is state will take place. D just how soon the S Although new to the data center, NAND S i flash-based solid-state storage has been transition from M A around for a long time, used mostly in R mechanical storage D consumer and mobile products like smart phones, PDAs and MP3 players. -

SSD Industry Report 2010

Rise of SSD in the Enterprise SSD Industry Report 2010 TABLE OF CONTENTS 1 Executive Summary 1.1 Executive Overview 1.2 Storage Industry Dynamics Computing Landscape – 1980 vs 2010 Closing the Price/Performance Gap in the Storage Hierarchy Access Density: A Growing Problem Memory Market Drivers 1.3 Market Status & Trends Solid State Drives: Market Drivers SSDs: When, Why and Where in the Computer Hierarchy? SSD Today & Challenges New SSD Market Segments – DRAM/SSD NVM vs. HDD/SSD Cache 1.4 Storage Market Segments & Product Requirements Application Driven Enterprise Requirements SSDs vs. HDDs: Features/Benefits, Competitive Pricing Pricing Dynamics – Impact on SSD Market Demand Price Driven SSD Market Demand Crossing over HDDs 1.5 Managing SSDs Controllers managing BER, Endurance, LifeCycles, Wear … Emphasizing Total Cost of Ownership 1.6 Enterprise SSD Price Forecast The Impact of Price Reductions SSD Costs Scale Out Model vs. Scale Up Models 1.7 Current Drivers & Inhibitors of SSD Why SSD Acceptance is still limited 1.8 Emerging Technologies MLC NAND, Phase Change 1.9 Futures SSD Industry Roadmap 2010-2020 2 Market Drivers & Industry Dynamics 2.1 Customers requirements for NextGen Storage 2.2 SSDs: A shift in Data Storage 2.3 Killer Applications & Infrastructure for SSDs 2.4 SSD Myths & Facts 2.5 SSD vs HDD Complexity of HDDs vs. Simplicity of SSDs Real TCO - Leveraging SSD’s advantage over HDDs SAN TCO Savings using Intelligent Tiered Storage Price & Capacity 2010 SSD vs. HDD Side/Side Comparison: Power Consumption, Performance, Total -

Open Youngjaekim-Dissertation.Pdf

The Pennsylvania State University The Graduate School DESIGN CHALLENGES ON ENTERPRISE-SCALE STORAGE SYSTEMS EMPLOYING HARD DRIVES AND NAND FLASH BASED SOLID-STATE DRIVES A Dissertation in Computer Science and Engineering by Youngjae Kim c 2009 Youngjae Kim Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy December 2009 The dissertation of Youngjae Kim was reviewed and approved∗ by the following: Anand Sivasubramaniam Professor of Computer Science and Engineering Dissertation Co-Advisor, Co-Chair of Committee Bhuvan Urgaonkar Assistant Professor of Computer Science and Engineering Dissertation Co-Advisor, Co-Chair of Committee Prasenjit Mitra Assistant Professor of Computer Science and Engineering Qian Wang Associate Professor of Mechanical and Nuclear Engineering Raj Acharya Professor of Computer Science and Engineering Head of the Department of Computer Science and Engineering ∗Signatures are on file in the Graduate School. Abstract Flash memory overcomes some key shortcomings of hard disk drives (HDDs), in- cluding faster access to non-sequential data and lower power consumption. Eco- nomic forces, driven by the desire to introduce flash into the enterprise market without changing existing software based, have resulted in the emergence of solid- state drives (SSDs), flash packaged in HDD from factors and capable of working with device drivers and I/O buses designed for HDDs. Unlike the use of DRAM for caching or buffering, however, certain idiosyncrasies of SSDs make their inte- gration into HDD-based systems non-trivial. Flash memory suffers from limits on its reliability, in an order of magnitude more expensive than the disk, and can be sometimes even slower than the HDD (due to excessive GC induced by high intensity of random writes). -

Flash Or SSD: Why and When to Use IBM Flashsystem

Redpaper Megan Gilge Karen Orlando Flash or SSD: Why and When to Use IBM FlashSystem Overview This IBM® Redpaper™ publication explains how to select an IBM FlashSystem™ or solid-state drive (SSD) solution. It describes why and when to use FlashSystem products, and reviews total cost of ownership (TCO), economics, performance, scalability, power, and cooling. Read this guide for information about selecting the correct solution (SSD or flash technology). This paper also reviews examples of FlashSystem storage bundled with solutions such as hybrid arrays and IBM System Storage® SAN Volume Controller (SVC). Furthermore, it compares FlashSystem storage to other storage such as PCIe Express (PCIe) products and hard disk drives (HDDs). Business value of FlashSystem products FlashSystem storage systems deliver high performance, efficiency, and reliability for shared enterprise storage environments, which can help you address performance issues with your most important applications and infrastructure. FlashSystem products also provide capability for big data and cloud environments. These storage systems can either complement or replace traditional hard disk arrays in many business-critical applications: Online transaction processing (OLTP) Business intelligence (BI) Online analytical processing (OLAP) Virtual desktop infrastructures (VDI) High-performance computing (HPC) Content delivery solutions (such as cloud storage and video-on-demand) As standard shared primary data storage devices, FlashSystem storage delivers performance exponentially beyond that of most traditional arrays, even those arrays that incorporate SSDs or other flash technology. These storage systems can also be used as the top tier of storage © Copyright IBM Corp. 2013. All rights reserved. ibm.com/redbooks 1 alongside traditional arrays in tiered storage architectures such as the IBM Easy Tier® functionality available in the System Storage SVC storage virtualization platform.