AN1089: EL4089 and EL4390 DC Restored Video Amplifier

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Prisma II Headend Driver Amplifiers (HEDA)

Prisma II Forward and Reverse Headend Driver Amplifiers Installation and Operation Guide For Your Safety Explanation of Warning and Caution Icons Avoid personal injury and product damage! Do not proceed beyond any symbol until you fully understand the indicated conditions. The following warning and caution icons alert you to important information about the safe operation of this product: You may find this symbol in the document that accompanies this product. This symbol indicates important operating or maintenance instructions. You may find this symbol affixed to the product. This symbol indicates a live terminal where a dangerous voltage may be present; the tip of the flash points to the terminal device. You may find this symbol affixed to the product. This symbol indicates a protective ground terminal. You may find this symbol affixed to the product. This symbol indicates a chassis terminal (normally used for equipotential bonding). You may find this symbol affixed to the product. This symbol warns of a potentially hot surface. You may find this symbol affixed to the product and in this document. This symbol indicates an infrared laser that transmits intensity- modulated light and emits invisible laser radiation or an LED that transmits intensity-modulated light. Important Please read this entire guide. If this guide provides installation or operation instructions, give particular attention to all safety statements included in this guide. Notices Trademark Acknowledgments Cisco and the Cisco logo are trademarks or registered trademarks of Cisco and/or its affiliates in the U.S. and other countries. To view a list of cisco trademarks, go to this URL: www.cisco.com/go/trademarks. -

Analog/SDI to SDI/Optical Converter with TBC/Frame Sync User Guide

Analog/SDI to SDI/Optical Converter with TBC/Frame Sync User Guide ENSEMBLE DESIGNS Revision 6.0 SW v1.0.8 This user guide provides detailed information for using the BrightEye™1 Analog/SDI to SDI/Optical Converter with Time Base Corrector and Frame Sync. The information in this user guide is organized into the following sections: • Product Overview • Functional Description • Applications • Rear Connections • Operation • Front Panel Controls and Indicators • Using The BrightEye Control Application • Warranty and Factory Service • Specifications • Glossary BrightEye-1 BrightEye 1 Analog/SDI to SDI/Optical Converter with TBC/FS PRODUCT OVERVIEW The BrightEye™ 1 Converter is a self-contained unit that can accept both analog and digital video inputs and output them as optical signals. Analog signals are converted to digital form and are then frame synchronized to a user-supplied video reference signal. When the digital input is selected, it too is synchronized to the reference input. Time Base Error Correction is provided, allowing the use of non-synchronous sources such as consumer VTRs and DVD players. An internal test signal generator will produce Color Bars and the pathological checkfield test signals. The processed signal is output as a serial digital component television signal in accordance with ITU-R 601 in both electrical and optical form. Front panel controls permit the user to monitor input and reference status, proper optical laser operation, select video inputs and TBC/Frame Sync function, and adjust video level. Control and monitoring can also be done using the BrightEye PC or BrightEye Mac application from a personal computer with USB support. -

Brighteye 42 Manual

HD/SD/ASI Distribution Amplifier User Guide ENSEMBLE DESIGNS Revision 3.0 SW v1.0 This user guide provides detailed information for using the BrightEye™42 HD/SD/ASI Distribution Amplifier. The information in this user guide is organized into the following sections: • Product Overview • Applications • Rear Connections • Operation • Front Panel Status Indicators • Warranty and Factory Service • Specifications • Glossary BrightEye-1 HD/SD/ASI Distribution Amplifier PRODUCT OVERVIEW The BrightEye™ 42 is a reclocking distribution amplifier that can be used with high definition, standard definition, or ASI signals. When used with SD or ASI input signals, the serial input automatically equalizes up to 300 meters of digital cable. When used with an HD input signal, the serial input automatically equalizes up to 100 meters of digital cable. The input signal is reclocked and delivered to four simultaneous outputs as shown in the block diagram below. The reclocker is ASI compliant and all four outputs have the correct ASI polarity. Front panel indictors permit the user to monitor input signal and power status Signal I/O and power is supplied to the rear of the unit, that is powered by a modular style power supply. There are no adjustments required on this unit. A glossary of commonly used video terms is provided at the end of this guide. HD/SD/ASI In HD/SD/ASI Out Reclocker (follows input) Power Front Panel Indicators BrightEye 42 Functional Block Diagram BrightEye-2 APPLICATIONS BrightEye 42 can be utilized in any number of different applications where distri- bution of HD, SD, or ASI is required. -

Camera Interfacing Guide

Camera Interface Guide Table of Contents Video Basics .......................................................................................................................................................... 5-12 Introduction ....................................................................................................................................................................3 Video formats ..................................................................................................................................................................3 Standard analog format ..................................................................................................................................................3 Blanking intervals...........................................................................................................................................................4 Vertical blanking .............................................................................................................................................................4 Horizontal blanking ........................................................................................................................................................4 Sync Pulses.....................................................................................................................................................................4 Color coding ....................................................................................................................................................................5 -

NTSC Is the Analog Television System in Use in the United States and In

NTSC is the analog television system in use in the United States and in many other countries, including most of the Americas and some parts of East Asia It is named for the National Television System(s) Committee, the industry-wide standardization body that created it. History The National Television Systems Committee was established in 1940 by the Quick Facts about: Federal Communications Commission An independent governmeent agency that regulates interstate and international communications by radio and television and wire and cable and satelliteFederal Communications Commission to resolve the conflicts which had arisen between companies over the introduction of a nationwide analog television system in the U.S. The committee in March 1941 issued a technical standard for Quick Facts about: black and white A black-and-white photograph or slideblack and white television. In January 1950 the committee was reconstituted, this time to decide about color television, and in March 1953 it unanimously approved what is now called simply the NTSC color television standard. The updated standard retained full backwards compatibility with older black and white television sets. The standard has since been adopted by many other countries, for example most of Quick Facts about: the Americas North and South Americathe Americas and Quick Facts about: Japan A constitutional monarchy occupying the Japanese Archipelago; a world leader in electronics and automobile manufacture and ship buildingJapan. Technical details Refresh rate The NTSC format—or more correctly -

Infinitereality™ Video Format Combiner User's Guide

InfiniteReality™ Video Format Combiner User’s Guide Document Number 007-3279-001 CONTRIBUTORS Written by Carolyn Curtis Illustrated by Carolyn Curtis Production by Laura Cooper Engineering contributions by Gregory Eitzmann, David Naegle, Chase Garfinkle, Ashok Yerneni, Rob Wheeler, Ben Garlick, Mark Schwenden, and Ed Hutchins Cover design and illustration by Rob Aguilar, Rikk Carey, Dean Hodgkinson, Erik Lindholm, and Kay Maitz © 1996, Silicon Graphics, Inc.— All Rights Reserved The contents of this document may not be copied or duplicated in any form, in whole or in part, without the prior written permission of Silicon Graphics, Inc. RESTRICTED RIGHTS LEGEND Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and/or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor/manufacturer is Silicon Graphics, Inc., 2011 N. Shoreline Blvd., Mountain View, CA 94043-1389. Silicon Graphics, the Silicon Graphics logo, Onyx, and IRIS are registered trademarks and IRIX, Sirius Video, POWER Onyx, and InfiniteReality are trademarks of Silicon Graphics, Inc. X Window System is a trademark of Massachusetts Institute of Technology. InfiniteReality™ Video Format Combiner User’s Guide Document Number 007-3279-001 Contents List of Figures vii List of Tables ix About This Guide xi Audience xi Structure of This Guide xi Conventions xii 1. InfiniteReality Graphics and the Video Format Combiner Utility 1 Channel Input and Output 2 Video Format Combinations 2 Video Format Combiner Utility and the Sirius Video Option 2 Programmable Querying of Video Format Combinations 3 2. -

611 Subpart K—Technical Standards

Federal Communications Commission § 76.601 Subpart K—Technical Standards procedures utilized, and a statement of the qualifications of the person per- § 76.601 Performance tests. forming the tests shall also be in- (a) The operator of each cable tele- cluded. vision system shall be responsible for (2) Proof-of-performance tests to de- insuring that each such system is de- termine the extent to which a cable signed, installed, and operated in a television system complies with the manner that fully complies with the standards set forth in § 76.605(a) (3), (4), provisions of this subpart. and (5) shall be made on each of the (b) The operator of each cable tele- NTSC or similar video channels of that vision system shall conduct complete system. Unless otherwise as noted, performance tests of that system at proof-of-performance tests for all other least twice each calendar year (at in- standards in § 76.605(a) shall be made on tervals not to exceed seven months), a minimum of four (4) channels plus unless otherwise noted below. The per- one additional channel for every 100 formance tests shall be directed at de- MHz, or fraction thereof, of cable dis- termining the extent to which the sys- tribution system upper frequency limit tem complies with all the technical (e.g., 5 channels for cable television standards set forth in § 76.605(a) and systems with a cable distribution sys- shall be as follows: tem upper frequency limit of 101 to 216 (1) For cable television systems with MHz; 6 channels for cable television 1000 or more subscribers but with 12,500 systems with a cable distribution sys- or fewer subscribers, proof-of-perform- tem upper frequency limit of 217–300 ance tests conducted pursuant to this MHz; 7 channels for cable television section shall include measurements systems with a cable distribution upper taken at six (6) widely separated frequency limit to 300 to 400 MHz, etc.). -

Mha Tfa X-Bp5.39

X-460-70-300 PREIN1T mhA Tfa X-bP5.39 SUPER-HIGH-FREQUENCY (SHF) COMMUNICATIONS SYSTEM PERFORMANCE ON ATS VOLUME 2: DATA AND ANALYSIS AUGUST 1970 - GODDARD SPACE FLIGHT CENTER GREENBELT, MARYLAND A70-41386 (PAGE) _ CD) RIoWducedby 0NF (NAS CROR TMX ORAD NUMBER) (CATEGORY) -- R in V5 X-460-70-300 SUPER-HIGH-FREQUENCY (SHF) COMMUNICATIONS SYSTEM PERFORMANCE ON ATS VOLUME 2: DATA AND ANALYSIS Prepared by: Westinghouse Electric Corporation and The ATS Project Office August 1970 GODDARD SPACE FLIGHT CENTER Greenbelt, Maryland This report consists of two volumes. Volume 1, System Summary (X-460-70-299), contains section 1 only (section 2 was deleted). Volume 2, Data and Analysis (X-460-70-300), contains sections 3, (4 deleted), 5, 6, and 7. TABLE OF CONTENTS 3 DATA ANALYSIS ..................................... 3.1 3.1 PATH LOSS EXPERIMENTS .......................... 3.2 3. 1. 1 RF Signal Power Levels and Propagation Losses .......... 3.2 3.2 MULTIPLEX IF/RF AND BASEBAND PERFORMANCE EXPERIMENTS ................................... 3.8 3.2.1 Baseband Noise Power Ratio ......................... 3.8 3. 2. 2 FDM Baseband Attenuation Versus Frequency (Baseband Frequency Response) ............................... 3.94 3.3 CONTROL LOOP AND STABILITY EXPERIMENTS .............. 3.100 3.3.1 Multiplex Channel Frequency Stability .................. 3.100 3.3.2 Multiplex Channel Level Stability .................. 3.119 3.3.3 Ground Transmitter Automatic Level Control Loop ...... 3.126 3.4 MULTIPLEX PERFORMANCE EXPERIMENTS ................. 3.132 3.4.1 Channel TT/NRatio ........................... 3.132 3.4.2 Digital Data Error Rate ........................ 3.171 3.4.3 Multiplex Channel Linearity ...................... 3.179 3.4.4 Multiplex Channel Audio Envelope Delay .............. -

A Preview of the Television Video and Audio – a Ready Reference for Engineers Course

A Preview of the Television Video and Audio – a Ready Reference for Engineers Course About the Author Randy Hoffner is retired from ABC Broadcast Operations and Engineering West Coast, where he held the position of Manager of Technology and Quality Control. Prior to 2006, Hoffner spent a number of years at ABC BOE New York, where he worked on advanced television projects including HDTV and early film-to-720p video transfers, accomplished using data telecine transfer techniques. Before joining ABC, Hoffner spent 15 years at NBC, New York, where he worked on technology development projects, including early HDTV work, and held the positions of Director of Research and Development and Director of Future Technology. He also played a large role in the transition of the NBC Television Network and local NBC television stations to stereo broadcasting. He twice received the NBC Technical Excellence Award. Hoffner is a Fellow of SMPTE, and has served the Audio Engineering Society as Convention Chairman and Vice President, Eastern Region, US and Canada. He has authored a number of technical papers presented at SMPTE and AES conventions, and published in their respective Journals. For many years he has written a column, “Technology Corner”, for the trade publication TV Technology. Introduction The purpose of this course is to give the television engineer a solid grounding in the various aspects of video and audio for television, and to serve as a ready reference to the pertinent standards. This course provides an overview of video and audio for television, from the dawn of analog television broadcasting to today’s digital television transmission. -

Evaluating the Navigation Potential of the National Television System Committee Broadcast Signal

Air Force Institute of Technology AFIT Scholar Theses and Dissertations Student Graduate Works 3-12-2004 Evaluating the Navigation Potential of the National Television System Committee Broadcast Signal Ryan J. Eggert Follow this and additional works at: https://scholar.afit.edu/etd Part of the Electrical and Electronics Commons Recommended Citation Eggert, Ryan J., "Evaluating the Navigation Potential of the National Television System Committee Broadcast Signal" (2004). Theses and Dissertations. 4039. https://scholar.afit.edu/etd/4039 This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact [email protected]. AFIT/GE/ENG/04-08 EVALUATING THE NAVIGATION POTENTIAL OF THE NATIONAL TELEVISION SYSTEM COMMITTEE BROADCAST SIGNAL THESIS Ryan J. Eggert Second Lieutenant, USAF AFIT/GE/ENG/04-08 DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY AIR FORCE INSTITUTE OF TECHNOLOGY Wright-Patterson Air Force Base, Ohio APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED. The views expressed in this thesis are those of the author and do not reflect the o±cial policy or position of the United States Air Force, Department of Defense, or U.S. Government. AFIT/GE/ENG/04-08 EVALUATING THE NAVIGATION POTENTIAL OF THE NATIONAL TELEVISION SYSTEM COMMITTEE BROADCAST SIGNAL THESIS Presented to the Faculty Department of Electrical and Computer Engineering Graduate School of Engineering and Management Air Force Institute of Technology Air University Air Education and Training Command In Partial Ful¯llment of the Requirements for the Degree of Master of Science in Electrical Engineering Ryan J. -

United States Patent (19) 11 Patent Number: 5,754,650 Katznelson 45 Date of Patent: May 19, 1998

US005754650A United States Patent (19) 11 Patent Number: 5,754,650 Katznelson 45 Date of Patent: May 19, 1998 54 SIMULTANEOUS MULTICHANNEL OTHER PUBLICATIONS TELEVISION ACCESS CONTROL SYSTEM AND METHOD "Instruction Manual." MX-MS Scrambler, Magnavox 75) Inventor: Ron D. Katznelson, San Diego, Calif. CATV Systems, Inc. 1979. Ostuni, Joseph. "Reference Manual. Pay TV." Magnavox 73) Assignee: Multichannel Communication CATV Systems, Inc. 1978. Sciences, Inc., San Diego, Calif. "Terminal Products." Magnavox CATV Systems, Inc. 1979. (21) Appl. No.: 433,135 22 Filed: May 3, 1995 Primary Examiner-Gilberto Barron, Jr. Attorney, Agent, or Firm-Irell & Manella LLP Related U.S. Application Data 57 ABSTRACT 63 Continuation of Ser. No. 233,212, Apr. 25, 1994, Pat No. 5,430,799, which is a continuation of Ser. No. 818,752, Jan. A multichannel television access control system is disclosed 8, 1992, abandoned. wherein processing of the broadband signal is performed by (51) int. C. ... H04N 7/171 gated coherent RF injection on a plurality of channels. 52) U.S. Cl. ................................ 380/15; 380/12;380/34; thereby effecting selective descrambling of an arbitrary 380/20 subset of channels in a channel group. The system provides 58) Field of Search .................................... 380/7, 10, 12. for a closed loop injection signal phasor control so as to 380/13, 15, 34, 20 maintain substantially constant relationship between the television signals and the injected signals. The combined 56) References Cited signals are supplied to subscribers enabling the use of their cable ready equipment. U.S. PATENT DOCUMENTS 5,319,709 6/1994 Raiser et al. 35 Claims, 18 Drawing Sheets III: NECTED RF CARRIERS U.S. -

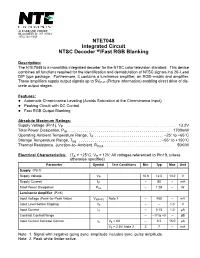

NTE7048 Integrated Circuit NTSC Decoder W/Fast RGB Blanking

NTE7048 Integrated Circuit NTSC Decoder w/Fast RGB Blanking Description: The NTE7048 is a monolithic integrated decoder for the NTSC color television standard. This device combines all functions required for the identification and demodulation of NTSC signals ina 20–Lead DIP type package. Furthermore, it contains a luminance amplifier, an RGB–matrix and amplifier. These amplifiers supply output signals up to 5VP–P (Picture information) enabling direct drive of dis- crete output stages. Features: D Automatic Chrominance Leveling (Avoids Saturation at the Chrominance Input) D Peaking Circuit with DC Control D Fast RGB Output Blanking Absolute Maximum Ratings: Supply Voltage (Pin1), VP . 13.2V Total Power Dissipation, Ptot . 1700mW Operating Ambient Temperature Range, TA . –25° to +65°C Storage Temperature Range, Tstg . –55° to +150°C Thermal Resistance, Junction–to–Ambient, RthJA . 50K/W Electrical Characteristics: (TA = +25°C, VP = 12V, All voltages referenced to Pin19, unless otherwise specified) Parameter Symbol Test Conditions Min Typ Max Unit Supply (Pin1) Supply Voltage VP 10.8 12.0 13.2 V Supply Current IP – 90 – mA Total Power Dissipation Ptot – 1.08 – W Luminance Amplifier (Pin8) Input Voltage (Peak–to–Peak Value) V8(P–P) Note 1 – 450 – mV Input Level before Clipping V8 – – 1.0 V Input Current I8 – 0.15 1.0 µA Contrast Control Range – –17 to +3 – dB Input Current Contrast Control I6 V6 < 6V – 0.5 15.0 µA V6 = 2.5V, Note 2 3 7 – mA Note 1. Signal with negative going sync; amplitude includes sync. pulse amplitude. Note 2. Peak white