Consolidated Amended Complaint 16 All Actions

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Second Generation of TSMC's Integrated Fan-Out (Info

Apple A11 Application Processor Second generation of TSMC’s inFO packaging PACKAGING report by Stéphane ELISABETH February 2018 – version 1 ©2017 by System Plus Consulting | Apple A11 with TSMC inFO Packaging 1 Table of Contents Overview / Introduction 4 o Application Processor 87 o Executive Summary Die Views, Marking & Dimensions o Reverse Costing Methodology Die Cross-Section Company Profile 8 Die Process Characteristics o Apple Physical Comparison 94 o Apple APE Portfolio o Apple’s APE Series: A9, A10, A11 o Fan-Out Packaging o APE’s PoP Technology: Standard PoP, MCeP, inFO o TSMC inFO Technology Manufacturing Process 98 o Apple iPhone 8 & X Teardown o APE Die Front-End Process & Fabrication Unit o Fan-Out Market o Deep Trench Capacitor Die Front-End Process Flow Physical Analysis 22 & Fabrication Unit o Summary of the Physical Analysis 23 o inFO Packaging Process Flow & Fabrication unit o Packaging 25 Cost Analysis 117 Package Views, Marking & Dimensions o Summary of the cost analysis 118 o Yields Explanation & Hypotheses 119 Package X-Ray o APE die 122 Package RDL Deprocessing Wafer & Die Front-End Cost Package Memory: X-Ray view & Opening Preparation Wafer Cost Package Opening o LSC die 126 Board Cross-Section: Via Frame, PCB, Dimensions Wafer & Die Front-End Cost Package Cross-Section: TiV, Adhesive, RDLs Frond-End cost per Process Steps Package Process o inFO Packaging 131 Summary of Physical Data inFO Wafer Cost o Land-Side Capacitor 65 inFO Front-End Cost per Process Steps Die Views & Dimensions Component Cost Die Deprocessing & Delayering Company services 136 Die Process Die Cross-Section Die Process Characteristics ©2017 by System Plus Consulting | Apple A11 with TSMC inFO Packaging 2 Executive Summary Overview / Introduction o Executive Summary • This full reverse costing study has been conducted to provide insight on technology data, manufacturing cost and selling price of o Reverse Costing Methodology the Apple A11. -

Talkonly Apple Keynote (Sept 2017) Bi… Myfreebingocards.Com

Talkonly Apple Keynote (Sept 2017) Bi… myfreebingocards.com Safety First! Before you print all your bingo cards, please print a test page to check they come out the right size and color. Your bingo cards start on Page 4 of this PDF. If your bingo cards have words then please check the spelling carefully. If you need to make any changes go to mfbc.us/e/n6ctdh Play Once you've checked they are printing correctly, print off your bingo cards and start playing! On the next two pages you will find the "Bingo Caller's Card" - this is used to call the bingo and keep track of which words have been called. Your bingo cards start on Page 4. Virtual Bingo Please do not try to split this PDF into individual bingo cards to send out to players. We have tools on our site to send out links to individual bingo cards. For help go to myfreebingocards.com/virtual-bingo. Help If you're having trouble printing your bingo cards or using the bingo card generator then please go to https://myfreebingocards.com/faq where you will find solutions to most common problems. Share Pin these bingo cards on Pinterest, share on Facebook, or post this link: mfbc.us/s/n6ctdh Edit and Create To add more words or make changes to this set of bingo cards go to mfbc.us/e/n6ctdh Go to myfreebingocards.com/bingo-card-generator to create a new set of bingo cards. Legal The terms of use for these printable bingo cards can be found at myfreebingocards.com/terms. -

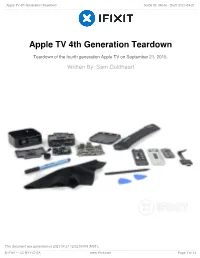

Apple TV 4Th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21

Apple TV 4th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21 Apple TV 4th Generation Teardown Teardown of the fourth generation Apple TV on September 21, 2015. Written By: Sam Goldheart This document was generated on 2021-04-21 12:02:09 PM (MST). © iFixit — CC BY-NC-SA www.iFixit.com Page 1 of 14 Apple TV 4th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21 INTRODUCTION Apple fans are doing the happy dance, what with a slew of new devices coming out of Cupertino— including the first new Apple TV in more than three years. Our teardown engineers look pretty happy too. That's because we've got our hands on a 4th generation Apple TV. That's right, kids. It's teardown time! Don't touch that dial—unless you're looking for more teardown news on our Facebook, Instagram, or Twitter. [video: https://www.youtube.com/watch?v=lSA8uFwptJc] TOOLS: iFixit Opening Picks set of 6 (1) Spudger (1) T7 Torx Screwdriver (1) T3 Torx Screwdriver (1) This document was generated on 2021-04-21 12:02:09 PM (MST). © iFixit — CC BY-NC-SA www.iFixit.com Page 2 of 14 Apple TV 4th Generation Teardown Guide ID: 49046 - Draft: 2021-04-21 Step 1 — Apple TV 4th Generation Teardown We like to start with some specs, and in this case a lot of the good stuff is packed into the fancypants new remote. The box itself contains: Dual-core, 64-bit Apple A8 chip Ethernet, 802.11a/b/g/n/ac Wi-Fi, IR receiver, and HDMI 1.4 connectivity ...whilst the remote is packing: Glass Touch surface Dual microphones Accelerometer and gyroscope Bluetooth 4.0, IR transmitter, Lightning connector This document was generated on 2021-04-21 12:02:09 PM (MST). -

TSMC Integrated Fan-Out (Info) Package Apple A10

Electronic Costing & Technology Experts 21 rue la Nouë Bras de Fer 44200 Nantes – France Phone : +33 (0) 240 180 916 email : [email protected] www.systemplus.fr September 2016 – Version 1 – Written by Stéphane ELISABETH DISCLAIMER : System Plus Consulting provides cost studies based on its knowledge of the manufacturing and selling prices of electronic components and systems. The given values are realistic estimates which do not bind System Plus Consulting nor the manufacturers quoted in the report. System Plus Consulting is in no case responsible for the consequences related to the use which is made of the contents of this report. The quoted trademarks are property of their owners. © 2016 by SYSTEM PLUS CONSULTING, all rights reserved. 1 Return to TOC Glossary 1. Overview / Introduction 4 – A10 Die Analysis 57 – Executive Summary – A10 Die View, Dimensions & Marking – Reverse Costing Methodology – A10 Die Cross-Section – A10 Die Process Characteristics 2. Company Profile 7 – Comparison with previous generation 65 – Apple Inc. – A9 vs. A10 PoP – Apple Series Application processor – A9 vs. A10 Process – Fan-Out Packaging – TSMC Port-Folio 4. Manufacturing Process Flow 70 – TSMC inFO packaging – Chip Fabrication Unit – Packaging Fabrication Unit 3. Physical Analysis 15 – inFO Reconstitution Flow – Physical Analysis Methodology – iPhone 7 Plus Teardown 17 5. Cost Analysis 81 – A10 Die removal – Synthesis of the cost analysis – A10 Package-on-Package Analysis 23 – Main steps of economic analysis – A10 Package View, Dimensions – Yields Hypotheses – A10 Package XRay View – Die Cost Analysis 86 – A10 Package Opening – Wafer Cost – A10 Package Marking – Die Cost – A10 Package Cross-Section – inFO Packaging Cost Analysis 90 – A10 Package Cross-Section – Adhesive & Passivation – Packaging Wafer Cost – A10 package cross-Section - TIVs – Packaging Cost per process Steps – A10 package cross-Section – Solder Balls – Component Cost – A10 package cross-Section – RDL – Land-Side Decoupling Capacitor Analysis 48 6. -

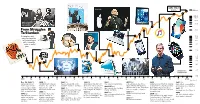

From Struggles to Stardom

AAPL 175.01 Steve Jobs 12/21/17 $200.0 100.0 80.0 17 60.0 Apple co-founders 14 Steve Wozniak 40.0 and Steve Jobs 16 From Struggles 10 20.0 9 To Stardom Jobs returns Following its volatile 11 10.0 8.0 early years, Apple has 12 enjoyed a prolonged 6.0 period of earnings 15 and stock market 5 4.0 gains. 2 7 2.0 1.0 1 0.8 4 13 1 6 0.6 8 0.4 0.2 3 Chart shown in logarithmic scale Tim Cook 0.1 1980 ’82 ’84 ’86’88 ’90 ’92 ’94 ’96 ’98 ’00 ’02 ’04 ’06’08 ’10 ’12 ’14 ’16 2018 Source: FactSet Dec. 12, 1980 (1) 1984 (3) 1993 (5) 1998 (8) 2003 2007 (12) 2011 2015 (16) Apple, best known The Macintosh computer Newton, a personal digital Apple debuts the iMac, an The iTunes store launches. Jobs announces the iPhone. Apple becomes the most valuable Apple Music, a subscription for the Apple II home launches, two days after assistant, launches, and flops. all-in-one desktop computer 2004-’05 (10) Apple releases the Apple TV publicly traded company, passing streaming service, launches. and iPod Touch, and changes its computer, goes public. Apple’s iconic 1984 1995 (6) with a colorful, translucent Apple unveils the iPod Mini, Exxon Mobil. Apple introduces 2017 (17 ) name from Apple Computer. Shares rise more than Super Bowl commercial. Microsoft introduces Windows body designed by Jony Ive. Shuffle, and Nano. the iPhone 4S with Siri. Tim Cook Introduction of the iPhone X. -

Invisible in Man the East Teacher’S Notes Key: Level: Intermediate Upwards Paragraphs 1–9 1

PowersInvisible in man the East Teacher’s notes Teacher’s Key: Level: Intermediate upwards paragraphs 1–9 1. thug; 2. knighted; 3. enterprise; 4. authorship; 5. labs; Timing: 90 minutes plus 6. consultant; 7. tombstone; 8. consummate; 9. refinement; Material needed: One copy of the worksheet 10. conceived per student; one copy of the vocabulary record per student paragraphs 10–19 11. principles; 12. intuitive; 13. honour; 14. shaping; Group size: Any 15. prototypes; 16. temper; 17. permeated; 18. successor; 19. eulogy; 20. touching Find the information Overview Before reading the article properly, students should This lesson plan for both pre-experience and in-work scan the article to find the answers to these key questions. business students is based around an original article first published in Business Spotlight Issue 4/2014. The article is Key: about Sir Jonathan Ive, Apple’s head of design, a man who 1. Apple; 2. head of design; 3. Sir Jonathan Ive; 4. British; could be famous, but isn’t. In the article, we read about 5. Yes. He has a wife and twin sons. what he does, where he came from, what kind of man he is, what well-known products he has designed and his Two-word expressions work philosophy. First, students match words to make expressions from The tasks in the student worksheet ensure that the the article. Then, they use the expressions to complete students understand the content of the article and the the sentences. language used, and also provide extra questions for discussion. Key: 1. softly spoken (para 1); 2. -

Contrails Ejoa Summer 2018

EJOA EDITION SETTING THE STANDARD CONTROLLING USE TAX ON YOUR AIRCRAFT PURCHASES FOR INNOVATION THE PRIVATE JET MAGAZINE SUMMER 2018 DRONES AND HURRICANES SOARING INTO HURRICANE SEASON SERIOUS ASTUNT STICK AND RUDDER FLYING S E T T I N G THE STANDARD A REVIEW OF THE LAST DECADE Embraer 18Q3.indd 1 8/5/18 9:17 PM NEW Now there’s a Bose aviation headset that’s just your type. AIRCRAFT SALES & ACQUISITIONS AEROCOR has quickly become the world's number one VLJ broker, with more listings and more completed transactions than the competition. Our success is driven by product specialization and direct access to the largest pool of light turbine buyers. Find out why buyers and sellers are switching to AEROCOR. UNPARALLELED Introducing the new Bose ProFlight Aviation ACCURATE INTEGRITY PRICING EXPOSURE Headset with features designed for airline and corporate aircraft fl ight decks. Proprietary market Honest & fair Strategic partnership tracking & representation with Aerista, the world's Designed for the professional pilot, the Bose ProFlight is the industry’s valuation tools largest Cirrus dealer smallest, quietest and most comfortable active noise cancelling communication headset and includes three user selectable levels of noise cancellation, a unique tap control for talk-through communication and quick release side-swappable boom microphone and down cable. CALL US TODAY! All engineered into a form factor unlike any other headset – a highly PROFLIGHT AVIATION HEADSET stable, in-ear confi guration without the usual intrusive deep-insert eartips. In-ear confi guration for pilots The new Bose ProFlight is FAA TSO and EASA E/TSO-C139a certifi ed. -

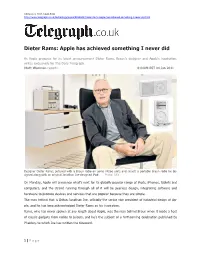

Dieter Rams: Apple Has Achieved Something I Never Did

February 3, 2012, taken from http://www.telegraph.co.uk/technology/apple/8555503/Dieter-Rams-Apple-has-achieved-something-I-never-did.html Dieter Rams: Apple has achieved something I never did As Apple prepares for its latest announcement Dieter Rams, Braun’s designer and Apple’s inspiration, writes exclusively for The Daily Telegraph. Matt Warman reports. 8:00AM BST 04 Jun 2011 Designer Dieter Rams, pictured with a Braun radio on some Vitsoe units and (inset) a portable Braun radio he de- signed along with an original Jonathan Ive-designed iPod Photo: REX On Monday, Apple will announce what’s next for its globally popular range of iPods, iPhones, tablets and computers, and the strand running through all of it will be peerless design, integrating software and hardware to produce devices and services that are popular because they are simple. The man behind that is Briton Jonathan Ive, officially the senior vice president of industrial design at Ap- ple, and he has long acknowledged Dieter Rams as his inspiration. Rams, who has never spoken at any length about Apple, was the man behind Braun when it made a host of classic gadgets from radios to juicers, and he’s the subject of a forthcoming celebration published by Phaidon, to which Ive has written the foreword. 1 | Page February 3, 2012, taken from http://www.telegraph.co.uk/technology/apple/8555503/Dieter-Rams-Apple-has-achieved-something-I-never-did.html When Ive talks about Rams designing “surfaces that were without apology, bold, pure, perfectly- proportioned, coherent and effortless”, he could equally be talking about the iPod. -

Android Vs Ios

Android vs iOS By Mohammad Daraghmeh Jack DeGonzaque AGENDA ● Android ○ History ● Samsung S6 ○ System Architecture ○ Processor ○ Performance Metrics ● iOS ○ History ● iPhone 6 ○ System Architecture ○ Processor ○ Performance Metrics ● Samsung S6 vs iPhone 6 Android Android History ● The Android OS was created mainly by three amazing people Andy Rubin, Rich Miner, Nick Sears, and Chris White. ○ Initial development for the OS was to create an operating system for digital cameras and PC integration. ○ After gauging the size of the market for such a product, Rubin and his colleagues decided to target the booming smartphone market. ● In 2005, Google also wanted to venture into the smartphone market and did so by acquiring Android Inc. ○ The primary directive was to develop technologies that are developed and distributed at a significantly lower cost to make it more accessible. ○ In 2008, the first Android running smartphone, the HTC Dream, was released. Android History (Cont.) ● The Android operating system has become one of the most popular operating systems. ○ According to research firm, called Gartner, more than a billion Android devices were sold in 2014, which is roughly five times more than Apple iOS devices sold and three times more Windows machines sold. ● Their attribute to success stems from the fact that Google does not charge for Android, and that most phone manufacturers are making cost effective phones, which results in affordable smartphones and internet services at low costs for consumers to enjoy. SAMSUNG GALAXY S6 System Architecture ● Samsung S6 uses the Exynos 7420 processor, which is developed by Samsung as well. ○ The Exynos 7420 is a 78 mm^2 SoC comprised of 8 cores connected to two L2 cache instances. -

Acquisition of a Majority Stake in Canyon

Acquisition of a majority stake in Canyon December 2020 2 Letter from the founder “When I saw our first bike on the Tour de France, a childhood dream came true, however, I knew that this was just the beginning. CANYON is built on a foundation of passion and self-sacrifice, with the ultimate goal of being the best bicycle company in the world. In the beginning, a lot of people told us that selling bikes online was impossible. We have proven everybody wrong! We are pioneers in building a fundamentally superior business model and consumer experience which our competitors simply can’t replicate. Our brand today represents the same core values of performance, innovation, community and quality as it did in 1985. This has only been possible thanks to our team. Always passionate, industry-leading and driven by the same goal, building the best and sharing the passion. We are uniquely positioned to take advantage of this huge and growing market with ever more support from recent global events. Our plan will take us to €1bn in sales over the next five years, but our vision remains the same. Canyon is the best bicycle company in the world. We invite GBL to join us as we become the largest.” - Roman Arnold, Founder & Chairman of the Advisory Board 3 Canyon is in line with structural trends which guide GBL’s investment decisions Health awareness Consumer experience Digitalization & technology Sustainability and resource scarcity 4 Introduction to the transaction • GBL has signed a definitive agreement to acquire a majority stake in Canyon • Canyon is -

Mise En Avant SPECIFICATIONS PRINCIPALES

Apple iPhone 6(MQ3D2ZD/A) Apple iPhone 6 - Smartphone - 4G LTE - 32 Go - GSM - 4.7"- 1334 x 750 pixels (326 ppi) - Retina HD - 8 MP (caméra avant de 1,2 mégapixels) - gris L'iPhone 6 n'est pas seulement plus grand en taille. Il est plus grand en tout. Plus large,mais beaucoup plus fin. Plus puissant,mais remarquablement économe en énergie. Sa surface lisse métallique épouse à merveille le nouvel écran Retina. Sous son design profilé s'opère une fusion parfaite entre matériel et logiciel. Redessinée,affûtée,perfectionnée,une nouvelle génération d'iPhone est née. Mise en avant L'iPhone n'a jamais été aussi grand Pas juste un écran plus grand Formidablement puissant L'appareil qui a changé la photo révolutionne maintenant la vidéo Sans-fil plus rapide Votre doigt sur la sécurité Le plus grand des iOS Les atouts L'iPhone n'a jamais été aussi grand Pour développer un iPhone avec un écran plus grand et plus performant,il a fallu repousser plus loin les limites du design. Du mariage parfait du verre et du métal à l'épuration des lignes,le moindre détail a été soigneusement étudié et mis au service de votre utilisation. Ainsi,même avec son écran plus grand,l'iPhone 6 reste parfaitement calibré. Pas juste un écran plus grand C'est une chose que d'agrandir l'écran. C'en est une autre que de mettre au point un écran multi- touch plus grand aux couleurs éclatantes,au contraste accru,avec des angles de vision encore plus larges. Formidablement puissant Le coprocesseur de mouvement M8 compile efficacement les données issues de capteurs innovants et d'un nouveau baromètre. -

Apple Iphone SE 16GB 4-Inch Powerhouse Smartphone!

Apple iPhone SE 16GB 4-inch Powerhouse Smartphone! Apple makes the compact smartphone king again with its new iPhone SE. A 4-inch powerhouse that easily fits in your pocket yet delivers the same high speeds and stunning graphics as the iPhone 6s. It’s designed with an improved battery, a rear-facing 12- megapixel iSight camera with Focus Pixels, True Tone Flash and Live Photos, and FaceTime HD camera with Retina Flash for gorgeous selfies. Same powerful chip as iPhone 6s Engineered to bring desktop-class architecture to the iPhone, the 64-bit A9 chip delivers incredible performance and console-standard graphics in apps and games. Overall computing performance is improved by up to 70% over the previous generation, while graphics are as much as 90% faster, ensuring you get a more reactive, immersive experience. Built within the A9 chip is the M9 motion coprocessor, which is connected to the accelerometer, compass and gyroscope to improve city navigation and fitness tracking. It also works to strengthen your connection to Siri, so you don’t have to hold up your iPhone to ask your questions. Capture amazing photos and 4K videos Take sharp, detailed photos and brilliant 4K video with the new 12 megapixel iSight camera. It’s faster, with improved tone mapping and image stabilisation, so you can just tap the shutter and let iPhone do the rest. And with four times the resolution of 1080p Full HD video, the detail you can capture in videos is simply extraordinary. Live Photos Don’t just capture a still; capture the moment with Live Photos.