TEA6422 TEA6422D TEA6422DT Stmicroelectronics Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Enel Green Power, Sharp and Stmicroelectronics Sign Agreement for the Largest Photovoltaic-Panel Manufacturing Plant in Italy

Enel Green Power, Sharp and STMicroelectronics Sign Agreement for the Largest Photovoltaic-Panel Manufacturing Plant in Italy January 4, 2010 3:04 AM ET Enel Green Power, Sharp and STMicroelectronics join forces to produce innovative thin-film photovoltaic panels. The plant, located in Catania, Italy, is expected to have initial production capacity of 160 MW per year and is targeted to grow to 480 MW over the next years. In addition, Enel Green Power and Sharp will jointly develop solar farms focusing on the Mediterranean area, with a total installed capacity at a level of 500 MW, by the end of 2016. Geneva, January 4, 2010 – Today, Enel Green Power, Sharp and STMicroelectronics signed an agreement for the manufacture of triple-junction thin-film photovoltaic panels in Italy. At the same time, Enel Green Power and Sharp signed a further agreement to jointly develop solar farms. Today's agreement regarding the photovoltaic panel factory follows the Memorandum of Understanding signed in May 2008 by Enel Green Power and Sharp. STMicroelectronics has joined this strategic partnership. This agreement marks the first time that three global technology and industrial powerhouses have joined together in an equal partnership to contribute their unique value-add to the solar industry. It brings together Enel Green Power, with its international market development and project management know-how; Sharp, and its exclusive triple-junction thin-film technology, which will be operational in the mother plant in Sakai, Japan as of spring 2010; and STMicroelectronics, with its manufacturing capacity, skills and resources in highly advanced, hi-tech sectors such as microelectronics. -

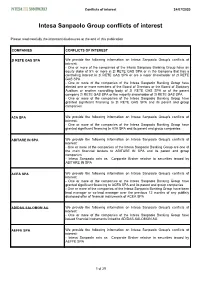

Intesa Sanpaolo Group Conflicts of Interest

Conflicts of interest 24/07/2020 Intesa Sanpaolo Group conflicts of interest Please read carefully the important disclosures at the end of this publication COMPANIES CONFLICTS OF INTEREST 2I RETE GAS SPA We provide the following information on Intesa Sanpaolo Group's conflicts of interest: - One or more of the companies of the Intesa Sanpaolo Banking Group have an equity stake of 5% or more in 2I RETE GAS SPA or in the Company that has a controlling interest in 2I RETE GAS SPA or are a major shareholder of 2I RETE GAS SPA - One or more of the companies of the Intesa Sanpaolo Banking Group have elected one or more members of the Board of Directors or the Board of Statutory Auditors or another controlling body of 2I RETE GAS SPA or of the parent company 2I RETE GAS SPA or the majority shareholder of 2I RETE GAS SPA - One or more of the companies of the Intesa Sanpaolo Banking Group have granted significant financing to 2I RETE GAS SPA and its parent and group companies A2A SPA We provide the following information on Intesa Sanpaolo Group's conflicts of interest: - One or more of the companies of the Intesa Sanpaolo Banking Group have granted significant financing to A2A SPA and its parent and group companies ABITARE IN SPA We provide the following information on Intesa Sanpaolo Group's conflicts of interest: - One or more of the companies of the Intesa Sanpaolo Banking Group are one of the main financial lenders to ABITARE IN SPA and its parent and group companies - Intesa Sanpaolo acts as Corporate Broker relative to securities issued -

4133-6266-6020.6 EMTN PROGRAMME PROSPECTUS This

EMTN PROGRAMME PROSPECTUS This document constitutes two base prospectuses: (i) the base prospectus of TIM S.p.A. and (ii) the base prospectus of Telecom Italia Finance S.A. (together, the EMTN Programme Prospectus). TIM S.p.A. (incorporated with limited liability under the laws of the Republic of Italy) TELECOM ITALIA FINANCE S.A. (incorporated with limited liability under the laws of the Grand-Duchy of Luxembourg) €20,000,000,000 Euro Medium Term Note Programme unconditionally and irrevocably guaranteed in respect of Notes issued by Telecom Italia Finance S.A. by TIM S.p.A. (incorporated with limited liability under the laws of the Republic of Italy) Under this €20,000,000,000 Euro Medium Term Note Programme (the Programme), TIM S.p.A. (TIM) and Telecom Italia Finance S.A. (TI Finance and, together with TIM in its capacity as an issuer, the Issuers and each an Issuer) may from time to time issue notes (the Notes) denominated in any currency agreed with the relevant Dealer (as defined below). Payment of all amounts owing in respect of the Notes issued by TI Finance will be unconditionally and irrevocably guaranteed by TIM (in such capacity, the Guarantor). The maximum aggregate nominal amount of all Notes from time to time outstanding under the Programme will not exceed €20,000,000,000 (or its equivalent in other currencies calculated as described in the Programme Agreement), subject to increase as described herein. The Notes may be issued on a continuing basis to one or more of the Dealers specified under “Overview of the Programme” and any additional Dealer appointed under the Programme from time to time by the Issuers (each a Dealer and, together, the Dealers), which appointment may be for a specific issue or on an ongoing basis. -

World's Smallest Micro-Mirror Scanning Technology From

Press release Communiqué de presse Comunicato stampa 新闻稿 / 新聞稿 プレスリリース 보도자료 T4264D World’s Smallest Micro-Mirror Scanning Technology from STMicroelectronics Chosen for Intel® RealSense™ High-Resolution LiDAR Depth Camera L515 Power-efficient, hi-res LiDAR camera capturing millions of depth points per second suits a wide range of Industrial and Computing use cases Geneva, March 8, 2021 – STMicroelectronics (NYSE: STM), a global semiconductor leader serving customers across the spectrum of electronics applications, has developed a tiny MEMS mirror with Intel enabling spatial scanning of an environment. Intel developed a LiDAR system based on this micro-mirror, providing high-resolution scanning for industrial applications such as robotic arms for bin picking, volumetric measurements, logistics, and 3D scanning. Built into the Intel RealSense LiDAR1 Camera L515, the small dimensions of the ST micro-mirror contribute to the LiDAR camera’s hockey-puck size (61mm diameter x 26mm height). The micro-mirror enables continuous laser scanning across the entire field of view. In combination with a custom photodiode sensor, the RealSense LiDAR Camera L515 renders a 3D depth map of the entire scene. “With 30 frames per second and a field-of-view of 70° by 55°, ST’s 2nd-generation micro-mirror continues to set the bar for 3D scanning and detection applications,” said Benedetto Vigna, President Analog, MEMS and Sensors Group, STMicroelectronics. “Continuing the long-term supply relationship for micro-mirrors with Intel demonstrates our never-ending efforts to leverage our long-lasting leadership in MEMS to meet the demanding technical and supply needs of our customers.” The L515 leverages the scanning capabilities of ST’s MEMS to deliver high-resolution depth with no interpolated pixels, the ability to control the field of view, and provides close to zero pixel blur driven by the low 50nS exposure time. -

John Hancock Disciplined Value International Fund A: JDIBX C: JDICX I: JDVIX R2: JDISX R4: JDITX R6: JDIUX

All data is as of June 30, 2021 Q2 - 2021 International equity fund Quarterly commentary John Hancock Disciplined Value International Fund A: JDIBX C: JDICX I: JDVIX R2: JDISX R4: JDITX R6: JDIUX Objective Use for Morningstar category Long-term growth of capital Core international holding Foreign Large Value Quarterly commentary Highlights The fund beneited from strong stock selection in the communication International equities rallied in the second quarter, helping the fund’s services sector, where SK Telecom Co., Ltd. was a top performer ater its benchmark—the MSCI EAFE Index—achieve a series of all-time highs management announced a plan to split the company in two to recognize before it peaked in mid-June. value. The fund also outperformed in energy, due largely to a rally in shares The fund delivered a positive return, but it trailed the index. of Cenovus Energy, Inc., IMI PLC, and Hitachi Corp. All three companies Given the underperformance of the value style relative to growth, the were top contributors for the quarter, as was a zero weighting in the fund’s value-driven strategy was a headwind to results compared with the Japanese company Sotbank Group Corp. broad-based benchmark. Market review and outlook Portfolio changes International stocks performed well in the past three months as economic We increased the fund’s weightings in industrials and healthcare while data continued to improve as the gradual rollout of vaccines fostered a reducing its allocation to information technology. The changes were all resumption of normal business conditions. Broad measures of consumer stock speciic, and the structure of the portfolio didn’t change materially. -

Euro Stoxx® Residual Momentum Premium Index

EURO STOXX® RESIDUAL MOMENTUM PREMIUM INDEX Components1 Company Supersector Country Weight (%) EUROFINS SCIENTIFIC null null 3.37 SARTORIUS STEDIM BIOTECH null null 3.20 EDP RENOVAVEIS null null 2.97 HELLOFRESH AG null null 2.21 SIEMENS GAMESA null null 2.21 SARTORIUS PREF. null null 2.16 KESKO null null 2.07 DEUTSCHE POST null null 1.89 CORBION null null 1.81 BRENNTAG null null 1.80 SIGNIFY null null 1.75 ZALANDO null null 1.68 SEB null null 1.56 LVMH MOET HENNESSY null null 1.52 BOLLORE null null 1.48 INTERPUMP GRP null null 1.45 SIEMENS null null 1.44 CAP GEMINI null null 1.41 RATIONAL null null 1.41 BMW null null 1.40 BANCO BPM null null 1.37 FUCHS PETROLUB PREF null null 1.30 SOITEC null null 1.27 SAINT GOBAIN null null 1.25 PUBLICIS GRP null null 1.23 MICHELIN null null 1.22 UNIBAIL-RODAMCO-WESTFIELD null null 1.20 WARTSILA null null 1.15 CAIXABANK null null 1.13 STELLANTIS null null 1.12 CNH Industrial NV null null 1.12 SOLVAY null null 1.11 BCO BILBAO VIZCAYA ARGENTARIA null null 1.09 PROSIEBENSAT.1 MEDIA null null 1.08 NOKIAN RENKAAT null null 1.08 COVESTRO null null 1.06 DEUTSCHE BANK null null 1.02 INFINEON TECHNOLOGIES null null 1.02 DAIMLER null null 1.02 STMICROELECTRONICS null null 1.02 CONTINENTAL null null 1.01 REXEL null null 0.99 FLUTTER ENTERTAINMENT null null 0.99 AALBERTS null null 0.99 COMMERZBANK null null 0.95 RYANAIR null null 0.94 HEIDELBERGCEMENT null null 0.93 BASF null null 0.93 ASML HLDG null null 0.93 SPIE null null 0.90 ING GRP null null 0.90 ELIS null null 0.89 HERMES INTERNATIONAL null null 0.88 ASM -

Semiconductors & Semiconductor Equipment

Semiconductors & Semiconductor Equipment Driving forces Highlighted criteria & The application of advanced semiconductors has progressed dimension weights beyond traditional computing products to include the Internet Environmental Dimension..34% of Things, Artificial Intelligence, automotive applications, 5G, – Climate Strategy and high-performance computing. Cybersecurity is a strategic – Environmental Policy & priority that is increasing in importance, since security should Management Systems be included by design during chip R&D. The rate at which the – Operational Eco-Efficiency number of transistors on a chip doubles (i.e., Moore’s Law) is – Product Stewardship slowing as integrated circuits become smaller. The semiconductor industry must, therefore, investigate new architectures, materials, Social Dimension ............. 23% and packaging to go beyond current scaling and performance – Human Capital Development constraints, while also addressing the demand for low energy- – Talent Attraction & Retention consumption products. To sustain a rapid pace of innovation, the industry will need to increase R&D investment that, in turn, Governance & Economic will necessitate attracting and retaining a skilled workforce and Dimension ........................ 43% developing talent. The industry must continue to improve its – Innovation Management ultra-pure water usage, energy and waste management, and – Product Quality and Recall pollution prevention. It must also increase promotion of projects Management to substitute hazardous materials and -

Yield Crescendo Tempo Autocall Step Down on Intesa Sanpaolo

Key Information Document This document provides you with key information about this investment product. It is not marketing material. The information is required by law to help you understand the nature, risks, costs, potential gains and losses of this product and to help you compare it with other products. YIELD CRESCENDO TEMPO AUTOCALL STEP DOWN ON INTESA SANPAOLO, UNICREDIT AND STMICROELECTRONICS - EUR - JANUARY 2022 ISIN: FREXA0014771 Issuer: Exane Finance | Guarantor: Exane Derivatives | Supervisor: Autorité des Marchés Financiers and Autorité de Contrôle Prudentiel et de Résolution | Telephone Number: (+33) 1 44 95 70 00 | Website: www.exane.com KID production date: 4/07/2019 You are about to purchase a product that is not simple and may be difficult to understand. WHAT IS THIS PRODUCT? TYPE: Certificate indexed to one or more Underlyings. OBJECTIVES The Certificate Yield Crescendo Tempo Autocall Step Down on Intesa Sanpaolo, Unicredit and STMicroelectronics - EUR - January 2022 issued by Exane Finance carries a risk of capital loss during its life and at maturity. Coupon mechanism On each Interest Payment Date, if the official closing price of each Underlying on the Coupon Valuation Date is higher than or equal to 50% of its Initial Price, the Holder will receive a coupon of EUR 10 and in addition to the current coupon, all previously missed coupons. Otherwise, no coupon is paid for the period. Automatic Early settlement On each Automatic Early Settlement Date, if the official closing price of each Underlying on the Automatic Early Valuation Date is higher than or equal to the decreasing redemption barrier (as a percentage of its Initial Price), the product is early redeemed and the Holder will receive an amount corresponding to EUR 1,000. -

Italy's Largest Photovoltaic Panel Plant Starts

ITALY’S LARGEST PHOTOVOLTAIC PANEL PLANT STARTS COMMERCIAL PRODUCTION The new industrial plant run by 3SUN – a joint venture equally owned by Enel Green Power, Sharp and STMicroelectronics – has begun commercial manufacturing operations. In its initial phase it will manufacture photovoltaic modules for a potential output of 160MW per year. The Catania plant will supply the most promising markets of Europe, the Middle East and Africa Rome, December 23rd, 2011 – Today marks the first day of commercial manufacturing operations in Catania’s new plant dedicated to technologically innovative solar panels, run by 3Sun, a joint venture company owned by Enel Green Power, Sharp and STMicroelectronics. This is the biggest solar panel plant in Italy, and one of the biggest in Europe. The construction of the plant was financed by a mix of capital from the partners, CIPE’s funding and project financing with three major lending institutions, namely Banca IMI, Centrobanca and Unicredit. In this first phase the plant will produce multi-junction thin- film photovoltaic panels for a capacity of 160MW per year, and will employ around 280 people. The factory’s output is intended to meet the demand of solar power markets in Europe, the Middle East and Africa (EMEA), using both projects under development and the sales networks of Enel Green Power and Sharp. For this purpose, Enel Green Power and Sharp have set up a second joint venture, ESSE (Enel Green Power & Sharp Solar Energy), to develop, build and operate photovoltaic systems in the EMEA area with an output target of over 500MW by 2016, using panels manufactured by the factory. -

Stmicroelectronics Nv (Stm) 20-F

STMICROELECTRONICS NV (STM) 20-F Annual and transition report of foreign private issuers pursuant to sections 13 or 15(d) Filed on 03/05/2012 Filed Period 12/31/2011 Table of Contents As filed with the Securities and Exchange Commission on March 5, 2012 SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 Form 20-F ¨ REGISTRATION STATEMENT PURSUANT TO SECTION 12(b) OR (g) OF THE SECURITIES EXCHANGE ACT OF 1934 OR x ANNUAL REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the fiscal year ended December 31, 2011 OR ¨ TRANSITION REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 For the transition period from to ¨ SHELL COMPANY REPORT PURSUANT TO SECTION 13 OR 15(d) OF THE SECURITIES EXCHANGE ACT OF 1934 Date of event requiring this shell company report Commission file number: 1-13546 STMicroelectronics N.V. (Exact name of registrant as specified in its charter) Not Applicable The Netherlands (Translation of registrant's (Jurisdiction of incorporation name into English) or organization) WTC Schiphol Airport Schiphol Boulevard 265 1118 BH Schiphol Airport The Netherlands (Address of principal executive offices) Carlo Bozotti 39, chemin du Champ des Filles 1228 Plan-Les-Ouates Geneva Switzerland Tel: +41 22 929 29 29 Fax: +41 22 929 29 88 (Name, Telephone, E-mail and/or Facsimile number and Address of Company Contact Person) Securities registered or to be registered pursuant to Section 12(b) of the Act: Title of Each Class: Name of Each Exchange on Which Registered: Common shares, -

Automotive Industry Outlook: Staying Ahead of the Curve in a Rapidly Changing Landscape March 2021

Automotive Industry Outlook: Staying Ahead of the Curve in a Rapidly Changing Landscape March 2021 Mike Wall Executive Director, Automotive Analysis +1 248 728 8400 Direct +1 616 446 6885 Mobile [email protected] © 2021 IHS Markit. All Rights Reserved. 2 A World Leader in Critical Information, Analytics and Solutions Addressing Strategic Challenges with Interconnected Capabilities Energy Financial Agribusiness Services 50,000+ 80% Climate & Economics & customers in over of the Fortune Sustainability Country Risk 140 countries Global 500 Engineering & Life Sciences Product Design 94/100 $4B annual revenue largest US corporates Telecoms & NYSE: INFO Chemical Technology Maritime & Automotive Trade © 2021 IHS Markit. All Rights Reserved. 3 World Economic Growth Global Growth Improved in February; World Real GDP is Projected to Increase 5.1% in 2021 10.0 2018 2019 2020 2021 2022 2023-2028 World Average 8.0 2021 = +5.1% 6.0 4.0 2.0 0.0 -2.0 (in percent) -4.0 -6.0 Annual GrowthAnnual GDP Real -8.0 -10.0 World United Japan Eurozone Brazil Russia India China States (mainland) Source: IHS Markit Data Insight © 2021 IHS Markit. All Rights Reserved. 4 Introduction to Automotive Semiconductor: From Silicon to Cars Car Silicon Ingots and Packaged and Electronics Control Units* • 1,000 – 1,400 Processed wafers chips / car Raw silicon wafers tested chips (ECU) • $427 chip value / car in 2020 Manufacturing cycle time: Months Days Hours Semiconductor Suppliers NXP, Infineon, Renesas, Texas Instruments, Material suppliers: STMicroelectronics, ON Semi, Micron, Samsung... Tier 1: OEMs: Shin-Etsu, Siltronics, Bosch, Continental, Aptiv, Valeo, VW, Toyota, Toyota, Soitec Harman, BorgWarner, Denso… GM, RNM… Foundries (front end): Packaging & Test TSMC, Samsung, (back-end) * Picture from IHS Markit Teardown of GlobalFoundries, UMC, Amkor, ASE, UTAC Harman – Mercedes TTG9 Head-Unit Tower, DB Hitek, SMIC © 2021 IHS Markit. -

Qualcomm® Quick Charge™ Technology Device List

One charging solution is all you need. Waiting for your phone to charge is a thing of the past. Quick Charge technology is ® designed to deliver lightning-fast charging Qualcomm in phones and smart devices featuring Qualcomm® Snapdragon™ mobile platforms ™ and processors, giving you the power—and Quick Charge the time—to do more. Technology TABLE OF CONTENTS Quick Charge 5 Device List Quick Charge 4/4+ Quick Charge 3.0/3+ Updated 09/2021 Quick Charge 2.0 Other Quick Charge Devices Qualcomm Quick Charge and Qualcomm Snapdragon are products of Qualcomm Technologies, Inc. and/or its subsidiaries. Devices • RedMagic 6 • RedMagic 6Pro Chargers • Baseus wall charger (CCGAN100) Controllers* Cypress • CCG3PA-NFET Injoinic-Technology Co Ltd • IP2726S Ismartware • SW2303 Leadtrend • LD6612 Sonix Technology • SNPD1683FJG To learn more visit www.qualcomm.com/quickcharge *Manufacturers may configure power controllers to support Quick Charge 5 with backwards compatibility. Power controllers have been certified by UL and/or Granite River Labs (GRL) to meet compatibility and interoperability requirements. These devices contain the hardware necessary to achieve Quick Charge 5. It is at the device manufacturer’s discretion to fully enable this feature. A Quick Charge 5 certified power adapter is required. Different Quick Charge 5 implementations may result in different charging times. Devices • AGM X3 • Redmi K20 Pro • ASUS ZenFone 6* • Redmi Note 7* • Black Shark 2 • Redmi Note 7 Pro* • BQ Aquaris X2 • Redmi Note 9 Pro • BQ Aquaris X2 Pro • Samsung Galaxy