VGA Function Specification Gxm/Mxi Processors

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

User's Manual L Tqmx80uc UM 0102 L © 2020, TQ-Systems Gmbh Page I

User's Manual l TQMx80UC UM 0102 l © 2020, TQ-Systems GmbH Page i TQMx80UC User's Manual TQMx80UC UM 0102 2020-02-04 User's Manual l TQMx80UC UM 0102 l © 2020, TQ-Systems GmbH Page i TABLE OF CONTENTS 1. ABOUT THIS MANUAL......................................................................................................................................................................... 1 1.1 Copyright and License Expenses .................................................................................................................................................... 1 1.2 Registered Trademarks ...................................................................................................................................................................... 1 1.3 Disclaimer ............................................................................................................................................................................................... 1 1.4 Imprint ..................................................................................................................................................................................................... 1 1.5 Service and Support ............................................................................................................................................................................ 1 1.6 Tips on Safety ....................................................................................................................................................................................... -

Embedded Graphics Drivers and Video BIOS V6.1 User's Guide

Intel® Embedded Graphics Drivers and Video BIOS v6.1 User’s Guide December 2006 Document Number: 274041-011US INFORMATIONLegal Lines and Disclaimers IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Intel may make changes to specifications and product descriptions at any time, without notice. Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. -

Geode™ Gxm Processor Integrated X86 Solution with MMX Support

Geode™ GXm Processor Integrated x86 Solution with MMX Support April 2000 Geode™ GXm Processor Integrated x86 Solution with MMX Support General Description The National Semiconductor® Geode™ GXm processor graphics accelerator provides pixel processing and ren- is an advanced 32-bit x86 compatible processor offering dering functions. high performance, fully accelerated 2D graphics, a 64-bit A separate on-chip video buffer enables >30 fps MPEG1 synchronous DRAM controller and a PCI bus controller, video playback when used together with the CS5530 I/O all on a single chip that is compatible with Intel’s MMX companion chip. Graphics and system memory accesses technology. are supported by a tightly-coupled synchronous DRAM The GXm processor core is a proven design that offers (SDRAM) memory controller. This tightly coupled memory competitive CPU performance. It has integer and floating subsystem eliminates the need for an external L2 cache. point execution units that are based on sixth-generation The GXm processor includes Virtual System Architec- technology. The integer core contains a single, six-stage ture® (VSA™ technology) enabling XpressGRAPHICS execution pipeline and offers advanced features such as and XpressAUDIO subsystems as well as generic emula- operand forwarding, branch target buffers, and extensive tion capabilities. Software handler routines for the Xpress- write buffering. A 16 KB write-back L1 cache is accessed GRAPHICS and XpressAUDIO subsystems can be in a unique fashion that eliminates pipeline stalls to fetch included in the BIOS and provide compatible VGA and 16- operands that hit in the cache. bit industry standard audio emulation. XpressAUDIO tech- In addition to the advanced CPU features, the GXm pro- nology eliminates much of the hardware traditionally asso- cessor integrates a host of functions which are typically ciated with audio functions. -

How Microprocessors Work E 1 of 64 ZM

How Microprocessors Work e 1 of 64 ZM How Microprocessors Work ZAHIDMEHBOOB +923215020706 [email protected] 2003 BS(IT) PRESTION UNIVERSITY How Microprocessors Work The computer you are using to read this page uses a microprocessor to do its work. The microprocessor is the heart of any normal computer, whether it is a desktop machine, a server or a laptop. The microprocessor you are using might be a Pentium, a K6, a PowerPC, a Sparc or any of the many other brands and types of microprocessors, but they all do approximately the same thing in approximately the same way. If you have ever wondered what the microprocessor in your computer is doing, or if you have ever wondered about the differences between types of microprocessors, then read on. Microprocessor History A microprocessor -- also known as a CPU or central processing unit -- is a complete computation engine that is fabricated on a single chip. The first microprocessor was the Intel [email protected] +923215020706 (2003) How Microprocessors Work e 2 of 64 ZM 4004, introduced in 1971. The 4004 was not very powerful -- all it could do was add and subtract, and it could only do that 4 bits at a time. But it was amazing that everything was on one chip. Prior to the 4004, engineers built computers either from collections of chips or from discrete components (transistors wired one at a time). The 4004 powered one of the first portable electronic calculators. The first microprocessor to make it into a home computer was the Intel 8080, a complete 8- bit computer on one chip, introduced in 1974. -

MICROPROCESSOR REPORT the INSIDERS’ GUIDE to MICROPROCESSOR HARDWARE Slot Vs

VOLUME 12, NUMBER 1 JANUARY 26, 1998 MICROPROCESSOR REPORT THE INSIDERS’ GUIDE TO MICROPROCESSOR HARDWARE Slot vs. Socket Battle Heats Up Intel Prepares for Transition as Competitors Boost Socket 7 A A look Look by Michael Slater ship as many parts as they hoped, especially at the highest backBack clock speeds where profits are much greater. The past year has brought a great deal The shift to 0.25-micron technology will be central to of change to the x86 microprocessor 1998’s CPU developments. Intel began shipping 0.25-micron A market, with Intel, AMD, and Cyrix processors in 3Q97; AMD followed late in 1997, IDT plans to LookA look replacing virtually their entire product join in by mid-98, and Cyrix expects to catch up in 3Q98. Ahead ahead lines with new devices. But despite high The more advanced process technology will cut power con- hopes, AMD and Cyrix struggled in vain for profits. The sumption, allowing sixth-generation CPUs to be used in financial contrast is stark: in 1997, Intel earned a record notebook systems. The smaller die sizes will enable higher $6.9 billion in net profit, while AMD lost $21 million for the production volumes and make it possible to integrate an L2 year and Cyrix lost $6 million in the six months before it was cache on the CPU chip. acquired by National. New entrant IDT added another com- The processors from Intel’s challengers have lagged in petitor to the mix but hasn’t shipped enough products to floating-point and MMX performance, which the vendors become a significant force. -

21APPN003 E1 Appnote 003 Application Note

21APPN003 E1 - 2002-12-18 Using P1/P501 Graphics on MEN 824x/ALI boards under ELinOS Application Note Embedded Solutions Board-Level Computers for Industrial Applications ® About this Document About this Document This document describes how to configure P1/P501 graphics mezzanines under ELinOS 2.1 on MEN’s 824x/ALI series PowerPC boards (F1N, B11, A12, D3, SC13). When you have followed these instructions, you'll be able to: • use a VGA monitor as a Linux text console. • access the graphics memory from an application program through /dev/fb0. • run QT/embedded programs. • run X-Window system server (on a frame buffer basis). History Edition Description Technical Content Date of Issue E1 First edition Klaus Popp 2002-12-18 Conventions This sign marks important notes or warnings concerning proper functionality of the ! product described in this document. You should read them in any case. italics Folder, file and function names are printed in italics. bold Bold type is used for emphasis. monospace A monospaced font type is used for listings, C function descriptions or wherever appropriate. hyperlink Hyperlinks are printed in blue color. The globe will show you where hyperlinks lead directly to the Internet, so you can look for the latest information online. MEN Mikro Elektronik GmbH 2 21APPN003 E1 - 2002-12-18 About this Document Copyright Information MEN reserves the right to make changes without further notice to any products herein. MEN makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does MEN assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. -

Intel Embedded Graphics Drivers, EFI Video Driver, and Video BIOS V10.4

Intel® Embedded Graphics Drivers, EFI Video Driver, and Video BIOS v10.4 User’s Guide April 2011 Document Number: 274041-032US INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. -

Dell Openmanage Server Administrator Version 2.3 CIM

Dell OpenManage™ Server Administrator CIM Reference Guide www.dell.com | support.dell.com Notes and Notices NOTE: A NOTE indicates important information that helps you make better use of your computer. NOTICE: A NOTICE indicates either potential damage to hardware or loss of data and tells you how to avoid the problem. ____________________ Information in this document is subject to change without notice. © 2003–2005 Dell Inc. All rights reserved. Reproduction in any manner whatsoever without the written permission of Dell Inc. is strictly forbidden. Trademarks used in this text: Dell, the DELL logo, and Dell OpenManage are trademarks of Dell Inc.; Microsoft and is a registered trademarks of Microsoft Corporation; Intel, Pentium, and Celeron are registered trademarks, and i960, MMX, Xeon, i386, and i486 are trademarks of Intel Corporation. Other trademarks and trade names may be used in this document to refer to either the entities claiming the marks and names or their products. Dell Inc. disclaims any proprietary interest in trademarks and trade names other than its own. January 2005 Contents 1 Introduction Server Administrator. 11 Documenting CIM Classes and Their Properties. 11 Base Classes . 12 Parent Classes . 12 Classes That Describe Relationships . 12 Dell-defined Classes . 13 Typographical Conventions. 13 Common Properties of Classes . 14 Other Documents You May Need . 16 2 CIM_PhysicalElement CIM_PhysicalElement . 17 CIM_PhysicalPackage . 18 CIM_PhysicalFrame . 19 CIM_Chassis . 20 DELL_Chassis . 21 CIM_PhysicalComponent. 23 CIM_Chip . 23 CIM_PhysicalMemory . 24 CIM_PhysicalConnector . 26 CIM_Slot . 28 3 CIM_LogicalElement CIM_LogicalElement. 32 CIM_System . 32 Contents 3 CIM_ComputerSystem . 33 DELL_System . 34 CIM_LogicalDevice . 34 CIM_Sensor . 35 CIM_DiscreteSensor. 36 CIM_NumericSensor. 36 CIM_TemperatureSensor. 38 CIM_CurrentSensor . 39 CIM_VoltageSensor . -

PC Hardware Contents

PC Hardware Contents 1 Computer hardware 1 1.1 Von Neumann architecture ...................................... 1 1.2 Sales .................................................. 1 1.3 Different systems ........................................... 2 1.3.1 Personal computer ...................................... 2 1.3.2 Mainframe computer ..................................... 3 1.3.3 Departmental computing ................................... 4 1.3.4 Supercomputer ........................................ 4 1.4 See also ................................................ 4 1.5 References ............................................... 4 1.6 External links ............................................. 4 2 Central processing unit 5 2.1 History ................................................. 5 2.1.1 Transistor and integrated circuit CPUs ............................ 6 2.1.2 Microprocessors ....................................... 7 2.2 Operation ............................................... 8 2.2.1 Fetch ............................................. 8 2.2.2 Decode ............................................ 8 2.2.3 Execute ............................................ 9 2.3 Design and implementation ...................................... 9 2.3.1 Control unit .......................................... 9 2.3.2 Arithmetic logic unit ..................................... 9 2.3.3 Integer range ......................................... 10 2.3.4 Clock rate ........................................... 10 2.3.5 Parallelism ......................................... -

Towards a Trustworthy Thin Terminal for Securing Enterprise Networks By

Towards a Trustworthy Thin Terminal for Securing Enterprise Networks by Evan J. Frenn A Thesis Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the Degree of Master of Science in Computer Science May 2013 APPROVED: Dr. Craig A. Shue, Major Advisor Dr. Krishna K. Venkatasubramanian, Reader Dr. Craig E. Wills, Head of Department Abstract Organizations have many employees that lack the technical knowledge to securely operate their machines. These users may open malicious email attachments/links or install unverified software such as P2P programs. These actions introduce significant risk to an organizations network since they allow attackers to exploit the trust and access given to a client ma- chine. However, system administrators currently lack the control of client machines needed to prevent these security risks. A possible solution to address this issue lies in attestation. With respect to computer science, attestation is the ability of a machine to prove its current state. This capability can be used by client machines to remotely attest to their state, which can be used by other machines in the network when making trust decisions. Previous research in this area has focused on the use of a static root of trust (RoT), requiring the use of a chain of trust over the entire software stack. We would argue this approach is limited in feasibility, because it requires an understanding and evaluation of all the previous states of a machine. With the use of late launch, a dynamic root of trust introduced in the Trusted Platform Module (TPM) v1.2 specification, the required chain of trust is drastically shortened, minimizing the previous states of a machine that must be evaluated. -

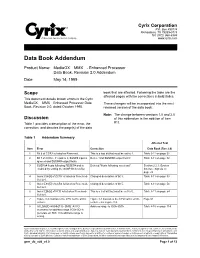

Data Book Addendum

Cyrix Corporation P.O. Box 850118 Richardson, TX 75085-0118 Tel: (972) 968-8388 www.cyrix.com Data Book Addendum Product Name: MediaGX MMX - Enhanced Processor Data Book, Revision 2.0 Addendum Date: May 14, 1999 Scope book that are affected. Following the table are the affected pages with the corrections in bold italics. This document details known errors in the Cyrix MediaGX MMX Enhanced Processor Data These changes will be incorporated into the next Book, Revision 2.0, dated October 1998. released version of the data book. Note: The change between versions 1.0 and 2.0 Discussion of this addendum is the addition of item Table 1 provides a description of the error, the #11. correction, and denotes the page(s) of the data Table 1 Addendum Summary Affected Text Item Error Correction Data Book (Rev 2.0) 1 Bit 6 of CCR2 is listed as Reserved. This is a test bit that must be set to 1. Table 3-11 on page 52 2 Bit 7 of CCR2 - If equal to 0, SUSP# input is Delete “and SUSPA# output floats”. Table 3-11 on page 52 ignored and SUSPA# output floats. 3 SUSPA# floats following RESET# and is Deleted "floats following reset and". Section 2.2.1, System enabled by setting the SUSP bit in CCR2. Interface Signals on page 23 4 Index C3h[3] of CCR3 is listed as Reserved- Changed description of bit 3. Table 3-11 on page 53 Set to 0. 5 Index E8h[5] of CCR4 is listed as Reserved- Changed description of bit 5. -

MARIE: an Introduction to a Simple Computer

00068_CH04_Null.qxd 10/18/10 12:03 PM Page 195 “When you wish to produce a result by means of an instrument, do not allow yourself to complicate it.” —Leonardo da Vinci CHAPTER MARIE: An Introduction 4 to a Simple Computer 4.1 INTRODUCTION esigning a computer nowadays is a job for a computer engineer with plenty of Dtraining. It is impossible in an introductory textbook such as this (and in an introductory course in computer organization and architecture) to present every- thing necessary to design and build a working computer such as those we can buy today. However, in this chapter, we first look at a very simple computer called MARIE: a Machine Architecture that is Really Intuitive and Easy. We then pro- vide brief overviews of Intel and MIPs machines, two popular architectures reflecting the CISC and RISC design philosophies. The objective of this chapter is to give you an understanding of how a computer functions. We have, therefore, kept the architecture as uncomplicated as possible, following the advice in the opening quote by Leonardo da Vinci. 4.2 CPU BASICS AND ORGANIZATION From our studies in Chapter 2 (data representation) we know that a computer must manipulate binary-coded data. We also know from Chapter 3 that memory is used to store both data and program instructions (also in binary). Somehow, the program must be executed and the data must be processed correctly. The central processing unit (CPU) is responsible for fetching program instructions, decod- ing each instruction that is fetched, and performing the indicated sequence of operations on the correct data.