Cascaded Noise Shaping for Oversampling A/D and D/A Conversion

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Design of Optimal Feedback Filters with Guaranteed Closed-Loop Stability for Oversampled Noise-Shaping Subband Quantizers

49th IEEE Conference on Decision and Control December 15-17, 2010 Hilton Atlanta Hotel, Atlanta, GA, USA Design of Optimal Feedback Filters with Guaranteed Closed-Loop Stability for Oversampled Noise-Shaping Subband Quantizers SanderWahls HolgerBoche. Abstract—We consider the oversampled noise-shaping sub- T T T T ] ] ] ] band quantizer (ONSQ) with the quantization noise being q q v q,q v q,q + Quant- + + + + modeled as white noise. The problem at hand is to design an q - q izer q q - q q ,...,w ,...,w optimal feedback filter. Optimal feedback filters with regard 1 1 ,...,v ,...,v to the current standard model of the ONSQ inhabit several + q,1 q,1 w=[w + w=[w =[v =[v shortcomings: the stability of the feedback loop is not ensured - q q v v and the noise is considered independent of both the input and u ŋ u ŋ -1 -1 the feedback filter. Another previously unknown disadvantage, q z F(z) q q z F(z) q which we prove in our paper, is that optimal feedback filters in the standard model are never unique. The goal of this paper is (a) Real model: η is the qnt. error (b) Linearized model: η is white noise to show how these shortcomings can be overcome. The stability issue is addressed by showing that every feedback filter can be Figure 1: Noise-Shaping Quantizer “stabilized” in the sense that we can find another feedback filter which stabilizes the feedback loop and achieves a performance w v E (z) p 1 q,1 p R (z) equal (or arbitrarily close) to the original filter. -

ESE 531: Digital Signal Processing

ESE 531: Digital Signal Processing Lec 12: February 21st, 2017 Data Converters, Noise Shaping (con’t) Penn ESE 531 Spring 2017 - Khanna Lecture Outline ! Data Converters " Anti-aliasing " ADC " Quantization " Practical DAC ! Noise Shaping Penn ESE 531 Spring 2017 - Khanna 2 ADC Penn ESE 531 Spring 2017 - Khanna 3 Anti-Aliasing Filter with ADC Penn ESE 531 Spring 2017 - Khanna 4 Oversampled ADC Penn ESE 531 Spring 2017 - Khanna 5 Oversampled ADC Penn ESE 531 Spring 2017 - Khanna 6 Oversampled ADC Penn ESE 531 Spring 2017 - Khanna 7 Oversampled ADC Penn ESE 531 Spring 2017 - Khanna 8 Sampling and Quantization Penn ESE 531 Spring 2017 - Khanna 9 Sampling and Quantization Penn ESE 531 Spring 2017 - Khanna 10 Effect of Quantization Error on Signal ! Quantization error is a deterministic function of the signal " Consequently, the effect of quantization strongly depends on the signal itself ! Unless, we consider fairly trivial signals, a deterministic analysis is usually impractical " More common to look at errors from a statistical perspective " "Quantization noise” ! Two aspects " How much noise power (variance) does quantization add to our samples? " How is this noise distributed in frequency? Penn ESE 531 Spring 2017 - Khanna 11 Quantization Error ! Model quantization error as noise ! In that case: Penn ESE 531 Spring 2017 - Khanna 12 Ideal Quantizer ! Quantization step Δ ! Quantization error has sawtooth shape, ! Bounded by –Δ/2, +Δ/2 ! Ideally infinite input range and infinite number of quantization levels Penn ESE 568 Fall 2016 - Khanna adapted from Murmann EE315B, Stanford 13 Ideal B-bit Quantizer ! Practical quantizers have a limited input range and a finite set of output codes ! E.g. -

A Subjective Evaluation of Noise-Shaping Quantization for Adaptive

332 IEEE TRANSACTIONS ON COMMUNICATIONS, VOL. 36, NO. 3, MARCH 1988 A Subjective Evaluation of Noise-S haping Quantization for Adaptive Intra-/Interframe DPCM Coding of Color Television Signals BERND GIROD, H AKAN ALMER, LEIF BENGTSSON, BJORN CHRISTENSSON, AND PETER WEISS Abstract-Nonuniform quantizers for just not visible reconstruction quantizers for just not visible eri-ors have been presented in errors in an adaptive intra-/interframe DPCM scheme for component- [12]-[I41 for the luminance and in [IS], [I61 for the color coded color television signals are presented, both for conventional DPCM difference signals. An investigation concerning the visibility and for noise-shaping DPCM. Noise feedback filters that minimize the of quantization errors for an adaiptive intra-/interframe lumi- visibility of reconstruction errors by spectral shaping are designed for Y, nance DPCM coder has been reported by Westerkamp [17]. R-Y, and B-Y. A closed-form description of the “masking function” is In this paper, we present quantization characteristics for the derived which leads to the one-parameter “6 quantizer” characteristic. luminance and the color dilference signals that lead to just not Subjective tests that were carried out to determine visibility thresholds for visible reconstruction errors in sin adaptive intra-/interframe reconstruction errors for conventional DPCM and for noise shaping DPCM scheme. These quantizers have been determined by DPCM show significant gains by noise shaping. For a transmission rate means of subjective tests. In order to evaluate the improve- of around 30 Mbitsls, reconstruction errors are almost always below the ments that can be achieved by reconstruction noise shaping visibility threshold if variable length encoding of the prediction error is [l 11, we compare the quantization characteristics for just not combined with noise shaping within a 3:l:l system. -

Quantization Noise Shaping on Arbitrary Frame Expansions

Hindawi Publishing Corporation EURASIP Journal on Applied Signal Processing Volume 2006, Article ID 53807, Pages 1–12 DOI 10.1155/ASP/2006/53807 Quantization Noise Shaping on Arbitrary Frame Expansions Petros T. Boufounos and Alan V. Oppenheim Digital Signal Processing Group, Massachusetts Institute of Technology, 77 Massachusetts Avenue, Room 36-615, Cambridge, MA 02139, USA Received 2 October 2004; Revised 10 June 2005; Accepted 12 July 2005 Quantization noise shaping is commonly used in oversampled A/D and D/A converters with uniform sampling. This paper consid- ers quantization noise shaping for arbitrary finite frame expansions based on generalizing the view of first-order classical oversam- pled noise shaping as a compensation of the quantization error through projections. Two levels of generalization are developed, one a special case of the other, and two different cost models are proposed to evaluate the quantizer structures. Within our framework, the synthesis frame vectors are assumed given, and the computational complexity is in the initial determination of frame vector ordering, carried out off-line as part of the quantizer design. We consider the extension of the results to infinite shift-invariant frames and consider in particular filtering and oversampled filter banks. Copyright © 2006 P. T. Boufounos and A. V. Oppenheim. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. 1. INTRODUCTION coefficient through a projection onto the space defined by another synthesis frame vector. This requires only knowl- Quantization methods for frame expansions have received edge of the synthesis frame set and a prespecified order- considerable attention in the last few years. -

Color Error Diffusion with Generalized Optimum Noise

COLOR ERROR DIFFUSION WITH GENERALIZED OPTIMUM NOISE SHAPING Niranjan Damera-Venkata Brian L. Evans Halftoning and Image Pro cessing Group Emb edded Signal Pro cessing Lab oratory Hewlett-Packard Lab oratories Dept. of Electrical and Computer Engineering 1501 Page Mill Road The University of Texas at Austin Palo Alto, CA 94304 Austin, TX 78712-1084 E-mail: [email protected] E-mail: [email protected] In this pap er, we derive the optimum matrix-valued er- ABSTRACT ror lter using the matrix gain mo del [3 ] to mo del the noise We optimize the noise shaping b ehavior of color error dif- shaping b ehavior of color error di usion and a generalized fusion by designing an optimized error lter based on a linear spatially-invariant mo del not necessarily separable prop osed noise shaping mo del for color error di usion and for the human color vision. We also incorp orate the con- a generalized linear spatially-invariant mo del of the hu- straint that all of the RGB quantization error b e di used. man visual system. Our approach allows the error lter We show that the optimum error lter may be obtained to have matrix-valued co ecients and di use quantization as a solution to a matrix version of the Yule-Walker equa- error across channels in an opp onent color representation. tions. A gradient descent algorithm is prop osed to solve the Thus, the noise is shap ed into frequency regions of reduced generalized Yule-Walker equations. In the sp ecial case that human color sensitivity. -

Noise Shaping

INF4420 ΔΣ data converters Spring 2012 Jørgen Andreas Michaelsen ([email protected]) Outline Oversampling Noise shaping Circuit design issues Higher order noise shaping Introduction So far we have considered so called Nyquist data converters. Quantization noise is a fundamental limit. Improving the resolution of the converter, translates to increasing the number of quantization steps (bits). Requires better -1 N+1 component matching, AOL > β 2 , and N+1 -1 -1 GBW > fs ln 2 π β . Introduction ΔΣ modulator based data converters relies on oversampling and noise shaping to improve the resolution. Oversampling means that the data rate is increased to several times what is required by the Nyquist sampling theorem. Noise shaping means that the quantization noise is moved away from the signal band that we are interested in. Introduction We can make a high resolution data converter with few quantization steps! The most obvious trade-off is the increase in speed and more complex digital processing. However, this is a good fit for CMOS. We can apply this to both DACs and ADCs. Oversampling The total quantization noise depends only on the number of steps. Not the bandwidth. If we increase the sampling rate, the quantization noise will not increase and it will spread over a larger area. The power spectral density will decrease. Oversampling Take a regular ADC and run it at a much higher speed than twice the Nyquist frequency. Quantization noise is reduced because only a fraction remains in the signal bandwidth, fb. Oversampling Doubling the OSR improves SNR by 0.5 bit Increasing the resolution by oversampling is not practical. -

Sonically Optimized Noise Shaping Techniques

Sonically Optimized Noise Shaping Techniques Second edition Alexey Lukin [email protected] 2002 In this article we compare different commercially available noise shaping algo- rithms and introduce a new highly optimized frequency response curve for noise shap- ing filter implemented in our ExtraBit Mastering Processor. Contents INTRODUCTION ......................................................................................................................... 2 TESTED NOISE SHAPERS ......................................................................................................... 2 CRITERIONS OF COMPARISON............................................................................................... 3 RESULTS...................................................................................................................................... 4 NOISE STATISTICS & PERCEIVED LOUDNESS .............................................................................. 4 NOISE SPECTRUMS ..................................................................................................................... 5 No noise shaping (TPDF dithering)..................................................................................... 5 Cool Edit (C1 curve) ............................................................................................................5 Cool Edit (C3 curve) ............................................................................................................6 POW-R (pow-r1 mode)........................................................................................................ -

Clock Jitter Effects on the Performance of ADC Devices

Clock Jitter Effects on the Performance of ADC Devices Roberto J. Vega Luis Geraldo P. Meloni Universidade Estadual de Campinas - UNICAMP Universidade Estadual de Campinas - UNICAMP P.O. Box 05 - 13083-852 P.O. Box 05 - 13083-852 Campinas - SP - Brazil Campinas - SP - Brazil [email protected] [email protected] Karlo G. Lenzi Centro de Pesquisa e Desenvolvimento em Telecomunicac¸oes˜ - CPqD P.O. Box 05 - 13083-852 Campinas - SP - Brazil [email protected] Abstract— This paper aims to demonstrate the effect of jitter power near the full scale of the ADC, the noise power is on the performance of Analog-to-digital converters and how computed by all FFT bins except the DC bin value (it is it degrades the quality of the signal being sampled. If not common to exclude up to 8 bins after the DC zero-bin to carefully controlled, jitter effects on data acquisition may severely impacted the outcome of the sampling process. This analysis avoid any spectral leakage of the DC component). is of great importance for applications that demands a very This measure includes the effect of all types of noise, the good signal to noise ratio, such as high-performance wireless distortion and harmonics introduced by the converter. The rms standards, such as DTV, WiMAX and LTE. error is given by (1), as defined by IEEE standard [5], where Index Terms— ADC Performance, Jitter, Phase Noise, SNR. J is an exact integer multiple of fs=N: I. INTRODUCTION 1 s X = jX(k)j2 (1) With the advance of the technology and the migration of the rms N signal processing from analog to digital, the use of analog-to- k6=0;J;N−J digital converters (ADC) became essential. -

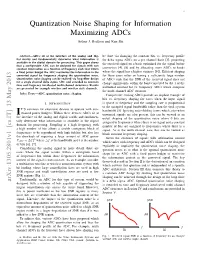

Quantization Noise Shaping for Information Maximizing Adcs Arthur J

1 Quantization Noise Shaping for Information Maximizing ADCs Arthur J. Redfern and Kun Shi Abstract—ADCs sit at the interface of the analog and dig- be done via changing the constant bits vs. frequency profile ital worlds and fundamentally determine what information is for delta sigma ADCs on a per channel basis [3], projecting available in the digital domain for processing. This paper shows the received signal on a basis optimized for the signal before that a configurable ADC can be designed for signals with non constant information as a function of frequency such that within conversion [4], [9] and by allocating more ADCs to bands a fixed power budget the ADC maximizes the information in the where the signal has a higher variance [10]. Efficient shaping converted signal by frequency shaping the quantization noise. for these cases relies on having a sufficiently large number Quantization noise shaping can be realized via loop filter design of ADCs such that the SNR of the received signal does not for a single channel delta sigma ADC and extended to common change significantly within the band converted by the 1 of the time and frequency interleaved multi channel structures. Results are presented for example wireline and wireless style channels. individual constant bit vs. frequency ADCs which comprise the multi channel ADC structure. Index Terms—ADC, quantization noise, shaping. Compressive sensing ADCs provide an implicit example of bits vs. frequency shaping for cases when the input signal I. INTRODUCTION is sparse in frequency and the sampling rate is proportional to the occupied signal bandwidth rather than the total system T’S common for electronic devices to operate with con- bandwidth [5]. -

Measurement of Delta-Sigma Converter

FACULTY OF ENGINEERING AND SUSTAINABLE DEVELOPMENT . Measurement of Delta-Sigma Converter Liu Xiyang 06/2011 Bachelor’s Thesis in Electronics Bachelor’s Program in Electronics Examiner: Niclas Bjorsell Supervisor: Charles Nader 1 2 Liu Xiyang Measurement of Delta-Sigma Converter Acknowledgement Here, I would like to thank my supervisor Charles. Nader, who gave me lots of help and support. With his guidance, I could finish this thesis work. 1 Liu Xiyang Measurement of Delta-Sigma Converter Abstract With today’s technology, digital signal processing plays a major role. It is used widely in many applications. Many applications require high resolution in measured data to achieve a perfect digital processing technology. The key to achieve high resolution in digital processing systems is analog-to-digital converters. In the market, there are many types ADC for different systems. Delta-sigma converters has high resolution and expected speed because it’s special structure. The signal-to-noise-and-distortion (SINAD) and total harmonic distortion (THD) are two important parameters for delta-sigma converters. The paper will describe the theory of parameters and test method. Key words: Digital signal processing, ADC, delta-sigma converters, SINAD, THD. 2 Liu Xiyang Measurement of Delta-Sigma Converter Contents Acknowledgement................................................................................................................................... 1 Abstract .................................................................................................................................................. -

Cities Alive: Towards a Walking World Foreword Gregory Hodkinson | Chairman, Arup Group

Towards a walking world Towards a walking world 50 DRIVERS OF CHANGE 50 BENEFITS 40 ACTIONS 80 CASE STUDIES This report is the product of collaboration between Arup’s Foresight + Research + Innovation, Transport Consulting and Urban Design teams as well as other specialist planners, designers and engineers from across our global offices. We are also grateful for the expert contributions from a range of external commentators. Contacts Susan Claris Chris Luebkeman Associate Director Arup Fellow and Director Transport Consulting Global Foresight + Research + Innovation [email protected] [email protected] Demetrio Scopelliti Josef Hargrave Architect Associate Masterplanning and Urban Design Foresight + Research + Innovation [email protected] [email protected] Local Contact Stefano Recalcati Associate Masterplanning and Urban Design [email protected] Released June 2016 #walkingworld 13 Fitzroy Street London W1T 4BQ arup.com driversofchange.com © Arup 2016 Contents Foreword 7 Executive summary 9 Introduction 14 Benefits 28 Envisioning walkable cities 98 Achieving walkable cities 110 Next steps 153 References 154 Acknowledgements 165 5 higher experience parking walk neighbourhoods community route increasing culture places strategies improving travel change research policies air needs road work study temporary services route digital cycling efcient physical local time potential order accessible transport improve attractive context investment city risk towards space walkable use people world live urban data -

Exploring Decimation Filters

High Frequency Design Decimation Filters Exploring Decimation Filters By Arash Loloee, Ph.D. Introduction An overview of Delta-sigma analog-to-digital converters (ADCs) are among the most decimation filters, along popular converters that are suitable for low-to-medium speed and high- with their operation and resolution applications such as communications systems, weighing scales requirements. and precision measurement applications. These converters use clock overs- ampling along with noise-shaping to achieve high signal-to-noise ratio (SNR) and, thus, higher effective number of bits (ENOB). Noise-shaping occurs when noise is pushed to higher frequencies that are out of the band of interest. When the out-of-band noise is chopped off, SNR increases. After noise-shaping, the sampling rate is reduced back to its Nyquist rate by means of decimation filters. In fact, delta-sigma converters can be partitioned into two main building blocks: modulator and decimation filters. With a good understanding of these building blocks you can arrive at a robust and efficient design. Each of these main build- ing blocks, in turn, is made of several different building blocks themselves. Unlike conventional converters that sample the analog input signal at Nyquist frequency or slightly higher, delta-sigma modulators, regardless of their order, sample the input data at rates that are much higher than Nyquist rate. The oversampling ratio (OSR) usually is expressed in the form of 2m, where m=1,2,3,… The modulator is an analog block in nature that needs little accuracy in its components. Thus, the burden of design can be pushed onto the decimation filter.