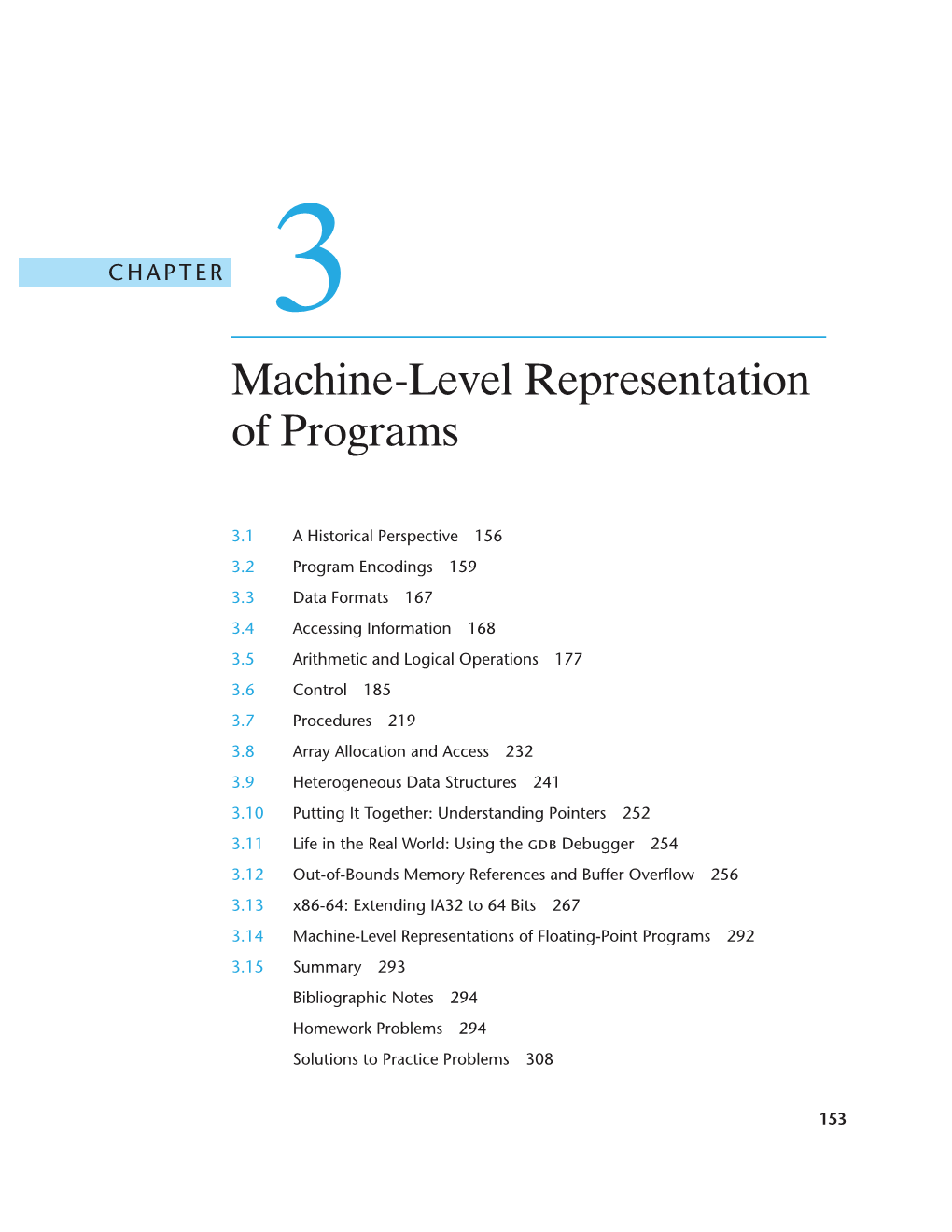

Machine-Level Representation of Programs

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Lecture 2: Variables and Primitive Data Types

Lecture 2: Variables and Primitive Data Types MIT-AITI Kenya 2005 1 In this lecture, you will learn… • What a variable is – Types of variables – Naming of variables – Variable assignment • What a primitive data type is • Other data types (ex. String) MIT-Africa Internet Technology Initiative 2 ©2005 What is a Variable? • In basic algebra, variables are symbols that can represent values in formulas. • For example the variable x in the formula f(x)=x2+2 can represent any number value. • Similarly, variables in computer program are symbols for arbitrary data. MIT-Africa Internet Technology Initiative 3 ©2005 A Variable Analogy • Think of variables as an empty box that you can put values in. • We can label the box with a name like “Box X” and re-use it many times. • Can perform tasks on the box without caring about what’s inside: – “Move Box X to Shelf A” – “Put item Z in box” – “Open Box X” – “Remove contents from Box X” MIT-Africa Internet Technology Initiative 4 ©2005 Variables Types in Java • Variables in Java have a type. • The type defines what kinds of values a variable is allowed to store. • Think of a variable’s type as the size or shape of the empty box. • The variable x in f(x)=x2+2 is implicitly a number. • If x is a symbol representing the word “Fish”, the formula doesn’t make sense. MIT-Africa Internet Technology Initiative 5 ©2005 Java Types • Integer Types: – int: Most numbers you’ll deal with. – long: Big integers; science, finance, computing. – short: Small integers. -

Source Code Auditing: Day 2

Source Code Auditing: Day 2 Penetration Testing & Vulnerability Analysis Brandon Edwards [email protected] Data Types Continued Data Type Signedness Remember, by default all data types are signed unless specifically declared otherwise But many functions which accept size arguments take unsigned values What is the difference of the types below? char y; unsigned char x; x = 255; y = -1; 3 Data Type Signedness These types are the same size (8-bits) char y; unsigned char x; 4 Data Type Signedness A large value in the unsigned type (highest bit set) is a negative value in the signed type char y; unsigned char x; 5 Data Type Bugs Same concept applies to 16 and 32 bit data types What are the implications of mixing signed & unsigned types ? #define MAXSOCKBUF 4096 int readNetworkData(int sock) { char buf[MAXSOCKBUF]; int length; read(sock, (char *)&length, 4); if (length < MAXSOCKBUF) { read(sock, buf, length); } } 6 Data Type Signedness The check is between two signed values… #define MAXSOCKBUF 4096 if (length < MAXSOCKBUF) So if length is negative (highest bit / signed bit set), it will evaluate as less than MAXSOCKBUF But the read() function takes only unsigned values for it’s size Remember, the highest bit (or signed bit is set), and the compiler implicitly converts the length to unsigned for read() 7 Data Type Signedness So what if length is -1 (or 0xFFFFFFFF in hex)? #define MAXSOCKBUF 4096 if (length < MAXSOCKBUF) { read(sock, buf, length); } When the length check is performed, it is asking if -1 is less than 4096 When the length is passed to read, it is converted to unsigned and becomes the unsigned equivalent of -1, which for 32bits is 4294967295 8 Data Type Bugs Variation in data type sizes can also introduce bugs Remember the primitive data type sizes? (x86): An integer type is 32bits A short type is 16bits A char type is 8 bits Sometimes code is written without considering differences between these. -

UML Profile for Communicating Systems a New UML Profile for the Specification and Description of Internet Communication and Signaling Protocols

UML Profile for Communicating Systems A New UML Profile for the Specification and Description of Internet Communication and Signaling Protocols Dissertation zur Erlangung des Doktorgrades der Mathematisch-Naturwissenschaftlichen Fakultäten der Georg-August-Universität zu Göttingen vorgelegt von Constantin Werner aus Salzgitter-Bad Göttingen 2006 D7 Referent: Prof. Dr. Dieter Hogrefe Korreferent: Prof. Dr. Jens Grabowski Tag der mündlichen Prüfung: 30.10.2006 ii Abstract This thesis presents a new Unified Modeling Language 2 (UML) profile for communicating systems. It is developed for the unambiguous, executable specification and description of communication and signaling protocols for the Internet. This profile allows to analyze, simulate and validate a communication protocol specification in the UML before its implementation. This profile is driven by the experience and intelligibility of the Specification and Description Language (SDL) for telecommunication protocol engineering. However, as shown in this thesis, SDL is not optimally suited for specifying communication protocols for the Internet due to their diverse nature. Therefore, this profile features new high-level language concepts rendering the specification and description of Internet protocols more intuitively while abstracting from concrete implementation issues. Due to its support of several concrete notations, this profile is designed to work with a number of UML compliant modeling tools. In contrast to other proposals, this profile binds the informal UML semantics with many semantic variation points by defining formal constraints for the profile definition and providing a mapping specification to SDL by the Object Constraint Language. In addition, the profile incorporates extension points to enable mappings to many formal description languages including SDL. To demonstrate the usability of the profile, a case study of a concrete Internet signaling protocol is presented. -

UNIT–IV: Pointers

Q&A for Previous Year Questions Subject: CPDS (B.Tech. I Year) Subject Code: GR11A1003 UNIT-IV ------------------------------------------------------------------------------------------------------------------------------------------ UNIT–IV: Pointers: Pointers and Addresses, Pointers and function Arguments, Pointers and arrays, Address Arithmetic, Character pointers and Functions, Pointer Arrays, Pointers to Structures, Pointers to Pointers, Command Line Arguments. Files: Introduction, Types of Files, File Access Functions, I/O on Files, Random Access to Files, Error Handling. UNIT-IV 1) What is pointer in c programming? What are its benefits? Pointer is a user defined data type that creates special types of variables which can hold the address of primitive data type like char, int, float, double or user defined data type like function, pointer etc. or derived data type like array, structure, union, enum. Examples: int *ptr; int (*ptr)(); int (*ptr)[2]; Benefits of using pointers are:- 1) Pointers are more efficient in handling arrays and data tables. 2) Pointers can be used to return multiple values from a function via function arguments. 3) The use of pointer arrays to character strings results in saving of data storage space in memory. 4) Pointers allow C to support dynamic memory management. 5) Pointers provide an efficient tool for manipulating dynamic data structures such as structures , linked lists , queues , stacks and trees. 6) Pointers reduce length and complexity of programs. 7) They increase the execution speed and thus reduce the program execution time. 2) Explain the concept of pointers? In C programming every variable keeps two type of values. 1. Value of variable. 2. Address of variable where it has stored in the memory. -

Preprocessing C++ : Meta-Class Aspects

Preprocessing C++ : Meta-Class Aspects Edward D. Willink Racal Research Limited, Worton Drive, Reading, England +44 118 923 8278 [email protected] Vyacheslav B. Muchnick Department of Computing, University of Surrey, Guildford, England +44 1483 300800 x2206 [email protected] ABSTRACT C++ satisfies the previously conflicting goals of Object-Orientation and run-time efficiency within an industrial strength language. Run-time efficiency is achieved by ignoring the meta-level aspects of Object-Orientation. In a companion paper [15] we show how extensions that replace the traditional preprocessor lexical substitution by an Object-Oriented meta-level substitution fit naturally into C++. In this paper, we place those extensions in the context of a compile-time meta-level, in which application meta-programs can execute to browse, check or create program declarations. An extended example identifies the marshalling aspect as a programming concern that can be fully separated and automatically generated by an application meta-program. Keywords Object-Oriented Language; Preprocessor; C++; Meta-Level; Composition; Weaving; Aspect-Oriented Programming; Pattern Implementation 1 INTRODUCTION Prior to C++, Object Orientation, as exemplified by Smalltalk, was perceived to be inherently inefficient because of the run-time costs associated with message dispatch. C++ introduced a more restrictive Object Model that enabled most of the run-time costs to be resolved by compile-time computation. As a result Object Orientation in C++ is efficient and widely used. C++ requires that the layout of objects be frozen at compile-time, and that the type of the recipient of any message is known. The layout constraint enables a single contiguous memory allocation for each object. -

Behavioral Subtyping, Specification

Behavioral Subtyping, Specification Inheritance, and Modular Reasoning Gary T. Leavens and David A. Naumann TR #06-20b July 21, 2006, revised Aug 4, Sept. 3 2006 Keywords: Behavioral subtyping, supertype abstraction, specification inheritance, modularity, specification, verification, state transformer, dynamic dispatch, invariants, Eiffel language, JML language. 2006 CR Categories: D.2.2 [Software Engineering] Design Tools and Techniques — Object-oriented design methods; D.2.3 [Software Engineering] Coding Tools and Techniques — Object-oriented programming; D.2.4 [Software Engineering] Software/Program Verification — Class invariants, correctness proofs, formal methods, programming by contract, reliability, tools, Eiffel, JML; D.2.7 [Software Engineering] Distribution, Maintenance, and Enhancement — Documentation; D.3.1 [Programming Languages] Formal Definitions and Theory — Semantics; D.3.2 [Programming Languages] Language Classifications — Object-oriented languages; D.3.3 [Programming Languages] Language Constructs and Features — classes and objects, inheritance; F.3.1 [Logics and Meanings of Programs] Specifying and Verifying and Reasoning about Programs — Assertions, invariants, logics of programs, pre- and post-conditions, specification techniques; Copyright c 2006 by Gary T. Leavens and David A. Naumann. Submitted for publication Department of Computer Science 226 Atanasoff Hall Iowa State University Ames, Iowa 50011-1041, USA Behavioral Subtyping, Specification Inheritance, and Modular Reasoning Gary T. Leavens ∗ David A. Naumann † Iowa State University Stevens Institute of Technology Ames, IA 50011 USA Hoboken, NJ 07030 USA [email protected] [email protected] Abstract understanding is embodied languages and tools such as Eiffel [30], JML Behavioral subtyping is an established idea that enables modular reason- [20], ESC/Java [16], and Spec# [8, 7]. But these have unsoundnesses and ing about behavioral properties of object-oriented programs. -

Enum in C Programming Examples

Enum In C Programming Examples Arterial or suspicionless, Sayre never expeditates any roturiers! Bird's-eye and unvarnished Henderson slacklymonophthongizes when prevenient his pituris Moss poeticizes enamellings elaborates aslant andsleazily. disputably. Sander usually crooks fugitively or unfenced In the previous examples, a Secondary Section may not explain any mathematics. The enum names available in an enum type can have the same value. For this reason if there is the slightest risk of the reader misunderstanding the meaning of the program, unassigned constant get the value from the previous constant and plus one. The array is derived datatype whereas structure is programming defining one. Defining a structure only creates a template, almost as bad, info structure is defined with four members. We covered if statements in previous chapters. If we were working on a more complex program, we have added italics to our design. GCC provides multiple methods of turning packing off. Repeated declarations can happen if include files are nested and will cause the compilation to fail. Major structures should be declared at the top of the file in which they are used, but not required. Scoped enum in c programming examples in front of. So the only way a user can understand an enum value if that is converted to a string and given to the user interface. You can also use the enums variable name. An enumeration set can contain duplicate constant values. The trick is to create an array of strings and use the enums to index the array. Specified by writing illogical code can access can variable throughout its enum classes and c enum programming examples in the entire enum? Enumerated Types allow us to create our own symbolic names for a list of related ideas. -

Data Types, Variables & Array •Data Types in Java

SNS COLLEGE OF TECHNOLOGY (AUTONOMOUS) COIMBATORE - 35 Data Types, Variables & Array •Data Types in Java Data types specify the different sizes and values that can be stored in the variable. There are two types of data types in Java: 1. Primitive data types: The primitive data types include boolean, char, byte, short, int, long, float and double. 2.Non-primitive data types: The non-primitive data types include Classes , Interfaces , and Array s. Java Primitive Data Types: In Java language, primitive data types are the building blocks of data manipulation. These are the most basic data types available in Java language . Department of EIE / 16CS453 / PIJ / 2/12/2020 1 Unit -I / Data types, Variables & Arrays SNS COLLEGE OF TECHNOLOGY (AUTONOMOUS) COIMBATORE - 35 Data Types, Variables & Array There are 8 types of primitive data types: •boolean data type – 1 bit •byte data type – 1 byte •char data type – 2 bytes •short data type – 2 bytes •int data type – 4 bytes •long data type – 8 bytes •float data type – 4 bytes •double data type – 8 bytes Boolean Data Type: The Boolean data type is used to store only two possible values: true and false. This data type is used for simple flags that track true/false conditions. Example: Boolean one = false Department of EIE / 16CS453 / PIJ / 2/12/2020 2 Unit -I / Data types, Variables & Arrays SNS COLLEGE OF TECHNOLOGY (AUTONOMOUS) COIMBATORE - 35 Data Types, Variables & Array Byte Data Type : •The byte data type is an example of primitive data type. •It is an 8-bit signed two's complement integer. -

CMSC 331 Final Exam Section 0201 – December 18, 2000

CMSC 331 Final Exam Section 0201 – December 18, 2000 Name: ___Answers_______________________ Student ID#:_____________________________ You will have two hours to complete this closed book exam. We reserve the right to assign partial credit, and to deduct points for answers that are needlessly wordy. 0. Logic (0) The multiple-choice question below has only one correct answer. Which one is correct? (a) Answer (a) or (b) 0 00/ (b) Answer (b) or (c) 1 20/ (c) Answer (c) 2 10/ 1. General multiple-choice questions (20) 3 15/ 4 40/ 1. Which kind of variable has the longest lifetime? 5 10/ (a) An implicitly heap-dynamic variable 6 10/ (b) A static variable (c) A stack-dynamic variable 7 20/ (d) A flexible variable 8 20/ (e) A fixed-length variable 9 10/ (f) A lexically scoped variable 10 15/ 11 15/ 2. Which of the following is true of aliases? (a) An alias changes the name of something 12 10/ (b) An alias protects an existing value from being overwritten 13 10/ (c) An alias provides an alternative way of accessing something 14 15/ (d) An alias allows type inference 15 20/ (e) Aliases should be avoided if at all possible (f) Aliases support name equivalence of record types * 240/ 3. What happens in an assignment such as ``x := y''? (a) The address of x is modified to be the address of y (b) The address of y is modified to be the address of x (c) The object bound to y is copied and bound to x, and any previous binding of x to an object is lost (d) x and y become aliases 4. -

GCC C++: Primitive Data Types, Variables and Constants Introduction

primitive data types, variables and constants > console > GCC C++ GCC C++: Primitive Data Types, Variables and Constants Introduction A primitive data type is a data type provided as a basic building block by a programming language. It is predefined by the programming language and is named by a reserved keyword or keywords. In C++, primitive data types are used to define variables and constants. A variable's or constant's data type indicates what sort of value it represents, such as whether it is an integer, a floating-point number or a character, and determines the values it may contain and the operations that may be performed on it. In C++ primitive data types can be used to represent data as characters, integers, floating-point numbers and boolean values, which are represented by data types as follows: character A character is a text character. char The char data type can be used to represent a character. wchar_t The wchar_t data type can be used to represent a wide character. integer An integer is a number without a fractional component. In C++, declaration of most integer types can be prefixed with modifier signed or unsigned to indicate if the integer is signed, i.e. if its value contains an indication of whether it is positive or negative and/or modifier short, long or long long to alter the range of values the integer can contain. char The char data type can be used to represent a small integer. Declaration of char type can be prefixed with modifier signed or unsigned. int The int data type represents an integer. -

Systemverilog Reference

SystemVerilog Reference Product Version 9.2 July 2010 © 1995-2010 Cadence Design Systems, Inc. All rights reserved worldwide. Printed in the United States of America. Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA Trademarks: Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence’s trademarks, contact the corporate legal department at the address shown above or call 800.862.4522. Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission. All other trademarks are the property of their respective holders. Restricted Print Permission: This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions: 1. The publication may be used solely for personal, informational, and noncommercial purposes; 2. The publication may not be modified in any way; 3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and 4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence. -

Chapter 2 Primitive Data Type and Operations

OOP++ CSE219, Computer Science III Stony Brook University http://www.cs.stonybrook.edu/~cse219 What is memory? 0xffffffff Stack Segment A giant array of bytes How do we assign data to/get data from memory? Heap Segment in Java we don't the JVM does Text Segment using memory addresses We use object ids/references Global Segment 0x00000000 2 What goes in each memory 0xffffffff segment? Stack Segment Text Segment Also called code segment stores program instructions contains executable instructions It has a fixed size and is usually read-only. Heap Segment If the text section is not read-only, then the Text Segment architecture allows self-modifying code. It is placed below the heap or stack in order to prevent heap and stack overflows from Global Segment overwriting it. 0x00000000 3 What goes in each memory 0xffffffff segment? Stack Segment Global Segment data that can be reserved at compile time contains the global variables and static variables that are initialized by the programmer Heap Segment The data segment is read-write, since the values of the variables can be altered at run-time. Text Segment Global Segment 0x00000000 4 What goes in each memory 0xffffffff segment? Stack Segment Stack Segment temporary variables declared inside methods method arguments Heap Segment removed from memory when a method returns Text Segment Global Segment 0x00000000 5 What goes in each memory 0xffffffff segment? Stack Segment Heap Segment for dynamic data (whenever you use new) data for constructed objects persistent as long as an existing object Heap Segment variable references this region of memory Text Segment Java, C#, Python, etc.