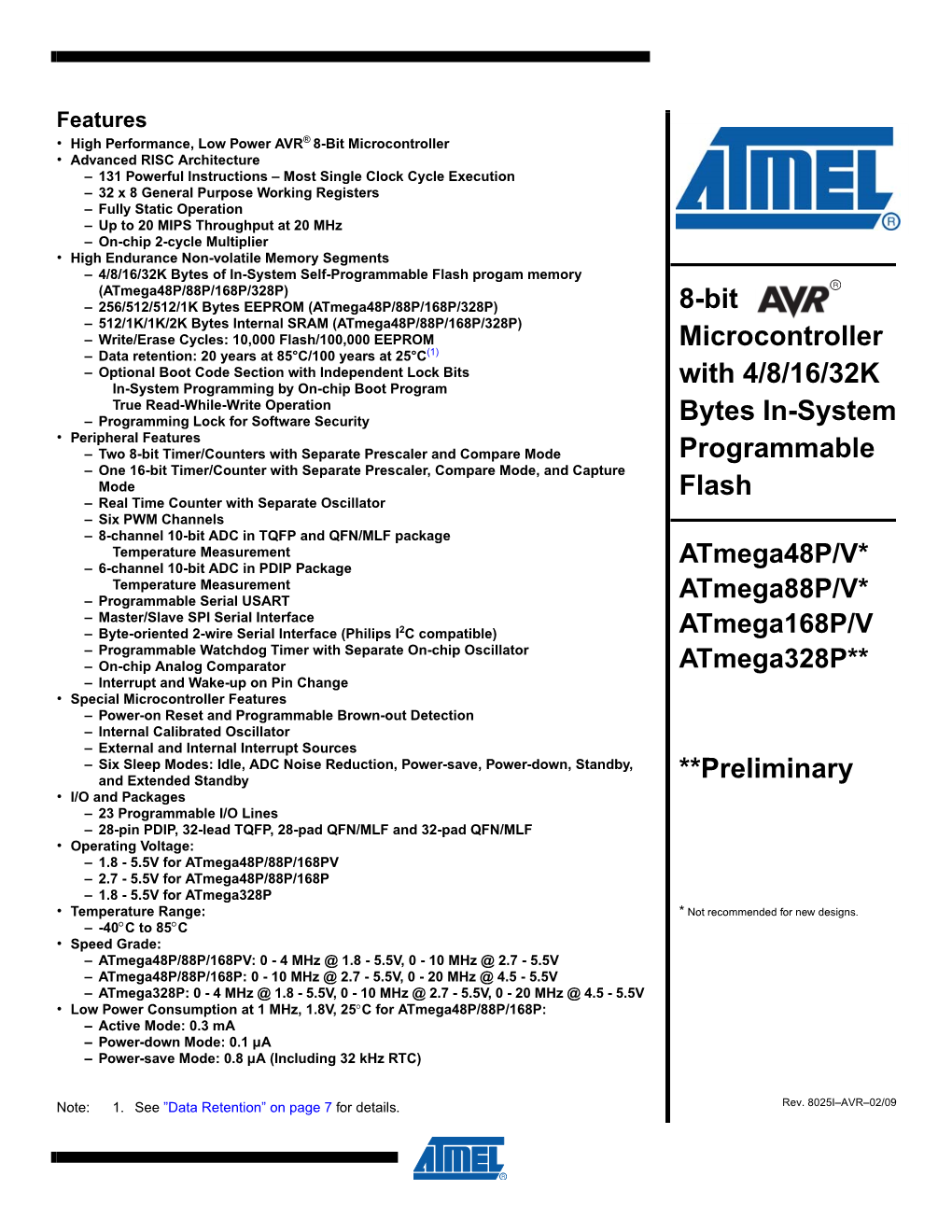

Atmega328p Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Arduino Duemilanove W/ Atmega328

Arduino Duemilanove w/ Atmega328 Overview The Arduino Duemilanove ("2009") is a microcontroller board based on the ATmega168 (datasheet) or ATmega328 (datasheet). It has 14 digital input/output pins (of which 6 can be used as PWM outputs), 6 analog inputs, a 16 MHz crystal oscillator, a USB connection, a power jack, an ICSP header, and a reset button. It contains everything needed to support the microcontroller; simply connect it to a computer with a USB cable or power it with a AC-to-DC adapter or battery to get started. "Duemilanove" means 2009 in Italian and is named after the year of its release. The Duemilanove is the latest in a series of USB Arduino boards; for a comparison with previous versions, see the index of Arduino boards. Summary Microcontroller ATmega168 Operating Voltage 5V Input Voltage 7-12V (recommended) Input Voltage (limits) 6-20V Digital I/O Pins 14 (of which 6 provide PWM output) Analog Input Pins 6 DC Current per I/O Pin 40 mA DC Current for 3.3V Pin 50 mA 16 KB (ATmega168) or 32 KB (ATmega328) of which 2 KB used by Flash Memory bootloader SRAM 1 KB (ATmega168) or 2 KB (ATmega328) EEPROM 512 bytes (ATmega168) or 1 KB (ATmega328) Clock Speed 16 MHz Schematic & Reference Design EAGLE files: arduino-duemilanove-reference-design.zip Schematic: arduino-duemilanove-schematic.pdf Power The Arduino Duemilanove can be powered via the USB connection or with an external power supply. The power source is selected automatically. External (non-USB) power can come either from an AC-to-DC adapter (wall-wart) or battery. -

Arduino Uno SMD

Arduino Uno SMD Overview The Arduino Uno SMD is a version of the Arduino Uno, but uses an surface mount version of the Atmega328P instead of the through-hole version. This version was made in response to a shortage in supply of the through-hole Atmega328P. The board is based on the ATmega328 (datasheet). It has 14 digital input/output pins (of which 6 can be used as PWM outputs), 6 analog inputs, a 16 MHz crystal oscillator, a USB connection, a power jack, an ICSP header, and a reset button. It contains everything needed to support the microcontroller; simply connect it to a computer with a USB cable or power it with a AC-to- DC adapter or battery to get started. The Uno differs from all preceding boards in that it does not use the FTDI USB-to-serial driver chip. Instead, it features the Atmega8U2 programmed as a USB-to-serial converter. "Uno" means one in Italian and is named to mark the upcoming release of Arduino 1.0. The Uno and version 1.0 will be the reference versions of Arduino, moving forward. The Uno is the latest in a series of USB Arduino boards, and the reference model for the Arduino platform; for a comparison with previous versions, see the index of Arduino boards. Summary Microcontroller ATmega328 Operating Voltage 5V Input Voltage (recommended) 7-12V Input Voltage (limits) 6-20V Digital I/O Pins 14 (of which 6 provide PWM output) Analog Input Pins 6 DC Current per I/O Pin 40 mA DC Current for 3.3V Pin 50 mA Flash Memory 32 KB (ATmega328) of which 0.5 KB used by bootloader SRAM 2 KB (ATmega328) EEPROM 1 KB (ATmega328) Clock Speed 16 MHz Schematic & Reference Design EAGLE files: arduino-uno-smd-reference-design.zip Schematic: arduino-uno-smd-schematic.pdf Power The Arduino Uno can be powered via the USB connection or with an external power supply. -

Atmega328p Xplained Mini User Guide

USER GUIDE ATmega328P Xplained Mini User Guide Introduction This user guide describes how to get started with the Atmel® ATmega328P Xplained Mini board. The ATmega328P Xplained Mini evalutation kit is a hardware platform to evaluate the Atmel ATmega328P microcontroller. The evaluation kit comes with a fully integrated debugger that provides seamless integration with Atmel Studio 6.2 (and later version). The kit provides access to the features of the ATmega328P enabling easy integration of the device in a custom design. 42287A-MCU-05/2014 Table of Contents Introduction .................................................................................... 1 1. Getting Started ........................................................................ 3 1.1. Features .............................................................................. 3 1.2. Design Documentation and Related Links .................................. 3 1.3. Board Assembly .................................................................... 3 1.3.1. In Customer Development Assembly ............................. 3 1.3.2. Connecting an Arduino Shield ..................................... 3 1.3.3. Standalone Node ...................................................... 3 1.4. Connecting the Kit ................................................................. 3 1.4.1. Connect the Kit to Atmel Studio ................................... 3 1.4.2. Connect the Target UART to the mEBDG COM Port ......... 3 1.5. Programming and Debugging ................................................. -

Getting Started with STK200 Dragon Introduction This Guide Is Designed to Get You up and Running with Main Software and Hardware

Getting Started with STK200 Dragon Introduction This guide is designed to get you up and running with main software and hardware. As you work through it, there could be lots of details you do not understand, but these are covered in books and other documentation that you can read later. The main software package is AVRStudio, which is Atmel’s Integrated Development Environment or IDE. There is also a plugin C Compiler module called WinAVR that compiles C programs within AVRStudio. The Kanda installer will install these packages and copy documentation to a folder on your hard drive. Default install path is C:\Program Files\STK200 Dragon AVRStudio has its own Atmel-AVR Tools folder in Program Files, and can be run from there or you can run from desktop icon. WinAVR never needs to be run directly, only from AVRStudio. The AVRStudio IDE is designed for writing source code, in C (.c files) or assembler (.asm files). These are then built or compiled into object code (.hex files) for programming into the AVR using ISP or debug files (.elf files) to step through the code. The AVR Dragon hardware is a programmer and In Circuit Emulator (ICE) in one tool. Once source code is built, it can be programmed into the AVR using ISP, which will just run the code or it can be set in Debug mode (using DebugWire or JTAG )that allows you to examine the code operation to find bugs. There are two Debug methods depending on the AVR device you are using • JTAG Mode for AVR devices with 40-pins or more • DebugWire for smaller pin-count devices. -

Vax 6135 Car Vax Uk - Service Parts List

VAX 6135 CAR VAX UK - SERVICE PARTS LIST Item Vax Part No. Description Price Code Service Item Item Vax Part No. Description Price Code Service Item 2 1-2-31-01-006 FILTER-FOAM-EXHAUST S1 CS 34 1-2-30-01-015 SEAL-FILTER/RESERVOIR K1 S 5 1-2-11-04-007 CABLE CLAMP L1 CS 35 1-3-15-03-007 FILTER HSG ASSY-UNIV-BLACK T3 S 29 1-2-31-01-002 FILTER DISC-BONDINI A1 CS 39 1-2-14-02-001 BALL VALVE N1 S 32 1-2-31-01-007 FILTER -FIBRE-MOULDED X1 CS 40 1-3-09-06-007 RESERVOIR ASSY-UNIV-BLACK W3 S 44 1-3-13-02-001 UPHOLSTERY TOOL Y1 CS 41 1-2-30-02-002 SEAL-CONICAL DUCT D2 S 47 1-2-39-01-010 CREVICE TOOL Y1 CS 42 1-2-30-02-003 SEAL-EXHAUST D2 S 48 1-3-13-01-001 DUSTBRUSH H2 CS 43 1-2-124731-12 RECOVERY BUCKET/SPIDER ASSY Z3 S 50 1-2-13-02-002 TUBE-EXTN-STAINLESS B3 CS 45 1-2-32-01-002 CASTOR-TWO WHEEL X1 S 52 1-3-18-01-022 HOSE & GRIP ASSY W3 CS 60 1-9-124423-00 TUBE-PUMP TO QRV A1 S 53 1-9-124962-00 WASH HEAD J3 CS 62 1-1-06-01-073 FEMALE QRV ASSY S2 S 54 1-9-124961-00 FLOOR BRUSH F3 CS 63 1-3-124422-00 ELBOW-QRV-ET408 C2 S 64 1-2-11-03-007 RETAINER CLIP-SPRING H1 CS 65 1-2-13-04-008 INLET TUBE-PVC A1 S 74 1-2-124594-00 UPHOLSTERY WASH TOOL K3 CS 66 1-3-124424-00 FIXING STRAP-ET408 L1 S 75 1-9-125226-00 TURBO TOOL-100mm R3 CS 67 1-7-124677-00 FILTER-WATER-INLET E2 S 77 1-9-125549-00 CREVICE TOOL-EXTRA LONG G2 CS 68 1-5-124419-00 PUMP-ET408 S3 S 101 1-2-124805-00 WATER TUBE ASSY-STRAIGHT Z2 CS 69 1-6-124425-00 SEAL-PUMP ET408 L1 S 3 1-3-124588-03 COVER-ACCESS-B R GREEN X1 NS 99 1-2-07-03-001 DUCT-CONICAL X1 S 6 1-2-36-04-004 CORD PROTECTOR A1 NS 102 -

![Power Debugger [USER GUIDE] 2 Atmel-42696D-Power-Debugger User Guide-10/2016 5.2.5](https://docslib.b-cdn.net/cover/8948/power-debugger-user-guide-2-atmel-42696d-power-debugger-user-guide-10-2016-5-2-5-598948.webp)

Power Debugger [USER GUIDE] 2 Atmel-42696D-Power-Debugger User Guide-10/2016 5.2.5

Programmers and Debuggers Power Debugger USER GUIDE Atmel-42696D-Power-Debugger_User Guide-10/2016 Table of Contents 1. The Atmel Power Debugger...................................................................................... 4 1.1. Kit Contents..................................................................................................................................5 2. Getting Started with the Power Debugger................................................................. 6 3. Connecting the Power Debugger...............................................................................8 3.1. Connecting to AVR and SAM Target Devices...............................................................................8 4. Detailed Use Cases.................................................................................................10 4.1. Low-power Application............................................................................................................... 10 4.1.1. Requirements.............................................................................................................. 10 4.1.2. Initial Hardware Setup................................................................................................. 10 4.1.3. Connections.................................................................................................................12 4.1.4. Disabling the debugWIRE Interface.............................................................................13 4.1.5. Disabling On-board Power Supply on the Xplained -

CS 6290 Chapter 1

Spring 2011 Prof. Hyesoon Kim Xbox 360 System Architecture, „Anderews, Baker • 3 CPU cores – 4-way SIMD vector units – 8-way 1MB L2 cache (3.2 GHz) – 2 way SMT • 48 unified shaders • 3D graphics units • 512-Mbyte DRAM main memory • FSB (Front-side bus): 5.4 Gbps/pin/s (16 pins) • 10.8 Gbyte/s read and write • Xbox 360: Big endian • Windows: Little endian http://msdn.microsoft.com/en-us/library/cc308005(VS.85).aspx • L2 cache : – Greedy allocation algorithm – Different workloads have different working set sizes • 2-way 32 Kbyte L1 I-cache • 4-way 32 Kbyte L1 data cache • Write through, no write allocation • Cache block size :128B (high spatial locality) • 2-way SMT, • 2 insts/cycle, • In-order issue • Separate vector/scalar issue queue (VIQ) Vector Vector Execution Unit Instructions Scalar Scalar Execution Unit • First game console by Microsoft, released in 2001, $299 Glorified PC – 733 Mhz x86 Intel CPU, 64MB DRAM, NVIDIA GPU (graphics) – Ran modified version of Windows OS – ~25 million sold • XBox 360 – Second generation, released in 2005, $299-$399 – All-new custom hardware – 3.2 Ghz PowerPC IBM processor (custom design for XBox 360) – ATI graphics chip (custom design for XBox 360) – 34+ million sold (as of 2009) • Design principles of XBox 360 [Andrews & Baker] - Value for 5-7 years -!ig performance increase over last generation - Support anti-aliased high-definition video (720*1280*4 @ 30+ fps) - extremely high pixel fill rate (goal: 100+ million pixels/s) - Flexible to suit dynamic range of games - balance hardware, homogenous resources - Programmability (easy to program) Slide is from http://www.cis.upenn.edu/~cis501/lectures/12_xbox.pdf • Code name of Xbox 360‟s core • Shared cell (playstation processor) ‟s design philosophy. -

MPC5634M Microcontroller Data Sheet, Rev

Freescale Semiconductor MPC5634M Rev. 9.2, 01/2015 MPC5634M Microcontroller Datasheet This is the MPC5634M Datasheet set consisting of the following files: • MPC5634M Datasheet Addendum (MPC5634M_AD), Rev. 1 • MPC5634M Datasheet (MPC5634M), Rev. 9 © Freescale Semiconductor, Inc., 2015. All rights reserved. Freescale Semiconductor MPC5634M_AD Datasheet Addendum Rev. 1.0, 01/2015 MPC5634M Microcontroller Datasheet Addendum This addendum describes corrections to the MPC5634M Table of Contents Microcontroller Datasheet, order number MPC5634M. 1 Addendum List for Revision 9 . 2 For convenience, the addenda items are grouped by 2 Revision History . 2 revision. Please check our website at http://www.freescale.com/powerarchitecture for the latest updates. The current version available of the MPC5634M Microcontroller Datasheet is Revision 9. © Freescale Semiconductor, Inc., 2015. All rights reserved. 1 Addendum List for Revision 9 4 Table 1. MPC5634M Rev 9 Addendum Location Description Section 4.11, “Temperature In “Temperature Sensor Electrical Characteristics” table, update the Min and Max value of Sensor Electrical “Accuracy” parameter to -20oC and +20oC, respectively. Characteristics”, Page 81 2 Revision History Table 2 provides a revision history for this datasheet addendum document. Table 2. Revision History Table Rev. Number Substantive Changes Date of Release 1.0 Initial release. 12/2014 MPC5634M_AD, Rev. 1.0 2 Freescale Semiconductor How to Reach Us: Information in this document is provided solely to enable system and software Home Page: implementers to use Freescale products. There are no express or implied copyright freescale.com licenses granted hereunder to design or fabricate any integrated circuits based on the Web Support: information in this document. freescale.com/support Freescale reserves the right to make changes without further notice to any products herein. -

Automated Synthesis of Symbolic Instruction Encodings from I/O Samples

Automated Synthesis of Symbolic Instruction Encodings from I/O Samples Patrice Godefroid Ankur Taly Microsoft Research Stanford University PLDI’2012 Page 1 June 2012 Need for Symbolic Instruction Encodings Symbolic Execution is a key l 1 : m o v eax, i n p 1 component of precise binary m o v c l , i n p 2 program analysis tools s h l eax, c l j n z l2 j m p l3 - SAGE, BitBlaze, BAP, etc. l 2 : d i v ebx, eax // Is this safe ? - Static analysis tools / / I s e a x ! = 0 ? l 3 : … PLDI’2012 Page 2 June 2012 Problem: Symbolic Instruction Encoding Bit Vector[X] Instruction Bit Vector[Y] Inp 1 ? Op1 Inpn Opm Problem: Given a processor and an instruction name, symbolically describe the input-output function for the instruction • Express the encoding as bit-vector constraints (ex: SMT-Lib format) PLDI’2012 Page 3 June 2012 So far, only manual solutions… • From the instruction architecture manual (X86, ARM, …) implemented by the processor Limitations: • Tedious, expensive - X86 has more than 300 unique instructions, each with ~10 OPCodes, 2000 pages • Error-prone - Written in English, many corner cases • Imprecise - Spec is often under-specified • Partial - Not all instructions are covered X86 spec for SHLD • Can we trust the spec ? PLDI’2012 Page 4 June 2012 Here: Automated Synthesis Approach Searches for a function f that respects truth table Partial Truth- table S Sample inputs Synthesis Function (C with in-lined engine f assembly) Goals: • As automated as possible so that we can boot-strap a symbolic execution engine on an arbitrary instruction -

Arduino Nano

Arduino Nano Arduino Nano Front Arduino Nano Rear Overview The Arduino Nano is a small, complete, and breadboard-friendly board based on the ATmega328 (Arduino Nano 3.0) or ATmega168 (Arduino Nano 2.x). It has more or less the same functionality of the Arduino Duemilanove, but in a different package. It lacks only a DC power jack, and works with a Mini-B USB cable instead of a standard one. The Nano was designed and is being produced by Gravitech. Schematic and Design Arduino Nano 3.0 (ATmega328): schematic, Eagle files. Arduino Nano 2.3 (ATmega168): manual (pdf), Eagle files. Note: since the free version of Eagle does not handle more than 2 layers, and this version of the Nano is 4 layers, it is published here unrouted, so users can open and use it in the free version of Eagle. Specifications: Microcontroller Atmel ATmega168 or ATmega328 Operating Voltage (logic 5 V level) Input Voltage 7-12 V (recommended) Input Voltage (limits) 6-20 V Digital I/O Pins 14 (of which 6 provide PWM output) Analog Input Pins 8 DC Current per I/O Pin 40 mA 16 KB (ATmega168) or 32 KB (ATmega328) of which 2 KB used by Flash Memory bootloader SRAM 1 KB (ATmega168) or 2 KB (ATmega328) EEPROM 512 bytes (ATmega168) or 1 KB (ATmega328) Clock Speed 16 MHz Dimensions 0.73" x 1.70" Power: The Arduino Nano can be powered via the Mini-B USB connection, 6-20V unregulated external power supply (pin 30), or 5V regulated external power supply (pin 27). -

Toshiba 32-Bit Arm Core-Based Microcontroller Product Guide

SUBSIDIARIES AND AFFILIATES (As of July 1, 2017) Toshiba America Toshiba Electronics Europe GmbH Toshiba Electronics Asia, Ltd. Nov. 2017 Semiconductor Catalog Nov. 2017 Electronic Components, Inc. • Düsseldorf Head Office Tel: 2375-6111 Fax: 2375-0969 • Irvine, Headquarters Tel: (0211)5296-0 Fax: (0211)5296-400 Toshiba Electronics (China) Co., Ltd. BCE0085H Tel: (949)462-7700 Fax: (949)462-2200 • France Branch • Shanghai Head Office • Buffalo Grove (Chicago) Tel: (1)47282181 Tel: (021)6139-3888 Fax: (021)6190-8288 Tel: (847)484-2400 Fax: (847)541-7287 • Italy Branch • Beijing Branch • Duluth/Atlanta Tel: (039)68701 Fax:(039)6870205 Tel: (010)6590-8796 Fax: (010)6590-8791 Tel: (404)639-9520 Fax: (404)634-4434 • Munich Office • Chengdu Branch • El Paso Tel: (089)20302030 Fax: (089)203020310 Tel: (028)8675-1773 Fax: (028)8675-1065 Tel: (915)533-4242 • Spain Branch • Hangzhou Office • Marlborough Tel: (91)660-6794 Tel: (0571)8717-5004 Fax: (0571)8717-5013 Tel: (508)481-0034 Fax: (508)481-8828 • Sweden Branch • Nanjing Office • Parsippany Tel: (08)704-0900 Fax: (08)80-8459 Tel: (025)8689-0070 Fax: (025)5266-5106 Tel: (973)541-4715 Fax: (973)541-4716 • U.K. Branch • Qingdao Branch 32-Bit Microcontrollers 32-Bit Microcontrollers • San Jose Tel: (1932)841600 Tel: (532)8579-3328 Fax: (532)8579-3329 Tel: (408)526-2400 Fax: (408)526-2410 Toshiba Electronics Asia (Singapore) Pte. Ltd. • Shenzhen Branch • Wixom (Detroit) Tel: (65)6278-5252 Fax: (65)6271-5155 Tel: (0755)3686-0880 Fax: (0755)3686-0816 Tel: (248)347-2607 Fax: (248)347-2602 Toshiba Electronics Service (Thailand) Co., Ltd. -

Digital and System Design

Digital System Design — Use of Microcontroller RIVER PUBLISHERS SERIES IN SIGNAL, IMAGE & SPEECH PROCESSING Volume 2 Consulting Series Editors Prof. Shinsuke Hara Osaka City University Japan The Field of Interest are the theory and application of filtering, coding, trans- mitting, estimating, detecting, analyzing, recognizing, synthesizing, record- ing, and reproducing signals by digital or analog devices or techniques. The term “signal” includes audio, video, speech, image, communication, geophys- ical, sonar, radar, medical, musical, and other signals. • Signal Processing • Image Processing • Speech Processing For a list of other books in this series, see final page. Digital System Design — Use of Microcontroller Dawoud Shenouda Dawoud R. Peplow University of Kwa-Zulu Natal Aalborg Published, sold and distributed by: River Publishers PO box 1657 Algade 42 9000 Aalborg Denmark Tel.: +4536953197 EISBN: 978-87-93102-29-3 ISBN:978-87-92329-40-0 © 2010 River Publishers All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, mechanical, photocopying, recording or otherwise, without prior written permission of the publishers. Dedication To Nadia, Dalia, Dina and Peter D.S.D To Eleanor and Caitlin R.P. v This page intentionally left blank Preface Electronic circuit design is not a new activity; there have always been good designers who create good electronic circuits. For a long time, designers used discrete components to build first analogue and then digital systems. The main components for many years were: resistors, capacitors, inductors, transistors and so on. The primary concern of the designer was functionality however, once functionality has been met, the designer’s goal is then to enhance per- formance.