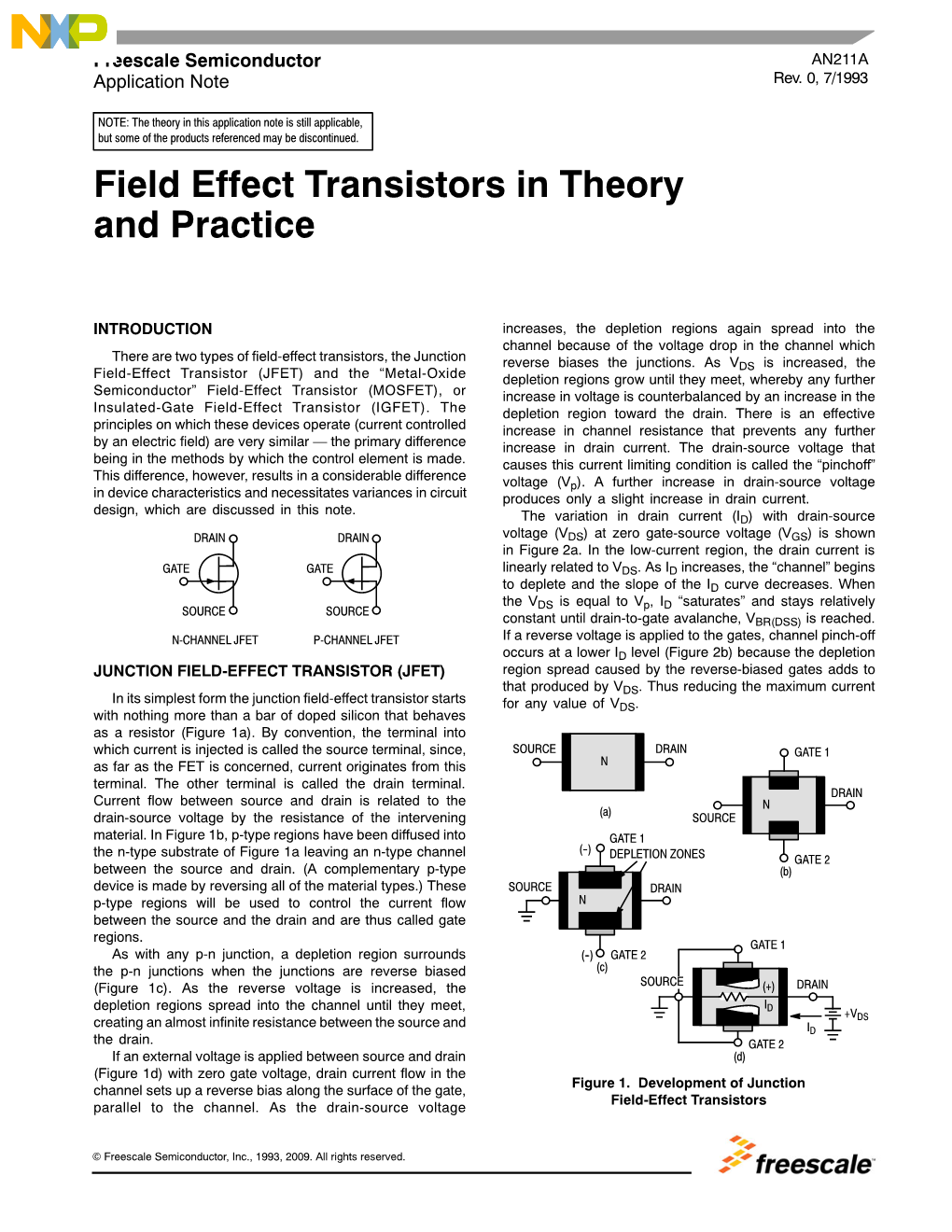

Field Effect Transistors in Theory and Practice Application Note

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Using Rctime to Measure Resistance

Basic Express Application Note Using RCtime to Measure Resistance Introduction One common use for I/O pins is to measure the analog value of a variable resistance. Although a built-in ADC (Analog to Digital Converter) is perhaps the easiest way to do this, it is also possible to use a digital I/O pin. This can be useful in cases where you don't have enough ADC channels, or if a particular processor doesn't have ADC capability. Procedure RCtime BasicX provides a special procedure called RCtime for this purpose. RCtime measures the time it takes for a pin to change state to a defined value. By connecting a fixed capacitor and a variable resistor in an RC circuit, you can use an I/O pin to measure the value of the variable resistor, which might be a device such as a potentiometer or thermistor. There are two common ways to wire an RCtime system. The first is to tie the variable resistor to ground. Figure 1 shows this configuration. The advantage here is less chance of damage from static electricity: Figure 1 Figure 2 The second configuration is shown in Figure 2. Here we use the opposite connection, where the capacitor C is tied to ground and the variable resistor RV is tied to 5 volts: In both circuits resistor R1 is there to protect the BasicX chip's output driver from driving too much current when charging the capacitor. To take a sample, the capacitor is first discharged by taking the pin to the correct state. In the case of Figure 1, the pin needs to be taken high (+5 V) to produce essentially 0 volts across the capacitor, which causes it to discharge. -

LSK489 Application Note

LSK489 Application Note Low Noise Dual Monolithic JFET Bob Cordell Introduction For circuits designed to work with high impedance sources, ranging from electrometers to microphone preamplifiers, the use of a low-noise, high-impedance device between the input and the op amp is needed in order to optimize performance. At first glance, one of Linear Systems’ most popular parts, the LSK389 ultra-low-noise dual JFET would appear to be a good choice for such an application. The part’s high input impedance (1 T Ω) and low noise (1 nV/ √Hz at 1kHz and 2mA drain current) enables power transfer while adding almost no noise to the signal. But further examination of the LSK389’s specification shows an input capacitance of over 20pF. This will cause intermodulation distortion as the circuit’s input signal increases in frequency if the source impedance is high. This is because the JFET junction capacitances are nonlinear. This will be especially the case where common source amplifier arrangements allow the Miller effect to multiply the effective value of the gate-drain capacitance. Further, the LSK389’s input impedance will fall to a lower value as the frequency increases relative to a part with lower input capacitance. A better design choice is Linear Systems’ new offering, the LSK489. Though the LSK489 has slightly higher noise (1.5 nV/ √Hz vs. 1.0 nV/ √Hz) its much lower input capacitance of only 4pF means that it will maintain its high input impedance as the frequency of the input signal rises. More importantly, using the lower-capacitance LSK489 will create a circuit that is much less susceptible to intermodulation distortion than one using the LSK389. -

A GUIDE to USING FETS for SENSOR APPLICATIONS by Ron Quan

Three Decades of Quality Through Innovation A GUIDE TO USING FETS FOR SENSOR APPLICATIONS By Ron Quan Linear Integrated Systems • 4042 Clipper Court • Fremont, CA 94538 • Tel: 510 490-9160 • Fax: 510 353-0261 • Email: [email protected] A GUIDE TO USING FETS FOR SENSOR APPLICATIONS many discrete FETs have input capacitances of less than 5 pF. Also, there are few low noise FET input op amps Linear Systems that have equivalent input noise voltages density of less provides a variety of FETs (Field Effect Transistors) than 4 nV/ 퐻푧. However, there are a number of suitable for use in low noise amplifier applications for discrete FETs rated at ≤ 2 nV/ 퐻푧 in terms of equivalent photo diodes, accelerometers, transducers, and other Input noise voltage density. types of sensors. For those op amps that are rated as low noise, normally In particular, low noise JFETs exhibit low input gate the input stages use bipolar transistors that generate currents that are desirable when working with high much greater noise currents at the input terminals than impedance devices at the input or with high value FETs. These noise currents flowing into high impedances feedback resistors (e.g., ≥1MΩ). Operational amplifiers form added (random) noise voltages that are often (op amps) with bipolar transistor input stages have much greater than the equivalent input noise. much higher input noise currents than FETs. One advantage of using discrete FETs is that an op amp In general, many op amps have a combination of higher that is not rated as low noise in terms of input current noise and input capacitance when compared to some can be converted into an amplifier with low input discrete FETs. -

Memristor-The Future of Artificial Intelligence L.Kavinmathi, C.Gayathri, K.Kumutha Priya

International Journal of Scientific & Engineering Research, Volume 5, Issue 4, April-2014 358 ISSN 2229-5518 Memristor-The Future of Artificial Intelligence L.kavinmathi, C.Gayathri, K.Kumutha priya Abstract- Due to increasing demand on miniaturization and low power consumption, Memristor came into existence. Our design exploration is Reconfigurable Threshold Logic Gates based Programmable Analog Circuits using Memristor. Thus a variety of linearly separable and non- linearly separable logic functions such as AND, OR, NAND, NOR, XOR, XNOR have been realized using Threshold logic gate using Memristor. The functionality can be changed between these operations just by varying the resistance of the Memristor. Based on this Reconfigurable TLG, various Programmable Analog circuits can be built using Memristor. As an example of our approach, we have built Programmable analog Gain amplifier demonstrating Memristor-based programming of Threshold, Gain and Frequency. As our idea consisting of Programmable circuit design, in which low voltages are applied to Memristor during their operation as analog circuit element and high voltages are used to program the Memristor’s states. In these circuits the role of memristor is played by Memristor Emulator developed by us using FPGA. Reconfigurable is the option we are providing with the present system, so that the resistance ranges are varied by preprogram too. Index Terms— Memristor, TLG-threshold logic gates, Programmable Analog Circuits, FPGA-field programmable gate array, MTL- memristor threshold logic, CTL-capacitor Threshold logic, LUT- look up table. —————————— ( —————————— 1 INTRODUCTION CCORDING to Chua’s [founder of Memristor] definition, 9444163588. E-mail: [email protected] the internal state of an ideal Memristor depends on the • L.kavinmathi is currently pursuing bachelors degree program in electronics A and communication engineering in tagore engineering college under Anna integral of the voltage or current over time. -

Lab 1: the Bipolar Junction Transistor (BJT): DC Characterization

Lab 1: The Bipolar Junction Transistor (BJT): DC Characterization Electronics II Contents Introduction 2 Day 1: BJT DC Characterization 2 Background . 2 BJT Operation Regions . 2 (i) Saturation Region . 4 (ii) Active Region . 4 (iii) Cutoff Region . 5 Part 1: Diode-Like Behavior of BJT Junctions, and BJT Type 6 Experiment . 6 Creating Your Own File . 6 Report..................................................... 8 Part 2: BJT IC vs. VCE Characteristic Curves - Point by Point Plotting 8 Prelab . 8 Experiment . 8 Creating Your Own File . 8 Parameter Sweep . 9 Report..................................................... 10 Part 3: The Current Mirror 11 Experiment . 12 Simulation . 12 Checkout . 12 Report..................................................... 13 1 ELEC 3509 Electronics II Lab 1 Introduction When designing a circuit, it is important to know the properties of the devices that you will be using. This lab will look at obtaining important device parameters from a BJT. Although many of these can be obtained from the data sheet, data sheets may not always include the information we want. Even if they do, it is also useful to perform our own tests and compare the results. This process is called device characterization. In addition, the tests you will be performing will help you get some experience working with your tools so you don't waste time fumbling around with them in future labs. In Day 1, you will be looking at the DC characteristics of your transistor. This will give you an idea of what the I-V curves look like, and how you would measure them. You will also have to build and test a current mirror, which should give you an idea of how they work and where their limitations are. -

Junction Field Effect Transistor (JFET)

Junction Field Effect Transistor (JFET) The single channel junction field-effect transistor (JFET) is probably the simplest transistor available. As shown in the schematics below (Figure 6.13 in your text) for the n-channel JFET (left) and the p-channel JFET (right), these devices are simply an area of doped silicon with two diffusions of the opposite doping. Please be aware that the schematics presented are for illustrative purposes only and are simplified versions of the actual device. Note that the material that serves as the foundation of the device defines the channel type. Like the BJT, the JFET is a three terminal device. Although there are physically two gate diffusions, they are tied together and act as a single gate terminal. The other two contacts, the drain and source, are placed at either end of the channel region. The JFET is a symmetric device (the source and drain may be interchanged), however it is useful in circuit design to designate the terminals as shown in the circuit symbols above. The operation of the JFET is based on controlling the bias on the pn junction between gate and channel (note that a single pn junction is discussed since the two gate contacts are tied together in parallel – what happens at one gate-channel pn junction is happening on the other). If a voltage is applied between the drain and source, current will flow (the conventional direction for current flow is from the terminal designated to be the gate to that which is designated as the source). The device is therefore in a normally on state. -

EE-202 Electronics-I- Field-Effect Transistors JFET

EE-202 Electronics-I- Chapter 10 Field-Effect Transistors JFET 1 FET FET (Field-Effect Transistors) - BJTs (Bipolar Junction Transistors). Similarities: • Amplifiers • Switching devices • Impedance matching circuits Differences: • FETs are voltage controlled devices, BJTs are current controlled devices. • FETs have a higher input impedance, BJTs have higher gains. • FETs are less sensitive to temperature variations and they are more easily integrated on ICs. • FETs are generally more sensitive to static than BJTs. 2 FET Types •JFET–– Junction Field-Effect Transistor •MOSFET –– Metal-Oxide Field-Effect Transistor .D-MOSFET –– Depletion MOSFET .E-MOSFET –– Enhancement MOSFET 3 JFET Construction There are two types of JFETs •n-channel •p-channel The n-channel is more widely used. There are three terminals. •Drain (D) and source (S) are connected to the n-channel •Gate (G) is connected to the p-type material 4 JFET Operating Characteristics Three basic operating conditions for a JFET: • VGS = 0, VDS increasing to some positive value • VGS < 0, VDS at some positive value • Voltage-controlled resistor 5 JFET Operating Characteristics VGS = 0, VDS increasing to some positive value When VGS = 0 and VDS is increased from 0 to a more positive voltage; • The depletion region between p-gate and n-channel increases • Increasing the depletion region, decreases the size of the n-channel • Increasing in the n-channel resistance, the ID current increases. 6 JFET Operating Characteristics VGS = 0, VDS increasing to some positive value: Pinch Off VGS = 0 and VDS is increased to a more positive voltage, the depletion zone gets so large that it pinches off the n-channel. -

Chapter1: Semiconductor Diode

Chapter1: Semiconductor Diode. Electronics I Discussion Eng.Abdo Salah Theoretical Background: • The semiconductor diode is formed by doping P-type impurity in one side and N-type of impurity in another side of the semiconductor crystal forming a p-n junction as shown in the following figure. At the junction initially free charge carriers from both side recombine forming negatively c harged ions in P side of junction(an atom in P -side accept electron and be comes negatively c harged ion) and po sitive ly c harged ion on n side (an atom in n-side accepts hole i.e. donates electron and becomes positively charged ion)region. This region deplete of any type of free charge carrier is called as depletion region. Further recombination of free carrier on both side is prevented because of the depletion voltage generated due to charge carriers kept at distance by depletion (acts as a sort of insulation) layer as shown dotted in the above figure. Working principle: When voltage is not app lied acros s the diode , de pletion region for ms as shown in the above figure. When the voltage is applied be tween the two terminals of the diode (anode and cathode) two possibilities arises depending o n polarity of DC supply. [1] Forward-Bias Condition: When the +Ve terminal of the battery is connected to P-type material & -Ve terminal to N-type terminal as shown in the circuit diagram, the diode is said to be forward biased. The application of forward bias voltage will force electrons in N-type and holes in P -type material to recombine with the ions near boundary and to flow crossing junction. -

Graphene Field-Effect Transistor Array with Integrated Electrolytic Gates Scaled to 200 Mm

Graphene field-effect transistor array with integrated electrolytic gates scaled to 200 mm N C S Vieira1,3, J Borme1, G Machado Jr.1, F Cerqueira2, P P Freitas1, V Zucolotto3, N M R Peres2 and P Alpuim1,2 1INL - International Iberian Nanotechnology Laboratory, 4715-330, Braga, Portugal. 2CFUM - Center of Physics of the University of Minho, 4710-057, Braga, Portugal. 3IFSC - São Carlos Institute of Physics, University of São Paulo, 13560-970, São Carlos-SP, Brazil E-mail: [email protected] Abstract Ten years have passed since the beginning of graphene research. In this period we have witnessed breakthroughs both in fundamental and applied research. However, the development of graphene devices for mass production has not yet reached the same level of progress. The architecture of graphene field-effect transistors (FET) has not significantly changed, and the integration of devices at the wafer scale has generally not been sought. Currently, whenever an electrolyte-gated FET (EGFET) is used, an external, cumbersome, out-of-plane gate electrode is required. Here, an alternative architecture for graphene EGFET is presented. In this architecture, source, drain, and gate are in the same plane, eliminating the need for an external gate electrode and the use of an additional reservoir to confine the electrolyte inside the transistor active zone. This planar structure with an integrated gate allows for wafer-scale fabrication of high-performance graphene EGFETs, with carrier mobility up to 1800 cm2 V-1 s-1. As a proof-of principle, a chemical sensor was achieved. It is shown that the sensor can discriminate between saline solutions of different concentrations. -

Ltspice Tutorial Part 4- Intermediate Circuits

Sim Lab 8 P art 2 – E fficiency R evisited Prerequisites ● Please make sure you have completed the following: ○ LTspice tutorial part 1-4 Learn ing Objectives 1. Build circuits that control the motor speed with resistor network and with MOSFET usingLTSpice XVII. 2. By calculating the power efficiency of two speed control circuits, learn that the use of MOSFET in a speed control circuit can increase the power efficiency. Speed control by resist or network ● First, place the components as the following figure. For convenience, we use a resistor in series with an inductor to model the motor. Set the values of resistors, the inductor and the voltage source like the figure. Speed control by resist or network ● Next, connect the circuit as the following figure. We first connect the left three 100 Ω resistors to the circuit. Also, add a label net called “Vmotor_1” and place it right above R6. W e want to monitor the voltage across the motor in this way. ● At the same time, like what we did to a capacitor in previous labs, we also need to set initial conditions for an inductor. Click “Edit” -> Spice Directive -> set “.ic i(L1) = 0”. Speed control by resist or network ● Next, set the simulation condition as the left figure. We are ready to start the simulation. ● The reason to set the stop time as 0.1ms is to observe the change of Vmotor_1 through time from a transient state to steady state. Motor Model Speed control by resist or network ● Run the simulation. ● Plot Vmotor_1 and the current flowing through R6. -

Basic DC Motor Circuits

Basic DC Motor Circuits Living with the Lab Gerald Recktenwald Portland State University [email protected] DC Motor Learning Objectives • Explain the role of a snubber diode • Describe how PWM controls DC motor speed • Implement a transistor circuit and Arduino program for PWM control of the DC motor • Use a potentiometer as input to a program that controls fan speed LWTL: DC Motor 2 What is a snubber diode and why should I care? Simplest DC Motor Circuit Connect the motor to a DC power supply Switch open Switch closed +5V +5V I LWTL: DC Motor 4 Current continues after switch is opened Opening the switch does not immediately stop current in the motor windings. +5V – Inductive behavior of the I motor causes current to + continue to flow when the switch is opened suddenly. Charge builds up on what was the negative terminal of the motor. LWTL: DC Motor 5 Reverse current Charge build-up can cause damage +5V Reverse current surge – through the voltage supply I + Arc across the switch and discharge to ground LWTL: DC Motor 6 Motor Model Simple model of a DC motor: ❖ Windings have inductance and resistance ❖ Inductor stores electrical energy in the windings ❖ We need to provide a way to safely dissipate electrical energy when the switch is opened +5V +5V I LWTL: DC Motor 7 Flyback diode or snubber diode Adding a diode in parallel with the motor provides a path for dissipation of stored energy when the switch is opened +5V – The flyback diode allows charge to dissipate + without arcing across the switch, or without flowing back to ground through the +5V voltage supply. -

Field Effect Transistors

Module www.learnabout-electronics.org 4 Field Effect Transistors Module 4.1 Junction Field Effect Transistors What you´ll learn in Module 4 Field Effect Transistors Section 4.1 Field Effect Transistors. Although there are lots of confusing names for field • FETs JFETs, JUGFETs, and IGFETS effect transistors (FETs) there are basically two main • The JFET. types: • Diffusion JFET Construction. • Planar JFET Construction. 1. The reverse biased PN junction types, the JFET or • JFET Circuit Symbols. Junction FET, (also called the JUGFET or Junction Unipolar Gate FET). Section 4.2 How a JFET Works. • Operation Below Pinch Off. 2. The insulated gate FET devices (IGFET). • Operation Above Pinch Off. • JFET Output Characteristic. All FETs can be called UNIPOLAR devices because • JFET Transfer Characteristic. the charge carriers that carry the current through the • JFET Video. device are all of the same type i.e. either holes or electrons, but not both. This distinguishes FETs from Section 4.3 The Enhancement Mode MOSFET. the bipolar devices in which both holes and electrons • The IGFET (Insulated Gate FET). • MOSFET(IGFET) Construction. are responsible for current flow in any one device. • MOSFET(IGFET) Operation. The JFET • MOSFET (IGFET) Circuit Symbols. • Handling Precautions for MOSFETS This was the earliest FET device available. It is a voltage-controlled device in which current flows Section 4.4 The Depletion Mode MOSFET. from the SOURCE terminal (equivalent to the • Depletion Mode MOSFET Operation. emitter in a bipolar transistor) to the DRAIN • MOSFE (IGFET) Circuit Symbols. (equivalent to the collector). A voltage applied • Applications of MOSFETS • High Power MOSFETS between the source terminal and a GATE terminal (equivalent to the base) is used to control the source - Section 4.5 Power MOSFETs.