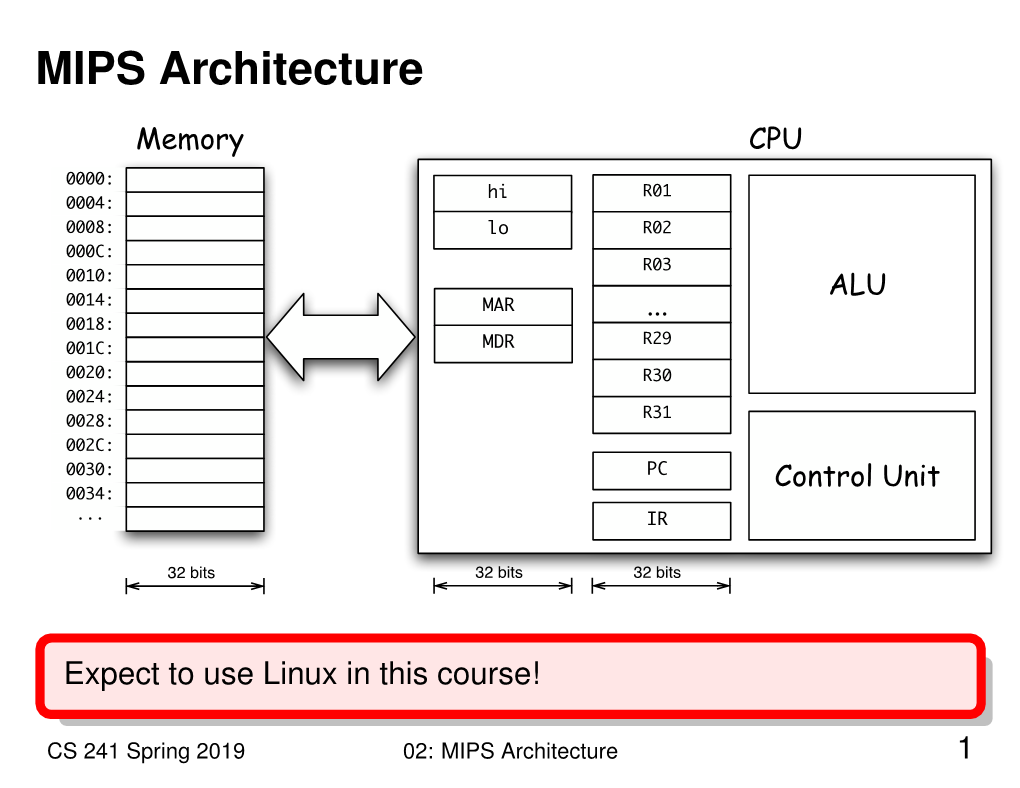

MIPS Architecture

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

MIPS Architecture

Introduction to the MIPS Architecture January 14–16, 2013 1 / 24 Unofficial textbook MIPS Assembly Language Programming by Robert Britton A beta version of this book (2003) is available free online 2 / 24 Exercise 1 clarification This is a question about converting between bases • bit – base-2 (states: 0 and 1) • flash cell – base-4 (states: 0–3) • hex digit – base-16 (states: 0–9, A–F) • Each hex digit represents 4 bits of information: 0xE ) 1110 • It takes two hex digits to represent one byte: 1010 0111 ) 0xA7 3 / 24 Outline Overview of the MIPS architecture What is a computer architecture? Fetch-decode-execute cycle Datapath and control unit Components of the MIPS architecture Memory Other components of the datapath Control unit 4 / 24 What is a computer architecture? One view: The machine language the CPU implements Instruction set architecture (ISA) • Built in data types (integers, floating point numbers) • Fixed set of instructions • Fixed set of on-processor variables (registers) • Interface for reading/writing memory • Mechanisms to do input/output 5 / 24 What is a computer architecture? Another view: How the ISA is implemented Microarchitecture 6 / 24 How a computer executes a program Fetch-decode-execute cycle (FDX) 1. fetch the next instruction from memory 2. decode the instruction 3. execute the instruction Decode determines: • operation to execute • arguments to use • where the result will be stored Execute: • performs the operation • determines next instruction to fetch (by default, next one) 7 / 24 Datapath and control unit -

MIPS IV Instruction Set

MIPS IV Instruction Set Revision 3.2 September, 1995 Charles Price MIPS Technologies, Inc. All Right Reserved RESTRICTED RIGHTS LEGEND Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and / or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor / manufacturer is MIPS Technologies, Inc., 2011 N. Shoreline Blvd., Mountain View, CA 94039-7311. R2000, R3000, R6000, R4000, R4400, R4200, R8000, R4300 and R10000 are trademarks of MIPS Technologies, Inc. MIPS and R3000 are registered trademarks of MIPS Technologies, Inc. The information in this document is preliminary and subject to change without notice. MIPS Technologies, Inc. (MTI) reserves the right to change any portion of the product described herein to improve function or design. MTI does not assume liability arising out of the application or use of any product or circuit described herein. Information on MIPS products is available electronically: (a) Through the World Wide Web. Point your WWW client to: http://www.mips.com (b) Through ftp from the internet site “sgigate.sgi.com”. Login as “ftp” or “anonymous” and then cd to the directory “pub/doc”. (c) Through an automated FAX service: Inside the USA toll free: (800) 446-6477 (800-IGO-MIPS) Outside the USA: (415) 688-4321 (call from a FAX machine) MIPS Technologies, Inc. -

Design and VHDL Implementation of an Application-Specific Instruction Set Processor

Design and VHDL Implementation of an Application-Specific Instruction Set Processor Lauri Isola School of Electrical Engineering Thesis submitted for examination for the degree of Master of Science in Technology. Espoo 19.12.2019 Supervisor Prof. Jussi Ryynänen Advisor D.Sc. (Tech.) Marko Kosunen Copyright © 2019 Lauri Isola Aalto University, P.O. BOX 11000, 00076 AALTO www.aalto.fi Abstract of the master’s thesis Author Lauri Isola Title Design and VHDL Implementation of an Application-Specific Instruction Set Processor Degree programme Computer, Communication and Information Sciences Major Signal, Speech and Language Processing Code of major ELEC3031 Supervisor Prof. Jussi Ryynänen Advisor D.Sc. (Tech.) Marko Kosunen Date 19.12.2019 Number of pages 66+45 Language English Abstract Open source processors are becoming more popular. They are a cost-effective option in hardware designs, because using the processor does not require an expensive license. However, a limited number of open source processors are still available. This is especially true for Application-Specific Instruction Set Processors (ASIPs). In this work, an ASIP processor was designed and implemented in VHDL hardware description language. The design was based on goals that make the processor easily customizable, and to have a low resource consumption in a System- on-Chip (SoC) design. Finally, the processor was implemented on an FPGA circuit, where it was tested with a specially designed VGA graphics controller. Necessary software tools, such as an assembler were also implemented for the processor. The assembler was used to write comprehensive test programs for testing and verifying the functionality of the processor. This work also examined some future upgrades of the designed processor. -

Overview of the MIPS Architecture: Part I

Overview of the MIPS Architecture: Part I CS 161: Lecture 0 1/24/17 Looking Behind the Curtain of Software • The OS sits between hardware and user-level software, providing: • Isolation (e.g., to give each process a separate memory region) • Fairness (e.g., via CPU scheduling) • Higher-level abstractions for low-level resources like IO devices • To really understand how software works, you have to understand how the hardware works! • Despite OS abstractions, low-level hardware behavior is often still visible to user-level applications • Ex: Disk thrashing Processors: From the View of a Terrible Programmer Letter “m” Drawing of bird ANSWERS Source code Compilation add t0, t1, t2 lw t3, 16(t0) slt t0, t1, 0x6eb21 Machine instructions A HARDWARE MAGIC OCCURS Processors: From the View of a Mediocre Programmer • Program instructions live Registers in RAM • PC register points to the memory address of the instruction to fetch and execute next • Arithmetic logic unit (ALU) performs operations on PC registers, writes new RAM values to registers or Instruction memory, generates ALU to execute outputs which determine whether to branches should be taken • Some instructions cause Devices devices to perform actions Processors: From the View of a Mediocre Programmer • Registers versus RAM Registers • Registers are orders of magnitude faster for ALU to access (0.3ns versus 120ns) • RAM is orders of magnitude larger (a PC few dozen 32-bit or RAM 64-bit registers versus Instruction GBs of RAM) ALU to execute Devices Instruction Set Architectures (ISAs) -

In More Depth: the IBM/Motorola Powerpc Indexed Addressing

In More Depth IMD 2.20-11 In More Depth: The IBM/Motorola PowerPC The PowerPC, made by IBM and Motorola and used in the Apple Macin- tosh, shares many similarities to MIPS: both have 32 integer registers, instructions are all 32 bits long, and data transfer is possible only with loads and stores. The primary difference is two more addressing modes plus a few operations. Indexed Addressing In the examples above we saw cases where we needed one register to hold the base of the array and the other to hold the index of the array. PowerPC provides an addressing mode, often called indexed addressing, that allows two registers to be added together. The MIPS code add $t0,$a0,$s3 # $a0 = base of array, $s3 = index lw $t1,0($t0) # reg $t1 gets Memory[$a0+$s3] could be replaced by the following single instruction in PowerPC: lw $t1,$a0+$s3 # reg $t1 gets Memory[$a0+$s3] Using the same notation as Figure 2.24 on page 101, Figure 2.1.1 shows indexed addressing. It is available with both loads and stores. Update Addressing Imagine the case of a code sequence marching through an array of words in memory, such as in the array version of clear1 on page 130. A frequent pair of operations would be loading a word and then incrementing the base reg- ister to point to the next word. The idea of update addressing is to have a new version of data transfer instructions that will automatically increment the base register to point to the next word each time data is transferred. -

Design of the RISC-V Instruction Set Architecture

Design of the RISC-V Instruction Set Architecture Andrew Waterman Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2016-1 http://www.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-1.html January 3, 2016 Copyright © 2016, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Design of the RISC-V Instruction Set Architecture by Andrew Shell Waterman A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate Division of the University of California, Berkeley Committee in charge: Professor David Patterson, Chair Professor Krste Asanovi´c Associate Professor Per-Olof Persson Spring 2016 Design of the RISC-V Instruction Set Architecture Copyright 2016 by Andrew Shell Waterman 1 Abstract Design of the RISC-V Instruction Set Architecture by Andrew Shell Waterman Doctor of Philosophy in Computer Science University of California, Berkeley Professor David Patterson, Chair The hardware-software interface, embodied in the instruction set architecture (ISA), is arguably the most important interface in a computer system. Yet, in contrast to nearly all other interfaces in a modern computer system, all commercially popular ISAs are proprietary. -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements. -

![MIPS Architecture with Tomasulo Algorithm [12]](https://docslib.b-cdn.net/cover/1642/mips-architecture-with-tomasulo-algorithm-12-1591642.webp)

MIPS Architecture with Tomasulo Algorithm [12]

CALIFORNIA STATE UNIVERSITY NORTHRIDGE TOMASULO ARCHITECTURE BASED MIPS PROCESSOR A graduate project submitted in partial fulfilment for the requirement Of the degree of Master of Science In Electrical Engineering By Sameer S Pandit May 2014 The graduate project of Sameer Pandit is approved by: ______________________________________ ____________ Dr. Ali Amini, Ph.D. Date _______________________________________ ____________ Dr. Shahnam Mirzaei, Ph.D. Date _______________________________________ ____________ Dr. Ramin Roosta, Ph.D., Chair Date California State University Northridge ii ACKNOWLEDGEMENT I would like to express my gratitude towards all the members of the project committee and would like to thank them for their continuous support and mentoring me for every step that I have taken towards the completion of this project. Dr. Roosta, for his guidance, Dr. Shahnam for his ideas, and Dr. Ali Amini for his utmost support. I would also like to thank my family and friends for their love, care and support through all the tough times during my graduation. iii Table of Contents SIGNATURE PAGE .......................................................................................................... ii ACKNOWLEDGEMENT ................................................................................................. iii LIST OF FIGURES .......................................................................................................... vii ABSTRACT ....................................................................................................................... -

MIPS Processors

MIPS Processors 2 About MIPS Based on a heritage built and continuously innovated over more than three decades, Imagination’s MIPS® architecture is the industry’s most efficient RISC architecture, delivering the best performance and lowest power consumption in a given silicon area. SoC designers can use this efficiency advantage for significant cost and power savings, or to implement additional cores to deliver a performance advantage in the same power, thermal and area budget. Imagination’s family of MIPS processor cores are ideal for products where ultra low-power, compact silicon area and a high level of integration are required. Our powerful, yet flexible CPU IP scales seamlessly from entry-level to high-end, and features advanced technologies such as hardware multi-threading, compatible 32-bit and 64-bit instruction set architectures (ISAs), and ISA consistency from entry-level to high-end. MIPS is one of only three CPU architectures officially supported by Google’s Android, making it ideal for Android-based devices, as well as a wide range of other OS including Linux, and a range of RTOS (real-time OS). With billions of MIPS-based products already shipped, and many universities and schools around the world teaching CPU architecture using MIPS as their preferred platform, MIPS is truly the ideal CPU for tomorrow’s SoCs, from the highest-performance mobile applications processors to the lowest power connected sensor processors. 1 MIPS Architecture The market-leading MIPS architecture was created in the early 1980s as a 32-bit RISC processor focused on providing the highest levels of performance together with new levels of silicon efficiency thanks to its clean, elegant design. -

Using As the Gnu Assembler

Using as The gnu Assembler Version 2.14.90.0.7 The Free Software Foundation Inc. thanks The Nice Computer Company of Australia for loaning Dean Elsner to write the first (Vax) version of as for Project gnu. The proprietors, management and staff of TNCCA thank FSF for distracting the boss while they got some work done. Dean Elsner, Jay Fenlason & friends Using as Edited by Cygnus Support Copyright c 1991, 92, 93, 94, 95, 96, 97, 98, 99, 2000, 2001, 2002 Free Software Foundation, Inc. Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation; with no Invariant Sections, with no Front-Cover Texts, and with no Back-Cover Texts. A copy of the license is included in the section entitled \GNU Free Documentation License". Chapter 1: Overview 1 1 Overview This manual is a user guide to the gnu assembler as. Here is a brief summary of how to invoke as. For details, see Chapter 2 [Command-Line Options], page 15. as [-a[cdhlns][=file]] [-D][{defsym sym=val] [-f][{gstabs][{gstabs+] [{gdwarf2][{help] [-I dir][-J][-K][-L] [{listing-lhs-width=NUM][{listing-lhs-width2=NUM] [{listing-rhs-width=NUM][{listing-cont-lines=NUM] [{keep-locals][-o objfile][-R][{statistics][-v] [-version][{version][-W][{warn][{fatal-warnings] [-w][-x][-Z][{target-help][target-options] [{|files ...] Target Alpha options: [-mcpu] [-mdebug | -no-mdebug] [-relax][-g][-Gsize] [-F][-32addr] Target ARC options: [-marc[5|6|7|8]] [-EB|-EL] Target ARM -

Migrating CPU Specific Code from the Powerpc to the Broadcom SB-1 Processor

WHITE PAPER Migrating CPU Specific Code from the PowerPC to the Broadcom SB-1 Processor 05/22/02 16215 Alton Parkway • P.O. Box 57013 • Irvine, California 92619-7013 • Phone: 949-450-8700 •Fax: 949-450-8710 REVISION HISTORY Revision # Date Change Description SB-1_WP100-R 05/22/02 Initial Release Broadcom Corporation 16215 Alton Parkway P.O. Box 57013 Irvine, California 92619-7013 © Copyright 2002 by Broadcom Corporation All rights reserved Printed in the U.S.A. Broadcom® and the pulse logo® are trademarks of Broadcom Corporation and/or its subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective owners. White Paper ■ SB-1 Processor 05/22/02 TABLE OF CONTENTS Introduction .................................................................................................................................................. 1 Programming Model .................................................................................................................................... 1 Processor Control........................................................................................................................................ 2 Memory Map Organization .......................................................................................................................... 2 The MIPS 32-bit Memory Map ................................................................................................................ 3 The Mips 64-bit Memory Map ................................................................................................................ -

Appendix C a Survey of RISC Architectures for Desktop, Server, and Embedded Computers

C.1 Introduction C-2 C.2 Addressing Modes and Instruction Formats C-4 C.3 Instructions: The MIPS Core Subset C-5 C.4 Instructions: Multimedia Extensions of the Desktop/Server RISCs C-16 C.5 Instructions: Digital Signal-Processing Extensions of the Embedded RISCs C-18 C.6 Instructions: Common Extensions to MIPS Core C-19 C.7 Instructions Unique to MIPS64 C-24 C.8 Instructions Unique to Alpha C-26 C.9 Instructions Unique to SPARC v.9 C-27 C.10 Instructions Unique to PowerPC C-31 C.11 Instructions Unique to PA-RISC 2.0 C-32 C.12 Instructions Unique to ARM C-35 C.13 Instructions Unique to Thumb C-36 C.14 Instructions Unique to SuperH C-37 C.15 Instructions Unique to M32R C-38 C.16 Instructions Unique to MIPS16 C-38 C.17 Concluding Remarks C-40 C.18 Acknowledgments C-41 References C-41 C A Survey of RISC Architectures for Desktop, Server, and Embedded Computers RISC: any computer announced after 1985. Steven Przybylski A Designer of the Stanford MIPS © 2003 Elsevier Science (USA). All rights reserved. C-2 I Appendix C A Survey of RISC Architectures for Desktop, Server, and Embedded Computers C.1 Introduction We cover two groups of reduced instruction set computer (RISC) architectures in this appendix. The first group is the desktop and server RISCs: I Digital Alpha I Hewlett-Packard PA-RISC I IBM and Motorola PowerPC I Silicon Graphics MIPS I Sun Microsystems SPARC The second group is the embedded RISCs: I Advanced RISC Machines ARM I Advanced RISC Machines Thumb I Hitachi SuperH I Mitsubishi M32R I Silicon Graphics MIPS16 There has never been another class of computers so similar.