Rail-To-Rail Output Op-Amp Design with Negative Miller Capacitance Compensation Muhaned Zaidi, Ian Grout, Abu Khari Bin A’Ain

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PH-218 Lec-12: Frequency Response of BJT Amplifiers

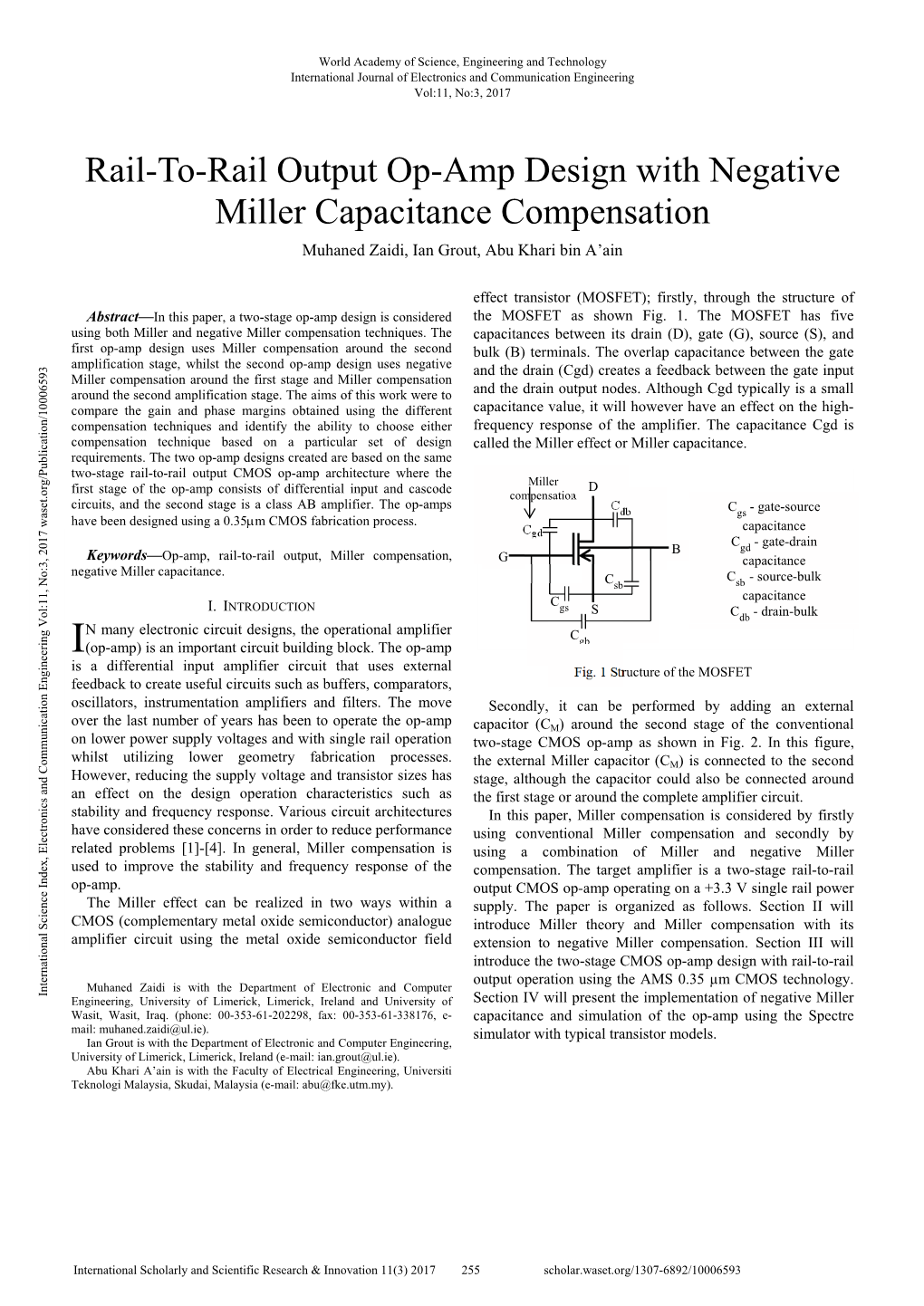

Analog & Digital Electronics Course No: PH-218 Lec-12: Frequency Response of BJT Amplifiers Course Instructors: Dr. A. P. VAJPEYI Department of Physics, Indian Institute of Technology Guwahati, India 1 High frequency Response of CE Amplifier At high frequencies, internal transistor junction capacitances do come into play, reducing an amplifier's gain and introducing phase shift as the signal frequency increases. In BJT, C be is the B-E junction capacitance, and C bc is the B-C junction capacitance. (output to input capacitance) At lower frequencies, the internal capacitances have a very high reactance because of their low capacitance value (usually only a few pf) and the low frequency value. Therefore, they look like opens and have no effect on the transistor's performance. As the frequency goes up, the internal capacitive reactance's go down, and at some point they begin to have a significant effect on the transistor's gain. High frequency Response of CE Amplifier When the reactance of C be becomes small enough, a significant amount of the signal voltage is lost due to a voltage-divider effect of the source resistance and the reactance of C be . When the reactance of Cbc becomes small enough, a significant amount of output signal voltage is fed back out of phase with the input (negative feedback), thus effectively reducing the voltage gain. 3 Millers Theorem The Miller effect occurs only in inverting amplifiers –it is the inverting gain that magnifies the feedback capacitance. vin − (−Av in ) iin = = vin 1( + A)× 2π × f ×CF X C Here C F represents C bc vin 1 1 Zin = = = iin 1( + A)× 2π × f ×CF 2π × f ×Cin 1( ) Cin = + A ×CF 4 High frequency Response of CE Amp.: Millers Theorem Miller's theorem is used to simplify the analysis of inverting amplifiers at high-frequencies where the internal transistor capacitances are important. -

High-Frequency Amplifier Response

Section H5: High-Frequency Amplifier Response Now that we’ve got a high frequency models for the BJT, we can analyze the high frequency response of our basic amplifier configurations. Note: in the circuits that follow, the actual signal source (vS) and its associated source resistance (RS) have been included. As discussed in the low frequency response section of our studies, we always knew that this source and resistance was there but we just started our investigations with the input to the transistor (vin). Remember - the analysis process is the same and the relationship between vS and vin is a voltage divider! Again, in some instances in the following discussion, I will be using slightly different notation and taking a different approach than your author. As usual, if this results in confusion, or you are more comfortable with his technique, let me know and we’ll work it out. High Frequency Response of the CE and ER Amplifier The generic common-emitter amplifier circuit of Section D2 is reproduced to the left below and the small signal circuit using the high frequency BJT model is given below right (based on Figures 10.17a and 10.17b of your text). Note that all external capacitors are assumed to be short circuits at high frequencies and are not present in the high frequency equivalent circuit (since the external capacitors are large when compared to the internal capacitances – recall that Zc=1/jωC gets small as the frequency or capacitance gets large). We can simplify the small signal circuit by making the following observations and approximations: ¾ Cce is very small and may be neglected. -

Miller Effect Cascode BJT Amplifier

ESE319 Introduction to Microelectronics Miller Effect Cascode BJT Amplifier 2008 Kenneth R. Laker,update 18Oct10 KRL 1 ESE319 Introduction to Microelectronics Prototype Common Emitter Circuit Ignore “low frequency” High frequency model capacitors 2008 Kenneth R. Laker,update 18Oct10 KRL 2 ESE319 Introduction to Microelectronics Multisim Simulation Mid-band gain ∣Av∣=g m RC=40mS ∗5.1k =20446.2 dB Half-gain point 2008 Kenneth R. Laker,update 18Oct10 KRL 3 ESE319 Introduction to Microelectronics Introducing the Miller Effect The feedback connection of C between base and collector causes it to appear to the amplifier like a large capacitor 1 − K C has been inserted between the base and emitter terminals. This phenomenon is called the “Miller effect” and the capacitive multiplier “1 – K ” acting on C equals the common emitter amplifier mid-band gain, i.e. K = − g m R C . NOTE: Common base and common collector amplifiers do not suffer from the Miller effect, since in these amplifiers, one side of C is connected directly to ground. 2008 Kenneth R. Laker,update 18Oct10 KRL 4 ESE319 Introduction to Microelectronics High Frequency CC and CB Models B C E ground B v-pi C B v-pi C E E C Common Collector Common Base C is in parallel with R . C is in parallel with R . B C 2008 Kenneth R. Laker,update 18Oct10 KRL 5 ESE319 Introduction to Microelectronics Miller's Theorem I Z −I I 1=I I 2=−I + + + + V 1 K V 1 V 2 V 1 Z Z V 2=K V 1 <=> 1 2 - - - - V 1 V 1 Z V 1−V 2 V 1−K V 1 V 1 Z I = = = => 1= = = Z Z Z I 1 I 1−K 1−K 1 Z 1= 1 j 2 f C 1−K V 2− V 2 V 2−V 2 K V 2 −I = = = V 2 V 2 Z Z Z Z Z = = = ≈ Z => 2 I −I 1 if K >> 1 1 2 1− 1− K K approx. -

Chapter 8 NOISE, GAIN and BANDWIDTH in ANALOG DESIGN

Chapter 8 NOISE, GAIN AND BANDWIDTH IN ANALOG DESIGN Robert G. Meyer Department of Electrical Engineering and Computer Sciences, University of California Trade-offs between noise, gain and bandwidth are important issues in analog circuit design. Noise performance is a primary concern when low-level sig- nals must be amplified. Optimization of noise performance is a complex task involving many parameters. The circuit designer must decide the basic form of amplification required – whether current input, voltage input or an impedance- matched input. Various parameters which can then be manipulated to optimize the noise performance include device sizes and bias currents, device types (FET or bipolar), circuit topologies (Darlington, cascode, etc.) and circuit impedance levels. The complexity of this situation is then further compounded when the issue of gain–bandwidth is included. A fundamental distinction to be made here is between noise issues in wideband amplifier design versus narrowband amplifier design. Wideband amplifiers generally have bandwidths of several octaves or more and may have to operate down to dc. This generally means that inductive elements cannot be used to enhance performance. By contrast, narrowband amplifiers may have bandwidths of as little as 10% or less of their center frequency, and inductors can be used to great advantage in trading gain for bandwidth and also in improving the circuit noise performance. In order to explore these issues and trade-offs, we begin first with a description of gain– bandwidth concepts as applied to both wideband and narrowband amplifiers, followed by a treatment of electronic circuit noise modeling. These concepts are then used in combination to define the trade-offs in circuit design between noise, gain and bandwidth. -

Theory of Vacuum Tubes Composed by J. B. Calvert

Vacuum Tubes This overgrown page covers all kinds of vacuum‐tube electron devices, especially receiving tubes. Many experiments are suggested, and much tube lore and curious circuits are presented. The Index may help you find what you want. Index i. History and Theory of Thermionic Tubes ii. Experiments iii. Diodes iv. The Noise Diode v. Phanotrons‐‐Gas Diodes vi. Triodes vii. The Cascode Circuit viii. Historic Triodes ix. A Pliotron x. High‐Frequency Triodes (acorn, etc) xi. Power Triodes xii. Screen‐Grid Tetrodes xiii. Space‐Charge‐Grid Tetrodes; Low‐Voltage Tubes xiv. Contact Potentials xv. Pentodes xvi. Power Pentodes and Beam Power Tubes xvii. Battery Tubes xviii. Sub‐Miniature Tubes xix. 117V Heater Tubes xx. Compactrons xxi. Grid Leak and Diode Detectors xxii. Oscillators and Mixers‐‐Conversion xxiii. Electron‐Ray Tubes xxiv. Voltage Regulator Tubes xxv. Thyratrons xxvi. Other Tubes xxvii. References and Links Composed by J. B. Calvert 1 Theory of Vacuum Tubes Miniature vacuum tubes with cathodes of high‐field‐emitting carbon nanotubes are currently under study at Agere Systems in Murray Hill, NJ. A triode with amplification factor of 4 has been constructed, with an anode‐cathode spacing of 220 μm, and a pentode is planned. Vacuum tubes may return to electronic technology! See Physics Today, July 2002, pp. 16‐18. Devices in which a stream of electrons is controlled by electric and magnetic fields have many applications in electronics. Because a vacuum must be provided in the form of an evacuated enclosure in which the electrons can move without collisions with gas molecules, these devices were called vacuum tubes or electron tubes in the US, and thermionic valves in Britain. -

Operational Amplifier Bandwidth Extension Using Negative Capacitance Generation

Brigham Young University BYU ScholarsArchive Theses and Dissertations 2006-07-06 Operational Amplifier Bandwidth Extension Using Negative Capacitance Generation Adrian P. Genz Brigham Young University - Provo Follow this and additional works at: https://scholarsarchive.byu.edu/etd Part of the Electrical and Computer Engineering Commons BYU ScholarsArchive Citation Genz, Adrian P., "Operational Amplifier Bandwidth Extension Using Negative Capacitance Generation" (2006). Theses and Dissertations. 459. https://scholarsarchive.byu.edu/etd/459 This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact [email protected], [email protected]. OPERATIONAL AMPLIFIER BANDWIDTH EXTENSION USING NEGATIVE CAPACITANCE GENERATION by Adrian P. C. Genz A thesis submitted to the faculty of Brigham Young University in partial fulfillment of the requirements for the degree of Master of Science Department of Electrical and Computer Engineering Brigham Young University August 2006 Copyright c 2006 Adrian P. C. Genz All Rights Reserved BRIGHAM YOUNG UNIVERSITY GRADUATE COMMITTEE APPROVAL of a thesis submitted by Adrian P. C. Genz This thesis has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory. Date David J. Comer, Chair Date Donald T. Comer Date Richard H. Selfridge BRIGHAM YOUNG UNIVERSITY As chair of the candidate’s graduate committee, I have read the thesis of Adrian P. C. Genz in its final form and have found that (1) its format, citations, and bibli- ographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library. -

Miller Effect - Wikipedia, the Free Encyclopedia Page 1 of 4

Miller effect - Wikipedia, the free encyclopedia Page 1 of 4 Miller effect From Wikipedia, the free encyclopedia In electronics, the Miller effect accounts for the increase in the equivalent input capacitance of an inverting voltage amplifier due to amplification of the effect of capacitance between the input and output terminals. The virtually increased input capacitance due to the Miller effect is given by where is the gain of the amplifier and C is the feedback capacitance. Although the term Miller effect normally refers to capacitance, any impedance connected between the input and another node exhibiting gain can modify the amplifier input impedance via this effect. These properties of the Miller effect are generalized in the Miller theorem. Contents ■ 1 History ■ 2 Derivation ■ 3 Effects ■ 3.1 Mitigation ■ 4 Impact on frequency response ■ 4.1 Miller approximation ■ 5 References and notes ■ 6 See also History The Miller effect was named after John Milton Miller.[1] When Miller published his work in 1920, he was working on vacuum tube triodes; however, the same theory applies to more modern devices such as bipolar and MOS transistors. Derivation Consider an ideal inverting voltage amplifier of gain with an impedance connected between its input and output nodes. The output voltage is therefore . Assuming that the amplifier input draws no current, all of the input current flows through , and is therefore given by . An ideal voltage inverting amplifier with an The input impedance of the circuit is impedance connecting output to input. http://en.wikipedia.org/wiki/Miller_effect 20. 11. 2013 Miller effect - Wikipedia, the free encyclopedia Page 2 of 4 If Z represents a capacitor with impedance , the resulting input impedance is [2] Thus the effective or Miller capacitance CM is the physical C multiplied by the factor . -

Lab 4: Frequency Response of CG and CD Amplifiers

State University of New York at Stony Brook ESE 314 Electronics Laboratory B Department of Electrical and Computer Engineering Fall 2010 © Leon Shterengas ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ Lab 4: Frequency Response of CG and CD Amplifiers. 1. OBJECTIVES Understand the role of input and output impedance in determining the gain of FET amplifiers: Measure the frequency response of CG amplifier; Measure the frequency response of CD amplifier. 2. INTRODUCTION 2.1. Frequency response of CG and CD amplifiers. In previous lab we have studied the gain of the CS amplifier paying special attention to the effect of load resistance and capacitance on amplifier bandwidth. By connecting capacitance to the load, we were essentially adding a low-pass filter at the output on CS amplifier. We have intentionally minimized the contribution of the parasitic low-pass-filter at the input to avoid the discussion of associated Miller effect. We did that by taking measured value of the gate-to-source signal voltage for an input voltage. Strictly speaking the gate material of the MOSFET has finite resistance and even in the experimental arrangement of lab 03 one cannot afford to unconditionally forget about low-pass-filter at the input. In this lab we will study that input low-pass-filter. We will also discuss the topologies of the FET amplifiers that can help to minimize the bandwidth limitations associated with the low-pass-filters either at the input or at the output. Figure 1a shows the generic CS amplifier with realistic signal source having finite output resistance. The equivalent circuit in Figure 1b can be used to predict high 3dB frequency fH. -

The Miller Effect and the Cascode Amplifier

BTT rev. new Bob’s TechTalk #52 Bob’s TechTalk Number 52: The MILLER EFFECT and the CASCODE AMPLIFIER by Bob Eckweiler - AF6C Introduction: The Miller Effect is an electronic principle where the capacitance at the input of a com- mon cathode triode amplifier increases with the gain of the amplifier. If the impedance dri- ving the amplifier is high, then the increased capacitance can reduce the bandwidth, espe- cially at high frequencies. There are ways to re- duce the Miller effect, one being the use of a cascode amplifier. In the Heathkit of the Month #91 article both the Miller Effect and the Cascode amplifier are mentioned. Here are explanations of what the Miller Effect is and what the Cascode Amplifier Figure 1: Typical small signal triode amplifier. can do to reduce its effect. ternal capacitance between the grid and plate, The Miller Effect: and the grid and cathode, respectively. Let’s The Miller Effect was documented by John Mil- assume the circuit has a gain of 50. GEN and ton Miller (1888 - 1968). while he was experi- Rs represent the signal source and source resis- menting with triode vacuum tubes. His distin- tance; this usually represents the previous guished career is well documented on Wiki- stage or the antenna (or other) input circuit. pedia. Miller published a paper in 1920 on the effect later named for him. While early on, the Figure 2 is an AC equivalent of Figure 1. CK Miller Effect was not a problem in most cir- and CIN, being large at the input frequency, are cuits, as frequencies increased the added ca- treated as shorts. -

Using Miller's Theorem and Dominant Poles to Accurately Determine Field

Paper ID #7756 Using Miller’s Theorem and Dominant Poles to Accurately Determine Field Effect Transistor and Bipolar Junction Transistor Small Signal and SPICE Capacitor Values Dr. Ernest M. Kim, University of San Diego Ernest M. Kim (M’77) received his B.S.E.E. from the University of Hawaii at Manoa in Honolulu, Hawaii in 1977, an M.S.E.E. in 1980 and Ph.D. in Electrical Engineering in 1987 from New Mexico State Univer- sity in Las Cruces, New Mexico. His dissertation was on precision near-field exit radiation measurements from optical fibers. He worked as an Electrical Engineer for the University of Hawaii at the Naval Ocean Systems Center, Hawaii Labs at Kaneohe Marine Corps Air Station after graduating with his B.S.E.E. Upon completing his M.S.E.E., he was an electrical engineer with the National Bureau of Standards in Boulder, Colorado designing hardware for precision fiber optic measurements. He then entered the commercial sector as a staff engineer with Burroughs Corporation in San Diego, California developing fiber optic LAN systems. He left Burroughs for Tacan/IPITEK Corporation as Manager of Electro-Optic Systems developing fiber optic CATV hardware and systems. In 1990 he joined the faculty of the University of San Diego. In 1996- 1997, he was at Ascom Tech in Bern, Switzerland as a Senior Systems Engineer performing research on Asynchronous Passive Optical Networks. He remains an active consultant in radio frequency and analog circuit design, and teaches review coursed for the engineering Fundamentals Examination. Dr. Thomas F. Schubert Jr. -

Miller Effect Cascode BJT Amplifier

ESE319 Introduction to Microelectronics Miller Effect Cascode BJT Amplifier 2008 Kenneth R. Laker (based on P. V. Lopresti 2006) update 15Oct08 KRL 1 ESE319 Introduction to Microelectronics Prototype Common Emitter Circuit Ignore “low frequency” High frequency model capacitors 2008 Kenneth R. Laker (based on P. V. Lopresti 2006) update 15Oct08 KRL 2 ESE319 Introduction to Microelectronics Multisim Simulation Mid-band gain ∣Av∣=g m RC=40mS∗5.1k=20446.2 dB Half-gain point 2008 Kenneth R. Laker (based on P. V. Lopresti 2006) update 15Oct08 KRL 3 ESE319 Introduction to Microelectronics Introducing the Miller Effect The feedback connection of C between base and collector causes it to appear to the amplifier like a large capacitor 1 − K C has been inserted between the base and emitter terminals. This phenomenon is called the “Miller effect” and the capacitive multiplier “1 – K ” acting on C equals the common emitter amplifier mid-band gain, i.e. K = − g m R C . Common base and common collector amplifiers do not suffer from the Miller effect, since in these amplifiers, one side of C is connected directly to ground. 2008 Kenneth R. Laker (based on P. V. Lopresti 2006) update 15Oct08 KRL 4 ESE319 Introduction to Microelectronics High Frequency CC and CB Models ground B C B C E E Common Collector Common Base C is in parallel with R . C is in parallel with R . B C 2008 Kenneth R. Laker (based on P. V. Lopresti 2006) update 15Oct08 KRL 5 ESE319 Introduction to Microelectronics Miller's Theorem I Z I 1=I I 2=I + + + + V1 V2=K V1 V V K V <=> 1 ic2 2= 1 - - - - V1−V2 V1−K V1 V1 V1 V1 Z I = = = => Z1= = = Z Z Z I 1 I 1−K 1−K V2 V2 Z Z Z = = =− = ≈Z => 2 −I −I 1 1 2 −1 1− K K if K >> 1 Let's examine Miller's Theorem as it applies to the HF model for the BJT CE amplifier. -

Common Source Stage Miller Approximation ZVTC Analysis Backgate Effect

Common Source Stage Miller Approximation ZVTC Analysis Backgate Effect Claudio Talarico Gonzaga University Sources: most of the figures were provided by B. Murmann CS with Resistive Load Vout VDD RD Bias Point (Q) vout Idi D = ID + id + VOUT v = V + v VoutOU=T OUT out Signal vin V in - Bias VIN vin Vin VIN + + gmvin 2I D 2I D vin ro RD vout Av = − RD || ro ≅ − RD - - VOV VOV gm often but not always !!! R EE 303 – Common Source Stage 2 Does ro matter ? § ro can be neglected in the gain calculation as long as the desired gain |Av| is much less than the intrinsic gain gmro 1 1 1 | AV |= gm (RD || ro ) = + | AV | gm RD gmro | A | g R = V ≅| A | m D | A | V 1− V gmro for | AV |<<gmro NOTE: IB The small signal 2ID 1 2 v VOoutUT gmro ≅ ⋅ = parameters (that is V V λI λV in vIN OV D OV gm and ro) are determined by the DC bias point Intrinsic Gain EE 303 – Common Source Stage 3 Upper Bound on Gain § In the basic common source stage RD performs two “conflicting” tasks – it translates the device’s drain current id into the output voltage vout. – it sets the drain bias voltage (VDS) of the MOSFET § This creates an upper bound on the achievable small signal voltage gain V 2ID RD | AV |≅ RD = 2 VOV VOV VRDmax VDD −VOV min VDD | AV max |=2 = 2 ≅ 2 VOUT VOV min VOV min VOV min VDD A NOTE: VIN – VT only a limited range B of the VTC is useful for amplification VDD ⋅ RON C For VIN large: VOUT ≅ (resistivedivider) RD + RON D VIN VT VDD cutoff saturation triode EE 303 – Common Source Stage 4 Voltage Gain and Drain Biasing Considerations (1) VIN ID VDS=VDD−RDID