AMD-K6 Series

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2004 Gamers' Hardware Upgrade Guide

Ace’s Hardware 2004 Gamers’ Hardware Upgrade Guide 2004 Gamers’ Hardware Upgrade Guide By Johan De Gelas – January 2004 Introduction Last week, we showed you a preview of the Athlon 64 3400+. Today, we'll investigate this new CPU as an upgrade to an existing system. How much performance do you gain when upgrading? What about the other features aside from performance, such as Cool'n'Quiet and more thermal and mechanical safety? As always, we start with a base system to be upgraded. This time around, our base system is equipped with an Athlon XP 2100+, as previous polls among our readers show that the faster versions of the Athlon XP "Palomino" were very popular in the early days of 2003. Now in 2004, Palomino is getting a little long in the tooth, so it's interesting to know whether or not an upgrade may be worthwhile. Our old system also contains a GeForce Ti 4200 and 512 MB of DDR266 (PC2100) memory. We will upgrade the CPU (to the Athlon 4 3400+) and memory (to DDR400 CAS 2) and compare that upgrade with one that simply upgrades the video card. As mentioned previously, we've done this before in many of our Gamer's Upgrade Guides. However, the gaming industry is not sitting still, and we are moving from hybrid DirectX 7/8 games to DirectX 8/9 games, which - as you will see - behave quite differently. The games you'll see tested in detail today are Halo 1.03, Return to Castle Wolfenstein: Enemy Territory, and X²- The Threat. -

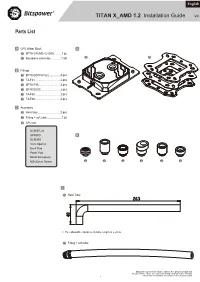

Titan X Amd 1.2 V4 Ig 20210319

English TITAN X_AMD 1.2 Installation Guide V4 Parts List A CPU Water Block A A-1 BPTA-CPUMS-V2-SKA ..........1 pc A-1 A-2 A-2 Backplane assembly ..............1 set B Fittings B-1 BPTA-DOTFH1622 ...............4 pcs B-2 TA-F61 ...................................2 pcs B-3 BPTA-F95 ..............................2 pcs B-4 BP-RIGOS5 ...........................2 pcs B-5 TA-F60 ..................................2 pcs B-6 TA-F40 ..................................2 pcs C Accessory C-1 Hard tube ..............................2 pcs C-2 Fitting + soft tube ....................1 pc C-3 CPU set SCM3FL20 SPRING B SCM3F6 1mm Spacer Back Pad Paste Pad Metal Backplane M3x32mm Screw B-1 B-2 B-3 B-4 B-5 B-6 C C-1 Hard Tube ※ The allowable variance in tube length is ± 2mm C-2 Fitting + soft tube Bitspower reserves the right to change the product design and interpretations. These are subject to change without notice. Product colors and accessories are based on the actual product. — 1 — I. AMD Motherboard system 54 AMD SOCKET 939 / 754 / 940 IN 48 AMD SOCKET AM4 AMD SOCKET AM3 / AM3+ AMD SOCKET AM2 / AM2+ AMD SOCKET FM1 / FM2+ Bitspower Fan and DRGB RF Remote Controller Hub (Not included) are now available at microcenter.com DRGB PIN on Motherboard or other equipment. 96 90 BPTA-RFCHUB The CPU water block has a DRGB cable, which AMD SOCKET AM4 AMD SOCKET AM3 AM3+ / AMD SOCKET AM2 AM2+ / AMD SOCKET FM1 / FM2+ can be connected to the DRGB extension cable of the radiator fans. Fan and DRGB RF Remote Motherboard Controller Hub (Not included) OUT DRGB LED Do not over-tighten the thumb screws Installation (SCM3FL20). -

Thermal Interface Material Comparison: Thermal Pads Vs

Thermal Interface Material Comparison: Thermal Pads vs. Thermal Grease Publication # 26951 Revision: 3.00 Issue Date: April 2004 © 2004 Advanced Micro Devices, Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice. Trademarks AMD, the AMD Arrow logo, AMD Athlon, AMD Duron, AMD Opteron and combinations thereof, are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. -

Super 7™ Motherboard

SY-5EH5/5EHM V1.0 Super 7Ô Motherboard ************************************************ Pentium® Class CPU supported ETEQ82C663 PCI/AGP Motherboard AT Form Factor ************************************************ User's Guide & Technical Reference NSTL “Year 2000 Test” Certification Letter September 23, 1998 Testing Date: September 23, 1998 Certification Date: September 23, 1998 Certification Number: NCY2000-980923-004 To Whom It May Concern: We are please to inform you that the “SY-5EHM/5EH5” system has passed NSTL Year 2000 certification test program. The Year 2000 test program tests a personal computer for its ability to support the year 2000. The “SY-5EHM/5EH5: system is eligible to carry the NSTL :Year 2000 Certification” seal. The Year 2000 certification test has been done under the following system configuration: Company Name : SOYO COMPUTER INC. System Model Name : SY-5EHM/5EH5 Hardware Revision : N/A CPU Model : Intel Pentium 200/66Mhz On Board Memory/L2 Cache : PC100 SDRAM DIMM 32MBx1 /1MB System BIOS : Award Modular BIOS V4.51PG, An Energy Star Ally Copyright © 1984—98, EH-1A6,07/15/1998-VP3-586B- 8669-2A5LES2AC-00 Best regards, SPORTON INTERNATIONAL INC. Declaration of Conformity According to 47 CFR, Part 2 and 15 of the FCC Rules Declaration No.: D872907 July.10 1998 The following designated product EQUIPMENT: Main Board MODEL NO.: SY-5EH Which is the Class B digital device complies with 47 CFR Parts 2 and 15 of the FCC rules. Operation is subject to the following two conditions : (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation. -

2021 User Guide

i Pro Fortran Linux Absoft Pro Fortran User Guide Absoft Fortran Linux Fortran User Guide 5119 Highland Road, PMB 398 Waterford, MI 48327 U.S.A. Tel (248) 220-1190 Fax (248) 220-1194 [email protected] All rights reserved. No part of this publication may be reproduced or used in any form by any means, without the prior written permission of Absoft Corporation. THE INFORMATION CONTAINED IN THIS PUBLICATION IS BELIEVED TO BE ACCURATE AND RELIABLE. HOWEVER, ABSOFT CORPORATION MAKES NO REPRESENTATION OF WARRANTIES WITH RESPECT TO THE PROGRAM MATERIAL DESCRIBED HEREIN AND SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. FURTHER, ABSOFT RESERVES THE RIGHT TO REVISE THE PROGRAM MATERIAL AND MAKE CHANGES THEREIN FROM TIME TO TIME WITHOUT OBLIGATION TO NOTIFY THE PURCHASER OF THE REVISION OR CHANGES. IN NO EVENT SHALL ABSOFT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE PURCHASER'S USE OF THE PROGRAM MATERIAL. U.S. GOVERNMENT RESTRICTED RIGHTS — The software and documentation are provided with RESTRICTED RIGHTS. Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at 252.227-7013. The contractor is Absoft Corporation, 2111 Cass Lake Rd. Ste 102, Keego Harbor, Michigan 48320. ABSOFT CORPORATION AND ITS LICENSOR(S) MAKE NO WARRANTIES, EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, REGARDING THE SOFTWARE. ABSOFT AND ITS LICENSOR(S) DO NOT WARRANT, GUARANTEE OR MAKE ANY REPRESENTATIONS REGARDING THE USE OR THE RESULTS OF THE USE OF THE SOFTWARE IN TERMS OF ITS CORRECTNESS, ACCURACY, RELIABILITY, CURRENTNESS, OR OTHERWISE. -

A Superscalar Out-Of-Order X86 Soft Processor for FPGA

A Superscalar Out-of-Order x86 Soft Processor for FPGA Henry Wong University of Toronto, Intel [email protected] June 5, 2019 Stanford University EE380 1 Hi! ● CPU architect, Intel Hillsboro ● Ph.D., University of Toronto ● Today: x86 OoO processor for FPGA (Ph.D. work) – Motivation – High-level design and results – Microarchitecture details and some circuits 2 FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT6-LUT 6-LUT6-LUT 3 6-LUT 6-LUT FPGA: Field-Programmable Gate Array ● Is a digital circuit (logic gates and wires) ● Is field-programmable (at power-on, not in the fab) ● Pre-fab everything you’ll ever need – 20x area, 20x delay cost – Circuit building blocks are somewhat bigger than logic gates 6-LUT 6-LUT 6-LUT 6-LUT 4 6-LUT 6-LUT FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 5 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel code and hardware accelerators need effort – Less effort if soft processors got faster 6 FPGA Soft Processors ● FPGA systems often have software components – Often running on a soft processor ● Need more performance? – Parallel -

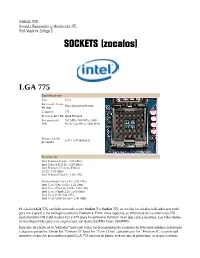

SOCKETS (Zocalos)

Instituto ITES Armado, Reparación y Mantención PC. Prof: Vladimir Zúñiga C. SOCKETS (zocalos) LGA 775 Especificaciones Tipo LGA Factores de forma Flip-chip land grid array del chip Contactos 775 Protocolo del FSB Quad-Pumped Frecuencia del 533 MT/s, 800 MT/s, 1066 FSB MT/s, 1333 MT/s, 1600 MT/s Dimesiones del 1.47 × 1.47 inches[1] procesador Procesadores Intel Pentium 4 (2.66 - 3.80 GHz) Intel Celeron D (2.53 - 3.60 GHz ) Intel Pentium 4 Extreme Edition (3.20 - 3.73 GHz) Intel Pentium D (2.66 - 3.60 GHz) Pentium Dual-Core (1.40 - 2.80 GHz) Intel Core 2 Duo (1.60 - 3.33 GHz) Intel Core 2 Extreme (2.66 - 3.20 GHz) Intel Core 2 Quad (2.33 - 3.00 GHz) Intel Xeon (1.86-3.40 GHz) Intel 'Core' Celeron (1.60 - 2.40 GHz) El zócalo LGA 775, también conocido como Socket T o Socket 775, es uno de los zócalos utilizados por Intel para dar soporte a los microprocesadores Pentium 4. Entre otros aspectos, se diferencia de los anteriores 370 (para Pentium III) y del Socket 423 y 478 (para los primeros Pentium 4) en que carece de pines. Las velocidades de bus disponibles para esta arquitectura van desde 533Mhz hasta 1600MHz. Este tipo de zócalo es el "estándar" para casi todos los procesadores de consumo de Intel para equipos sobremesa y algunos portátiles. Desde los "Celeron D" hasta los "Core 2 Duo", pasando por los "Pentium D", su principal atractivo es que los procesadores para LGA 775 carecen de pines; es decir que la placa base es la que contiene los contactos para comunicarse con el procesador. -

HDAMA Rev.G User's Guide

HDAMA rev.G HDAMA User’s Guide Release Date:Jul.2005 3.02 Version: Appendix BIOS Hardware Overview Setup Install Arima ServerBoard Manual COPYRIGHTS AND DISCLAIMERS ..........................................C-I ATTENTION: READ FIRST! ...................................... C-II Overview GENERAL SAFETY PRECAUTIONS .......................................C-2 ESD PRECAUTIONS ........................................................C-2 OPERATING PRECAUTIONS ................................................C-2 ABOUT THIS USER'S MANUAL ...........................................C-3 GETTING HELP ...............................................................C-3 SERVERBOARD SPECIFICATIONS ........................................C-5 SERVERBOARD LAYOUT ...................................................C-6 SERVERBOARD MAP .......................................................C-7 I/O PORT ARRAY ............................................................C-7 Hardware Installation MAP OF JUMPERS ...........................................................C-9 JUMPER SETTINGS ........................................................C-10 INSTALLING MEMORY .....................................................C-11 RECOMMENDED MEMORY CONFIGURATIONS .......................C-13 INSTALLING THE PROCESSOR AND HEATSINK ......................C-14 MAP OF SERVERBOARD CABLE CONNECTORS ...................C-16 ATX POWER CONNECTORS ............................................C-17 FLOPPY DISK DRIVE CONNECTOR ...................................C-18 PRIMARY IDE CONNECTORS ............................................C-18 -

User's Manual User's Manual

User’s Manual (English Edition) Intel Pentium 4 Socket 478 CPU AMD Athlon/ Duron/Athlon XP Socket 462 CPU AMD Athlon 64 Socket 754 CPU ZM-WB2 Gold * Please read before installation http://www.zalman.co.kr http://www.zalmanusa.com 1. Features 1) Gold plated pure copper base maximizes cooling performance and prevents CPU blocks from galvanic corrosion 2) Intel Pentium 4 (Socket 478), AMD Athlon/Duron/Athlon XP (Socket 462),Athlon 64 (Socket 754) compatible design for broad compatibility. 3) Three types of compression fitting are offered for use with water tubes (8X10mm,8X11mm,10X13mm) * Zalman Tech. Co., Ltd. is not responsible for any damage resulting from CPU OVERCLOCKING. 2. Specifications Part No Part name Q’ ty Weight (g) Use 1 CPU block 1 447.0 CPU mountimg 2 Hand screw 2 8.0 Clip mountimg 3 Thermal grease 1 1.8 Apply to cpu core 4 Clip 1 9.6 CPU block mountimg 5 User’s manual 1 6 Clip supports 2 8.2 Socket 478 7 Clip supports A 2 5.0 Socket 462 8 Clip supports B 2 5.0 Socket 462 9 Bolts 4 0.8 Clip supports, A, B-type 10 Paper washer 1 set 7, 8 mountimg 11 Nipple 2 6.2 Socket 754 mountimg 12 Back plate 60.0 Socket 754 mountimg Fitting to 13 Fitting 3 set 8 x 10mm, 8 x 11mm, 10 x 13mm tubes NOTE 1) The maximum weight for the cooler is specified as 450g/450g/300g for socket 478/754/462 respectively. Special care should be taken when moving a computer equipped with a cooler which exceeds the relevant weight limit. -

System Management BIOS (SMBIOS) Reference 6 Specification

1 2 Document Number: DSP0134 3 Date: 2011-01-26 4 Version: 2.7.1 5 System Management BIOS (SMBIOS) Reference 6 Specification 7 Document Type: Specification 8 Document Status: DMTF Standard 9 Document Language: en-US 10 System Management BIOS (SMBIOS) Reference Specification DSP0134 11 Copyright Notice 12 Copyright © 2000, 2002, 2004–2011 Distributed Management Task Force, Inc. (DMTF). All rights 13 reserved. 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 15 management and interoperability. Members and non-members may reproduce DMTF specifications and 16 documents, provided that correct attribution is given. As DMTF specifications may be revised from time to 17 time, the particular version and release date should always be noted. 18 Implementation of certain elements of this standard or proposed standard may be subject to third party 19 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations 20 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 21 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 22 inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to 23 any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, 24 disclose, or identify any such third party patent rights, or for such party’s reliance on the standard or 25 incorporation -

Thermal and Electrical Specification of AMD Semprontm Processors

Thermal and Electrical Specification of AMD SempronTM Processors Thermal and Electrical Specification of AMD SempronTM Processors 27 September 2004 Page 1/5 Thermal and Electrical Specification of AMD SempronTM Processors ©2004 Advanced Micro Devices Inc. All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. (“AMD”) products and are for information purposes only. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppels or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION. AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN OR FOR THE PERFORMANCE OR OPERATION OF ANY PERSON’S SYSTEM, INCLUDING, WITHOUT LIMITATION, ANY LOST PROFITS, BUSINESS INTERRUPTION, DAMAGE TO OR DESTRUCTION OF PROPERTY, OR LOSS OF PROGRAMS OR OTHER DATA, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. -

PCSA Oct 2001

Understanding CPU Upgrades In theory, one way to t seems that every time a new software product is released the system require- ments are increased - everything from the hard drive capacity and CPU speed increase the performance of a Ito the required RAM. One of the apparently obvious ways to gain a speed PC with little effort is to increase is by upgrading the CPU. But such an upgrade isn’t always cost effective and in some cases simply increasing the available RAM can help considerably to upgrade the CPU. Surely it boost the apparent speed of the PC. Sometimes though the best (and maybe only) option is to upgrade the CPU, although this can be a more involved process than it can’t be that difficult? might at first seem due to socket/motherboard incompatibilities, differing CPU and Actually there’s lots to think RAM speed requirements, cooling problems and inevitably assorted knock-on effects causing the upgrade to be anything but cost effective. Also, it is worth about. remembering that just because the replacement CPU has, for example, double the clock rate of the old unit doesn’t necessarily mean that the new one will increase the By Phil Morris processing performance of the PC in question by anything like 100%. Technical Writer This article looks at some of the options for upgrading the CPUs in existing systems. It is extremely unlikely that recent processors like AMD’s Duron (and forthcoming Hammer) and Intel’s Pentium 4 and Itanium will require upgrading for some time, so I will omit those in the context of this article.