SCAN90CP02 1.5 Gbps 2X2 LVDS Crosspoint Switch W/Pre-Emphasis

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Triad Rackamp 350 & 600 DSP V2.0 Instructions for IP Setup

Triad RackAmp 350 & 600 DSP v2.0 Instructions for IP Setup & Advanced Features This document describes IP (Internet Protocol) features unique to our RackAmp 350 & 600 DSP v2.0. Other connections, features and functions for these amps are very similar to our previous RackAmp 300/500/1000 DSP (v1.X). For more information see our RackAmp 350/600 DSP v2 Quick Start Guide and Triad SubAmp DSP v1.X Installer Setup Manual on the HOW TO or SUPPORT pages of our website http://www.triadspeakers.com/index.html . IP Features in RackAmp v2.0: IP for Setup – Use a computer or smart phone for remote setup when your subwoofer amps are located in different rooms than your subwoofers. IP for two Advanced Features 1. 6 Band Parametric EQ with 5 Hz resolution (-12dB to + 3dB; Q of .3 to 10). 2. Two Customizable Presets (default Volume & 1 band Parametric EQ). Note: IP allows Setup, Reset, or review by browser only; it is NOT for use with an external control system (Crestron, Control4, etc). IP Connections: • Via LAN: Connect RackAmp Ethernet Interface to a LAN with a standard Ethernet cable. If connecting to a wireless LAN, you can also use a Wi-Fi enabled smart phone, tablet, or laptop. The only issue when using a smart phone or tablet is that sliders do not work with the touch screen (the screen moves, not the slider). Instead, click on the number box above the slider and type the numbers in directly. • Direct to computer: Connect RackAmp’s Ethernet Interface direct to computer with an Ethernet crossover cable or a standard Ethernet cable with a crossover adaptor. -

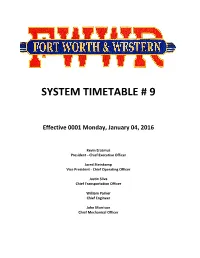

FWWR System Timetable and Special Instructions

SYSTEM TIMETABLE # 9 Effective 0001 Monday, January 04, 2016 Kevin Erasmus President - Chief Executive Officer Jared Steinkamp Vice President - Chief Operating Officer Justin Sliva Chief Transportation Officer William Parker Chief Engineer John Morrison Chief Mechanical Officer FORT WORTH & WESTERN RAILROAD DIRECTORY Corporate Office 6300 Ridglea Place, Suite 1200 Fort Worth, TX 76116 Phone: (817) 763-8297 Fax: (817) 738-9657 Customer Operations / Service Center Phone: (817) 731-1180 Toll Free: (800) 861-3657 Train Dispatcher Office Main Phone: (817) 738-2445 Emergency Only: (817) 821-6092 Fax: (817) 731-0602 Hodge Switching Yard (Main Yard) 2495 East Long Avenue Fort Worth, TX 76106 Phone: (817) 222-9798 Fax: (817) 222-1409 Dublin Switching Yard 407 E. Blackjack Dublin, Texas 76446 Phone: (254) 445-2177 Fax: (254) 445-4637 Cresson Switching Yard Phone / Fax: (817) 396-4841 8th Ave Switching Yard Phone / Fax: (817) 924-1441 Everman Switching Yard Phone / Fax: (817) 551-3706 Office Mobile President / CEO (817) 529-7140 (817) 223-1828 Vice President / COO (817) 222-9798 (817) 296-9933 Chief Transportation Officer (817) 222-9798 (817) 269-3582 Chief Engineer (817) 222-9798 (817) 201-4450 General Director of Track (817) 222-9798 (817) 821-2342 Chief Mechanical Officer (817) 222-9798 (817) 821-6094 Director of Transportation (817) 222-9798 (817) 235-3734 Gen Director Operating Practices (817) 222-9798 (817) 739-5567 Manager Train Operations (Fort Worth) (817) 222-9798 (817) 312-3429 Senior MTO (Dublin) (254) 445-2785 (817) 235-9713 Roadmaster -

Touchstone TM402 Telephony Modem User's Guide

Touchstone™ TM402 Telephony Modem User’s Guide Get ready to experience the Internet’s express lane! Whether you’re checking out streaming media, downloading new software, checking your email, or talking with friends on the phone, the Touchstone TM402 Telephony Modem brings it all to you faster and more reliably. All while providing toll quality Voice over IP telephone ser- vice. Some models even provide a Lithium-Ion battery backup to provide continued telephone service during power outages. The Touchstone Telephony Modem provides an Ethernet connection for use with ei- ther a single computer or home/office Local Area Network (LAN). The Touchstone Telephony Modem also provides a USB connection. You can connect two separate computers at the same time using both of these connections. In addition, the Touchstone Telephony Modem provides for up to two separate lines of telephone service. Installation is simple and your cable company will provide assistance to you for any special requirements. The links below will provide more detailed instructions. Safety Requirements Getting Started Battery Installation and Replacement (TM402G, TM402H, and TM402P models only) Installing and Connecting Your Telephony Modem Installing the Telephony Modem USB Drivers Configuring Your Ethernet Connection Using the Telephony Modem Troubleshooting Glossary Touchstone TM402 Telephony Modem User’s Guide 1 Export Regulations This product may not be exported outside the U.S. and Canada without U.S. Department of Commerce, Bureau of Export Administration au- thorization. Any export or re-export by the purchaser, directly or indirectly, in contravention of U.S. Export Administration Regulation is prohib- ited. Copyright © 2005 ARRIS International, Inc. -

The People Who Invented the Internet Source: Wikipedia's History of the Internet

The People Who Invented the Internet Source: Wikipedia's History of the Internet PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 22 Sep 2012 02:49:54 UTC Contents Articles History of the Internet 1 Barry Appelman 26 Paul Baran 28 Vint Cerf 33 Danny Cohen (engineer) 41 David D. Clark 44 Steve Crocker 45 Donald Davies 47 Douglas Engelbart 49 Charles M. Herzfeld 56 Internet Engineering Task Force 58 Bob Kahn 61 Peter T. Kirstein 65 Leonard Kleinrock 66 John Klensin 70 J. C. R. Licklider 71 Jon Postel 77 Louis Pouzin 80 Lawrence Roberts (scientist) 81 John Romkey 84 Ivan Sutherland 85 Robert Taylor (computer scientist) 89 Ray Tomlinson 92 Oleg Vishnepolsky 94 Phil Zimmermann 96 References Article Sources and Contributors 99 Image Sources, Licenses and Contributors 102 Article Licenses License 103 History of the Internet 1 History of the Internet The history of the Internet began with the development of electronic computers in the 1950s. This began with point-to-point communication between mainframe computers and terminals, expanded to point-to-point connections between computers and then early research into packet switching. Packet switched networks such as ARPANET, Mark I at NPL in the UK, CYCLADES, Merit Network, Tymnet, and Telenet, were developed in the late 1960s and early 1970s using a variety of protocols. The ARPANET in particular led to the development of protocols for internetworking, where multiple separate networks could be joined together into a network of networks. In 1982 the Internet Protocol Suite (TCP/IP) was standardized and the concept of a world-wide network of fully interconnected TCP/IP networks called the Internet was introduced. -

Connection Routing Schemes for Wireless ATM

Proceedings of the 32nd Hawaii International Conference on System Sciences - 1999 Proceedings of the 32nd Hawaii International Conference on System Sciences - 1999 Connection Routing Schemes for Wireless ATM Upkar Varshney Computer Information Systems Department Georgia State University Atlanta, Georgia 30302-4015 E-mail: [email protected] Abstract of the mobile location, how to provide quality of service, Wireless ATM, presents several interesting challenges and the how to deal with wireless links to support the such as managing an end-to-end ATM connection (using mobile computing environment. More details on wireless connection re-routing) and location management, ATM can be found in [3-5]. We discuss several rerouting handling high error rate performance of wireless links, schemes for wireless ATM networks and many issues maintaining the ATM cell sequence, and supporting including multi-connection and multicast connection quality of service (QoS) requirement. Recently, the design handoffs and propose generic techniques that can be of re-routing schemes has received some consideration in incorporated in rerouting schemes to support such the literature. However, most of these schemes do not handoffs. address support for multi-connection and multicast handoffs that may be necessary for mobile multimedia computing. We discuss several rerouting schemes for Satellite wireless ATM networks and many issues including multi- connection and multicast connection handoffs and Microwave Link propose generic techniques that can be incorporated in rerouting schemes to support such handoffs. We also ATM Network discuss how these can be incorporated in rerouting Dynamic Topology schemes such as RAC (Rearrange ATM Connection) and Network EAC (Extend ATM Connection). Fixed Topology Network 1. -

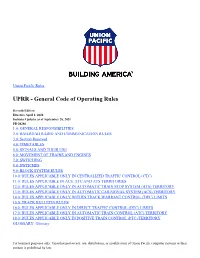

UPRR - General Code of Operating Rules

Union Pacific Rules UPRR - General Code of Operating Rules Seventh Edition Effective April 1, 2020 Includes Updates as of September 28, 2021 PB-20280 1.0: GENERAL RESPONSIBILITIES 2.0: RAILROAD RADIO AND COMMUNICATION RULES 3.0: Section Reserved 4.0: TIMETABLES 5.0: SIGNALS AND THEIR USE 6.0: MOVEMENT OF TRAINS AND ENGINES 7.0: SWITCHING 8.0: SWITCHES 9.0: BLOCK SYSTEM RULES 10.0: RULES APPLICABLE ONLY IN CENTRALIZED TRAFFIC CONTROL (CTC) 11.0: RULES APPLICABLE IN ACS, ATC AND ATS TERRITORIES 12.0: RULES APPLICABLE ONLY IN AUTOMATIC TRAIN STOP SYSTEM (ATS) TERRITORY 13.0: RULES APPLICABLE ONLY IN AUTOMATIC CAB SIGNAL SYSTEM (ACS) TERRITORY 14.0: RULES APPLICABLE ONLY WITHIN TRACK WARRANT CONTROL (TWC) LIMITS 15.0: TRACK BULLETIN RULES 16.0: RULES APPLICABLE ONLY IN DIRECT TRAFFIC CONTROL (DTC) LIMITS 17.0: RULES APPLICABLE ONLY IN AUTOMATIC TRAIN CONTROL (ATC) TERRITORY 18.0: RULES APPLICABLE ONLY IN POSITIVE TRAIN CONTROL (PTC) TERRITORY GLOSSARY: Glossary For business purposes only. Unauthorized access, use, distribution, or modification of Union Pacific computer systems or their content is prohibited by law. Union Pacific Rules UPRR - General Code of Operating Rules 1.0: GENERAL RESPONSIBILITIES 1.1: Safety 1.1.1: Maintaining a Safe Course 1.1.2: Alert and Attentive 1.1.3: Accidents, Injuries, and Defects 1.1.4: Condition of Equipment and Tools 1.2: Personal Injuries and Accidents 1.2.1: Care for Injured 1.2.2: Witnesses 1.2.3: Equipment Inspection 1.2.4: Mechanical Inspection 1.2.5: Reporting 1.2.6: Statements 1.2.7: Furnishing Information -

QOS-Aware Middleware for Mobile Multimedia Communications

Multimedia Tools and Applications 7, 67–82 (1998) c 1998 Kluwer Academic Publishers. Manufactured in The Netherlands. QOS-aware Middleware for Mobile Multimedia Communications ANDREW T. CAMPBELL [email protected] The COMET Group, Center for Telecommunications Research, Columbia University, Room 801 Schapiro Research Building, 530 W, 120th St., New York, NY 10027-6699 http://comet.columbia.edu/campbell, http://comet.columbia.edu/wireless Abstract. Next generation wireless communications system will be required to support the seamless delivery of voice, video and data with high quality. Delivering hard Quality of Service (QOS) assurances in the wireless domain is complex due to large-scale mobility requirements, limited radio resources and fluctuating network conditions. To address this challenge we are developing mobiware, a QOS-aware middleware platform that contains the complexity of supporting multimedia applications operating over wireless and mobile networks. Mobiware is a highly programmable software platform based on the latest distributed systems technology (viz. CORBA and Java). It is designed to operate between the application and radio-link layers of next generation wireless and mobile systems. Mobiware provides value-added QOS support by allowing mobile multimedia applications to operate transparently during handoff and periods of persistent QOS fluctuation. Keywords: middleware, mobile communications, adaptive algorithms, active transport, QOS 1. Introduction Recent years have witnessed a tremendous growth in the use of wireless communications in business, consumer and military applications. The number of wireless services and sub- scribers has expanded with systems for mobile analog and digital cellular telephony, radio paging, and cordless telephony becoming widespread. Next generation wireless networks such as wireless ATM (WATM ) will provide enhanced communication services such as high resolution digital video and full multimedia communications. -

Providing Seamless Communications in Mobile Wireless Networks

Providing Seamless Communications in Mobile Wireless Networks Bikram S Bakshi P Krishna N H Vaidya D K Pradhan Department of Computer Science Texas AM University College Station TX Email fbbakshipkrishnavaidyapradhangcstamuedu Phone April Technical Rep ort Abstract This paper presents a technique to provide seamless communications in mobile wireless networks The goal of seamless communication is to provide disruption free service to a mobile user A disruption in service could occur due to active handos handos during an active connection Existing protocols either provide total guarantee for disruption free service incurring heavy network bandwidth usage multicast based approach or do not provide any guarantee for disruption free service forwarding approach There are many user applications that do not require a total guarantee for disruption free service but would also not tolerate very frequent disruptions This paper proposes a novel staggered multicast approach which provides a probabilistic guarantee for disruption free service The main advantage of the staggered multicast approach is that it exploits the performance guarantees provided by the multicast approach and also provides the much required savings in the static network bandwidth The problem of guaranteeing disruption free service to mobile users becomes more acute when the static backbone network does not use any packet numbering or does not provide retrans missions Asynchronous Transfer Mode networks the future of BISDN display these properties To make our study complete -

Pathway Model 7364

SPECIFICATIONS MODEL 7364 Cat. No. 307364 ® Model 7364 Dual Channel Switch, DB9 A/B, DB9 Crossover, with RS232, Telnet and GUI INTRODUCTION Channel 1 of the Model 7364 Switch allows the user the capability of sharing a single port interface device connected to the “COMMON” port among two other devices connected to the “A” and “B” ports. Channel 2 of the Model 7364 allows the user the capability of attaching four devices connected to the “A”, “B”, “C”, and “D” ports in either a “Normal” or “Crossover” configuration. NORMAL position is defined as port A connected to port C and port B connected to port D. CROSSOVER position is defined as port A connected to port D and port B connected to port C. Remote Control access can be accomplished using an Ethernet 10/100BASE-T connection and either Telnet commands or graphical user interface. The unit can also be controlled via RS232 ASCII commands through the rear panel DB9 Remote Port. FEATURES SPECIFICATIONS: • Unit allows independent switch control of two channels. PORT CONNECTORS: (3) DB9 female connectors Channel one is a DB9 A/B Switch. Channel two is a DB9 labeled A, B, and COM for Channel 1. (4) DB9 female Crossover Switch. connectors labeled A, B, C, D for Channel 2. • Independently control each channel remotely via either the DB9 Serial REMOTE port, or the 10/100 RJ45 Ethernet CONTROLS: (2) Pushbuttons allow local switching. REMOTE port. DISPLAY: (4) Front panel LED’s display switch position. • Serial REMOTE port supports ASCII command set that allows TWO REMOTE CONTROL PORTS: (1) DB9 female position control, query of switch position, and front panel connector on rear panel accepts ASCII RS232 Serial pushbutton lock/unlock. -

Globus Project Future Directions

The Internet: Packet Switching and Other Big Ideas Ian Foster 2 The Internet 1969 2004 4 nodes 100s of millions 3 The Internet z Clearly a huge success in terms of not only impact but also scalability Some (not all) of the basic notions have scaled over eight orders of magnitude z What were underlying big ideas? Let’s say: Packet switching End-to-end principle Internet community & “standards” process z Also other important algorithms, e.g. Routing, naming, multicast z Common thread: (fairly) robust emergent behaviors from simple local strategies 4 Overview z Birth of the Internet Packet switching Process and governance z End-to-end principle E.g., congestion avoidance and control z Decentralized, adaptive algorithms Routing Naming Multicast 5 Simple Switching Network 6 Problem Statement z Many “stations” connected by point-to-point “connections” (with some redundancy) z Enable any station to send “messages” to any other station, despite diverse failure modes z And further Be efficient in use of network resources Support stations of diverse capabilities Support diverse applications & behaviors, including many not yet known (!) 7 “Traditional” Approach: Circuit Switching z A dedicated communication path between the two stations z Communication involves: Circuit Establishment z Point to Point from terminal node to network z Internal Switching and multiplexing among switching nodes. Data Transfer Circuit Disconnect z E.g., the telephone network 8 Circuit Switching z Once connection is established: Network is transparent -

BEFSRU31 User Guide.Qxd

Instant Broadband™ Series EtherFast® Cable/DSL Routers Use this User Guide to install the following Linksys product(s): BEFSRU31 EtherFast Cable/DSL Router with USB Port and 10/100 3-Port Switch BEFSR41 v2 EtherFast Cable/DSL Router with 10/100 4-Port Switch BEFSR11 EtherFast 1-Port Cable/DSL Router User Guide COPYRIGHT & TRADEMARKS Copyright © 2000 Linksys, All Rights Reserved. Instant Broadband is a registered trademark of Linksys. Microsoft, Windows, and the Windows logo are registered trade- marks of Microsoft Corporation. All other trademarks and brand names are the proper- ty of their respective proprietors. LIMITED WARRANTY Linksys guarantees that every Instant Broadband EtherFast Cable/DSL Router is free from physical defects in material and workmanship under normal use for one (1) year from the date of purchase. If the product proves defective during this warranty period, call Linksys Customer Support in order to obtain a Return Authorization number. BE SURE TO HAVE YOUR PROOF OF PURCHASE ON HAND WHEN CALLING. When returning a product, mark the Return Authorization number clearly on the outside of the package and include your original proof of purchase. RETURN REQUESTS CANNOT BE PROCESSED WITHOUT PROOF OF PURCHASE. All customers located outside of the United States of America and Canada shall be held responsible for shipping and handling charges. IN NO EVENT SHALL LINKSYS’ LIABILITY EXCEED THE PRICE PAID FOR THE PROD- UCT FROM DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAM- AGES RESULTING FROM THE USE OF THE PRODUCT, ITS ACCOMPANYING SOFT- WARE, OR ITS DOCUMENTATION. LINKSYS OFFERS NO REFUNDS FOR ITS PROD- UCTS. -

Who Invented the Internet? 1958-1961: Connect Computers?

How did the Internet come to be? ❒ It started as a research project to experiment with connecting computers together with packet switched 2: Internet History networks. It was developed with funding and leadership of the Defense Last Modified: Department’s Advanced Research Projects Agency (ARPA). 1/20/2003 12:46:58 PM -1 -2 Who invented the Internet? 1958-1961: Connect Computers? ❒ Al Gore? No ☺ ❒ 1958 – After USSR launches Sputnik, first artificial earth satellite, US forms the Advanced ❒ Leonard Kleinrock who did early work in Research Projects Agency (ARPA), the following packet switching? year, within the Department of Defense (DoD) to ❒ Vint Cerf and Robert Kahn who defined the establish US lead in science and technology "Internet Protocol" (IP) and participated in applicable to the military the development of TCP? ❒ 1961 – First published work on packet switching ❒ (“Information Flow in Large Communication Nets”, Tim Berners-Lee developed HTTP to Leonard Kleinrock, MIT graduate student) support a global hyper-text system he ❒ 1964 – other independent work in packet switching called the World Wide Web? (Internet vs at RAND Institute and National Physics the World Wide Web?) Laboratory in England -3 -4 1966 –1968: Connect 1969: First Connections Computers? Funded ❒ 1966 – Lawrence Roberts (colleague of ❒ 4/7/1969 – First RFC (“Host Software” by Kleinrock from MIT) publishes overall plan Steve Crocker) basis for the Network for an ARPAnet, a proposed packet switch Control Protocol(NCP) network ❒ 9/2/1969 – Leonard Kleinrock’s computer