Microprocessor Design/Print Version 1 Microprocessor Design/Print Version

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Hardware Realization of an FPGA Processor – Operating System Call Offload and Experiences

Downloaded from orbit.dtu.dk on: Oct 02, 2021 Hardware Realization of an FPGA Processor – Operating System Call Offload and Experiences Hindborg, Andreas Erik; Schleuniger, Pascal; Jensen, Nicklas Bo; Karlsson, Sven Published in: Proceedings of the 2014 Conference on Design and Architectures for Signal and Image Processing (DASIP) Publication date: 2014 Link back to DTU Orbit Citation (APA): Hindborg, A. E., Schleuniger, P., Jensen, N. B., & Karlsson, S. (2014). Hardware Realization of an FPGA Processor – Operating System Call Offload and Experiences. In A. Morawiec, & J. Hinderscheit (Eds.), Proceedings of the 2014 Conference on Design and Architectures for Signal and Image Processing (DASIP) IEEE. General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. Users may download and print one copy of any publication from the public portal for the purpose of private study or research. You may not further distribute the material or use it for any profit-making activity or commercial gain You may freely distribute the URL identifying the publication in the public portal If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim. Hardware Realization of an FPGA Processor – Operating System Call Offload and Experiences Andreas Erik Hindborg, Pascal Schleuniger Nicklas Bo Jensen, Sven Karlsson DTU Compute – Technical University of Denmark fahin,pass,nboa,[email protected] Abstract—Field-programmable gate arrays, FPGAs, are at- speedup of up to 64% over a Xilinx MicroBlaze based baseline tractive implementation platforms for low-volume signal and system. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

Technical Competencies and Professional Skills

TECHNICAL COMPETENCIES AND PROFESSIONAL SKILLS Applied Mathematics Technical Skills: data visualization and analysis, SQL, finance and accounting Programming Languages: R, MATLAB, C++, Java, Python Markup Languages: LaTeX, HTML, CSS Software: Microsoft Office (Excel, Office, Word), XCode, Visual Studio Note: Skills, software, and languages are dependent on elective taken, computer selection, and class year. Applied Sciences Instrumentation: UV/Vis spectroscopy, NMR spectroscopy, IR spectroscopy, GC-MS, LC-MS, thermocycler, nucleic acid sequencer, microplate reader, cryocooler Lab Techniques: Gel electrophoresis and SDS-PAGE, Western blotting, primer design and Polymerase Chain Reaction (PCR), QPCR, sterile lab technique, cell culture, nucleic acid isolation and purification, protein isolation and purification (chromatography, centrifugation, dialysis), enzyme thermodynamics and kinetics, transfection and transformation, chemical synthesis and purification (distillation, extraction, chromatography, rotary evaporator, crystallization), inert atmosphere and Schlenk line techniques, titration, dissection of preserved specimens, four-probe electrical measurement, Bragg diffraction Competencies: Application of the scientific method, Scientific writing and oral communication Software and computational skills: Microsoft Office (Word, Excel, Powerpoint), ChemDraw, PyMol, TopSpin, Java, Protein DataBank (PDB), NCBI suite (including BLAST, GenBank), Orca Quantum Chemistry software, LoggerPro, LabView Architecture Design Skills: Multi-scale civic -

Please Replace the Following Pages in the Book. 26 Microcontroller Theory and Applications with the PIC18F

Please replace the following pages in the book. 26 Microcontroller Theory and Applications with the PIC18F Before Push After Push Stack Stack 16-bit Register 0120 143E 20C2 16-bit Register 0120 SP 20CA SP 20C8 143E 20C2 0703 20C4 0703 20C4 F601 20C6 F601 20C6 0706 20C8 0706 20C8 0120 20CA 20CA 20CC 20CC 20CE 20CE Bottom of Stack FIGURE 2.12 PUSH operation when accessing a stack from the bottom Before POP After POP Stack 16-bit Register A286 16-bit Register 0360 Stack 143E 20C2 SP 20C8 SP 20CA 143E 20C2 0705 20C4 0705 20C4 F208 20C6 F208 20C6 0107 20C8 0107 20C8 A286 20CA A286 20CA 20CC 20CC Bottom of Stack FIGURE 2.13 POP operation when accessing a stack from the bottom Note that the stack is a LIFO (last in, first out) memory. As mentioned earlier, a stack is typically used during subroutine CALLs. The CPU automatically PUSHes the return address onto a stack after executing a subroutine CALL instruction in the main program. After executing a RETURN from a subroutine instruction (placed by the programmer as the last instruction of the subroutine), the CPU automatically POPs the return address from the stack (previously PUSHed) and then returns control to the main program. Note that the PIC18F accesses the stack from the top. This means that the stack pointer in the PIC18F holds the address of the bottom of the stack. Hence, in the PIC18F, the stack pointer is incremented after a PUSH, and decremented after a POP. 2.3.2 Control Unit The main purpose of the control unit is to read and decode instructions from the program memory. -

NESS Esk a 2005.0034090 a 22005 Sato Et

US007 185309B1 (12) United States Patent (10) Patent No.: US 7,185,309 B1 Kulkarni et al. (45) Date of Patent: Feb. 27, 2007 (54) METHOD AND APPARATUS FOR 2004/0006584 A1 1/2004 Vandeweerd APPLICATION-SPECIFIC PROGRAMMABLE 2004/O128120 A1 7/2004 Coburn et al. NESS Esk A 2005.00340902005/0114593 A1A 220055/2005 SatoCassell et al.et al. (75) Inventors: Chidamber R. Kulkarni, San Jose, CA 2005/0172085 A1 8/2005 Klingman (US); Gordon J. Brebner, Monte 2005/0172087 A1 8/2005 Klingman Sereno, CA (US); Eric R. Keller, 2005/0172088 A1 8/2005 Klingman Boulder, CO (US); Philip B. 2005/0172089 A1 8/2005 Klingman James-Roxby, Longmont, CO (US) 2005/0172090 A1 8/2005 Klingman O O 2005/0172289 A1 8/2005 Klingman (73) Assignee: Xilinx, Inc., San Jose, CA (US) 2005/0172290 A1 8/2005 Klingman (*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 (21) Appl. No.: 10/769,591 OTHER PUBLICATIONS (22) Filed: Jan. 30, 2004 U.S. Appl. No. 10/769,330, filed Jan. 30, 2004, James-Roxby et al. (51) Int. Cl. (Continued) G06F 7/50 (2006.01) Primary Examiner Thuan Do (52) U.S. Cl. ............................................. 716/18: 718/2 Assistant Examiner Binh Tat (58) Field of Classification Search .................. 716/18, (74) Attorney, Agent, or Firm—Robert Brush 716/2, 3: 709/217: 71.9/313 See application file for complete search history. (57) ABSTRACT (56) References Cited U.S. PATENT DOCUMENTS Programmable architecture for implementing a message 5,867,180 A * 2/1999 Katayama et al. -

Bringing Virtualization to the X86 Architecture with the Original Vmware Workstation

12 Bringing Virtualization to the x86 Architecture with the Original VMware Workstation EDOUARD BUGNION, Stanford University SCOTT DEVINE, VMware Inc. MENDEL ROSENBLUM, Stanford University JEREMY SUGERMAN, Talaria Technologies, Inc. EDWARD Y. WANG, Cumulus Networks, Inc. This article describes the historical context, technical challenges, and main implementation techniques used by VMware Workstation to bring virtualization to the x86 architecture in 1999. Although virtual machine monitors (VMMs) had been around for decades, they were traditionally designed as part of monolithic, single-vendor architectures with explicit support for virtualization. In contrast, the x86 architecture lacked virtualization support, and the industry around it had disaggregated into an ecosystem, with different ven- dors controlling the computers, CPUs, peripherals, operating systems, and applications, none of them asking for virtualization. We chose to build our solution independently of these vendors. As a result, VMware Workstation had to deal with new challenges associated with (i) the lack of virtual- ization support in the x86 architecture, (ii) the daunting complexity of the architecture itself, (iii) the need to support a broad combination of peripherals, and (iv) the need to offer a simple user experience within existing environments. These new challenges led us to a novel combination of well-known virtualization techniques, techniques from other domains, and new techniques. VMware Workstation combined a hosted architecture with a VMM. The hosted architecture enabled a simple user experience and offered broad hardware compatibility. Rather than exposing I/O diversity to the virtual machines, VMware Workstation also relied on software emulation of I/O devices. The VMM combined a trap-and-emulate direct execution engine with a system-level dynamic binary translator to ef- ficiently virtualize the x86 architecture and support most commodity operating systems. -

Standby Power Management Architecture for Deep- Submicron Systems

Standby Power Management Architecture for Deep- Submicron Systems Michael Alan Sheets Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2006-70 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-70.html May 19, 2006 Copyright © 2006, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Standby Power Management Architecture for Deep-Submicron Systems by Michael Alan Sheets B.S.C.E. (Georgia Institute of Technology) 1999 M.S. (University of California, Berkeley) 2003 A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences in the GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY Committee in charge: Professor Jan Rabaey, Chair Professor Robert Brodersen Professor Paul Wright Spring 2006 The dissertation of Michael Alan Sheets is approved: Chair Date Date Date University of California, Berkeley Spring 2006 Standby Power Management Architecture for Deep-Submicron Systems Copyright 2006 by Michael Alan Sheets 1 Abstract Standby Power Management Architecture for Deep-Submicron Systems by Michael Alan Sheets Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences University of California, Berkeley Professor Jan Rabaey, Chair In deep-submicron processes a signi¯cant portion of the power budget is lost in standby power due to increasing leakage e®ects. -

Register Are Used to Quickly Accept, Store, and Transfer Data And

Register are used to quickly accept, store, and transfer data and instructions that are being used immediately by the CPU, there are various types of Registers those are used for various purpose. Among of the some Mostly used Registers named as AC or Accumulator, Data Register or DR, the AR or Address Register, program counter (PC), Memory Data Register (MDR) ,Index register,Memory Buffer Register. These Registers are used for performing the various Operations. While we are working on the System then these Registers are used by the CPU for Performing the Operations. When We Gives Some Input to the System then the Input will be Stored into the Registers and When the System will gives us the Results after Processing then the Result will also be from the Registers. So that they are used by the CPU for Processing the Data which is given by the User. Registers Perform:- 1) Fetch: The Fetch Operation is used for taking the instructions those are given by the user and the Instructions those are stored into the Main Memory will be fetch by using Registers. 2) Decode: The Decode Operation is used for interpreting the Instructions means the Instructions are decoded means the CPU will find out which Operation is to be performed on the Instructions. 3) Execute: The Execute Operation is performed by the CPU. And Results those are produced by the CPU are then Stored into the Memory and after that they are displayed on the user Screen. Types of Registers are as Followings 1. MAR stand for Memory Address Register This register holds the memory addresses of data and instructions. -

Computer Organization

Chapter 12 Computer Organization Central Processing Unit (CPU) • Data section ‣ Receives data from and sends data to the main memory subsystem and I/O devices • Control section ‣ Issues the control signals to the data section and the other components of the computer system Figure 12.1 CPU Input Data Control Main Output device section section Memory device Bus Data flow Control CPU components • 16-bit memory address register (MAR) ‣ 8-bit MARA and 8-bit MARB • 8-bit memory data register (MDR) • 8-bit multiplexers ‣ AMux, CMux, MDRMux ‣ 0 on control line routes left input ‣ 1 on control line routes right input Control signals • Originate from the control section on the right (not shown in Figure 12.2) • Two kinds of control signals ‣ Clock signals end in “Ck” to load data into registers with a clock pulse ‣ Signals that do not end in “Ck” to set up the data flow before each clock pulse arrives 0 1 8 14 15 22 23 A IR T3 M1 0x00 0x01 2 3 9 10 16 17 24 25 LoadCk Figure 12.2 X T4 M2 0x02 0x03 4 5 11 18 19 26 27 5 C SP T1 T5 M3 0x04 0x08 5 6 7 12 13 20 21 28 29 B PC T2 T6 M4 0xFA 0xFC 5 30 31 A CPU registers M5 0xFE 0xFF CBus ABus BBus Bus MARB MARCk MARA MDRCk MDR MDRMux AMux AMux MDRMux CMux 4 ALU ALU CMux Cin Cout C CCk Mem V VCk ANDZ Addr ANDZ Z ZCk Zout 0 Data 0 0 0 N NCk MemWrite MemRead Figure 12.2 (Expanded) 0 1 8 14 15 22 23 A IR T3 M1 0x00 0x01 2 3 9 10 16 17 24 25 LoadCk X T4 M2 0x02 0x03 4 5 11 18 19 26 27 5 C SP T1 T5 M3 0x04 0x08 5 6 7 12 13 20 21 28 29 B PC T2 T6 M4 0xFA 0xFC 5 30 31 A CPU registers M5 0xFE 0xFF CBus ABus BBus -

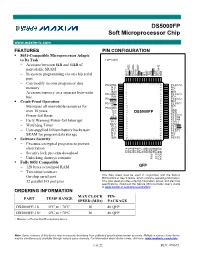

DS5000FP Soft Microprocessor Chip

DS5000FP Soft Microprocessor Chip www.maxim-ic.com FEATURES PIN CONFIGURATION 8051-Compatible Microprocessor Adapts to Its Task TOP VIEW − Accesses between 8kB and 64kB of nonvolatile SRAM LE BD6 PSEN BD5 P2.7/A15 BD4 − In-system programming via on-chip serial BA11 P0.5/AD5 CE2 P0.6/AD6 BA10 P0.7/AD7 CE1 EA N.C. BD7 A port − Can modify its own program or data 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 P0.4/AD4 1 64 P2.6/A14 2 N.C. 63 N.C. memory 3 62 N.C. N.C. BA9 4 61 BD3 − Accesses memory on a separate byte-wide P0.3/AD3 5 60 P2.5/A13 bus BA8 6 59 BD2 P0.2/AD2 7 58 P2.4/A12 Crash-Proof Operation BA13 8 57 BD1 P0.1/AD1 9 56 P2.3/A11 R/W 10 55 BD0 − Maintains all nonvolatile resources for 11 54 P0.0/AD0 VLI VCC0 12 53 GND over 10 years VCC 13 DS5000FP 52 GND 14 51 − Power-fail Reset VCC P2.2/A10 P1.0 15 50 P2.1/A9 BA14 16 49 P2.0/A8 − Early Warning Power-fail Interrupt P1.1 17 48 XTAL1 BA12 18 47 XTAL2 19 − Watchdog Timer P1.2 46 P3.7/RD 20 45 BA7 P3.6/WR − User-supplied lithium battery backs user P1.3 21 44 P3.5/T1 N.C. 22 43 N.C. SRAM for program/data storage N.C. 23 42 N.C. -

Computer Organization and Architecture, Rajaram & Radhakrishan, PHI

CHAPTER I CONTENTS: 1.1 INTRODUCTION 1.2 STORED PROGRAM ORGANIZATION 1.3 INDIRECT ADDRESS 1.4 COMPUTER REGISTERS 1.5 COMMON BUS SYSTEM SUMMARY SELF ASSESSMENT OBJECTIVE: In this chapter we are concerned with basic architecture and the different operations related to explain the proper functioning of the computer. Also how we can specify the operations with the help of different instructions. CHAPTER II CONTENTS: 2.1 REGISTER TRANSFER LANGUAGE 2.2 REGISTER TRANSFER 2.3 BUS AND MEMORY TRANSFERS 2.4 ARITHMETIC MICRO OPERATIONS 2.5 LOGIC MICROOPERATIONS 2.6 SHIFT MICRO OPERATIONS SUMMARY SELF ASSESSMENT OBJECTIVE: Here the concept of digital hardware modules is discussed. Size and complexity of the system can be varied as per the requirement of today. The interconnection of various modules is explained in the text. The way by which data is transferred from one register to another is called micro operation. Different micro operations are explained in the chapter. CHAPTER III CONTENTS: 3.1 INTRODUCTION 3.2 TIMING AND CONTROL 3.3 INSTRUCTION CYCLE 3.4 MEMORY-REFERENCE INSTRUCTIONS 3.5 INPUT-OUTPUT AND INTERRUPT SUMMARY SELF ASSESSMENT OBJECTIVE: There are various instructions with the help of which we can transfer the data from one place to another and manipulate the data as per our requirement. In this chapter we have included all the instructions, how they are being identified by the computer, what are their formats and many more details regarding the instructions. CHAPTER IV CONTENTS: 4.1 INTRODUCTION 4.2 ADDRESS SEQUENCING 4.3 MICROPROGRAM EXAMPLE 4.4 DESIGN OF CONTROL UNIT SUMMARY SELF ASSESSMENT OBJECTIVE: Various examples of micro programs are discussed in this chapter. -

Microprocessor Design

Microprocessor Design en.wikibooks.org March 15, 2015 On the 28th of April 2012 the contents of the English as well as German Wikibooks and Wikipedia projects were licensed under Creative Commons Attribution-ShareAlike 3.0 Unported license. A URI to this license is given in the list of figures on page 211. If this document is a derived work from the contents of one of these projects and the content was still licensed by the project under this license at the time of derivation this document has to be licensed under the same, a similar or a compatible license, as stated in section 4b of the license. The list of contributors is included in chapter Contributors on page 209. The licenses GPL, LGPL and GFDL are included in chapter Licenses on page 217, since this book and/or parts of it may or may not be licensed under one or more of these licenses, and thus require inclusion of these licenses. The licenses of the figures are given in the list of figures on page 211. This PDF was generated by the LATEX typesetting software. The LATEX source code is included as an attachment (source.7z.txt) in this PDF file. To extract the source from the PDF file, you can use the pdfdetach tool including in the poppler suite, or the http://www. pdflabs.com/tools/pdftk-the-pdf-toolkit/ utility. Some PDF viewers may also let you save the attachment to a file. After extracting it from the PDF file you have to rename it to source.7z.