Appendix A: Brief Tutorials of Kicad Schematic with SPICE

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

PLM Weekly Summary Editor: Cimdata News Team 15 January 2021 Contents Cimdata News

PLM Weekly Summary Editor: CIMdata News Team 15 January 2021 Contents CIMdata News ............................................................................................................................................ 2 An Enterprise Digital Transformation Platform – a CIMdata Commentary......................................................2 Aras’ Cloud Strategy – a CIMdata Blog Post ....................................................................................................5 CIMdata Announces its 2021 PLM Market & Industry Forum Series ..............................................................6 CIMdata to Host a Free Webinar on CAD Trends ............................................................................................7 NLign Analytics “Structural Lifecycle Digital Environment” Enables Model-Driven Product Quality – a CIMdata Commentary .......................................................................................................................................8 PTC’s Cloud Strategy – a CIMdata Blog Post ................................................................................................. 13 Acquisitions .............................................................................................................................................. 14 Accenture Acquires Real Protect, Brazil-Based Information Security Company ........................................... 14 Atos to acquire In Fidem to reinforce its cybersecurity position in the North American market .................... 15 Planview -

Simulation Software for Online Teaching of ECE Courses

Paper ID #25855 Simulation Software for Online Teaching of ECE Courses Dr. Alireza Kavianpour, DeVry University, Pomona Dr. Alireza Kavianpour received his PH.D. Degree from University of Southern California (USC). He is currently Senior Professor at DeVry University, Pomona, CA. Dr. Kavianpour is the author and co-author of over forty technical papers all published in IEEE Journals or referred conferences. Before joining DeVry University he was a researcher at the University of California, Irvine and consultant at Qualcom Inc. His main interests are in the areas of embedded systems and computer architecture. c American Society for Engineering Education, 2019 Simulation software for Online teaching of ECE Courses ABSTRACT Online learning, also known as e-learning, has become an increasingly common choice for many students pursuing an education. Online learning requires the student to participate and learn virtually via computer, as opposed to the traditional classroom environment. Although online learning is not for everyone, it's important for prospective students to determine whether or not it's something they would like to pursue. The following are advantages and disadvantages for online learning: Advantages -Online learning provides flexibility because students are able to work when it's convenient for them. Students can do all the homework from any location as long as they have access to a computer. -A student can learn at his or her own pace. -Degrees can be completed in less time compared to traditional universities. -Students have fewer distractions, and it can be less intimidating to participate in the discussions. -Students have the opportunity to connect with and work alongside students from other locations. -

Using the ELECTRIC VLSI Design System Version 9.07

Using the ELECTRIC VLSI Design System Version 9.07 Steven M. Rubin Author's affiliation: Static Free Software ISBN 0−9727514−3−2 Published by R.L. Ranch Press, 2016. Copyright (c) 2016 Static Free Software Permission is granted to make and distribute verbatim copies of this book provided the copyright notice and this permission notice are preserved on all copies. Permission is granted to copy and distribute modified versions of this book under the conditions for verbatim copying, provided also that they are labeled prominently as modified versions, that the authors' names and title from this version are unchanged (though subtitles and additional authors' names may be added), and that the entire resulting derived work is distributed under the terms of a permission notice identical to this one. Permission is granted to copy and distribute translations of this book into another language, under the above conditions for modified versions. Electric is distributed by Static Free Software (staticfreesoft.com), a division of RuLabinsky Enterprises, Incorporated. Table of Contents Chapter 1: Introduction.....................................................................................................................................1 1−1: Welcome.........................................................................................................................................1 1−2: About Electric.................................................................................................................................2 1−3: Running -

A Fedora Electronic Lab Presentation

Chitlesh GOORAH Design & Verification Club Bristol 2010 FUDConBrussels 2007 - [email protected] [ Free Electronic Lab ] (formerly Fedora Electronic Lab) An opensource Design and Simulation platform for Micro-Electronics A one-stop linux distribution for hardware design Marketing means for opensource EDA developers (Networking) From SPEC, Model, Frontend Design, Backend, Development boards to embedded software. FUDConBrussels 2007 - [email protected] Electronic Designers Problems Approx. 6 month design development cycle Tackling Design Complexity Lower Power, Lower Cost and Smaller Space Semiconductor Industry's neck squeezed in 2008 Management (digital/analog) IP Portfolio FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] A basic Design Flow FUDConBrussels 2007 - [email protected] TIP: Use verilator to lint your verilog files. Most of the Veripool tools are available under FEL. They are in sync with Wilson Snyder's releases. FUDConBrussels 2007 - [email protected] FUDConBrussels 2007 - [email protected] GTKWaveGTKWave Don'tDon't forgetforget itsits TCLTCL backendbackend WidelyWidely usedused togethertogether withwith SystemCSystemC FUDConBrussels 2007 - [email protected] Tools Standard Cell libraries FUDConBrussels 2007 - [email protected] BackendBackend designdesign Open Circuit Design, Electric FUDConBrussels 2007 - [email protected], Toped gEDA/gafgEDA/gaf Well known and famous. A very good example of opensource -

Circuitmaker 2000 (The Symbol Will Be Replaced by a Rectangle)

CircuitMaker® 2000 the virtual electronics lab™ CircuitMaker User Manual advanced schematic capture mixed analog/digital simulation Revision A Software, documentation and related materials: Copyright © 1988-2000 Protel International Limited. All Rights Reserved. Unauthorized duplication of the software, manual or related materials by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Protel International Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment. CircuitMaker, TraxMaker, Protel and Tango are registered trademarks of Protel International Limited. SimCode, SmartWires and The Virtual Electronics Lab are trademarks of Protel International Limited. Microsoft and Microsoft Windows are registered trademarks of Microsoft Corporation. Orcad is a registered trademark of Cadence Design Systems. PADS is a registered trademark of PADS Software. All other trademarks are the property of their respective owners. Printed by Star Printery Pty Ltd ii Table of Contents Chapter 1: Welcome to CircuitMaker Introduction............................................................................................1-1 Required User Background..............................................................1-1 Required Hardware/Software...........................................................1-1 -

IDF Exporter IDF Exporter Ii

IDF Exporter IDF Exporter ii April 27, 2021 IDF Exporter iii Contents 1 Introduction to the IDFv3 exporter 2 2 Specifying component models for use by the exporter 2 3 Creating a component outline file 4 4 Guidelines for creating outlines 6 4.1 Package naming ................................................ 6 4.2 Comments .................................................... 6 4.3 Geometry and Part Number entries ...................................... 7 4.4 Pin orientation and positioning ........................................ 7 4.5 Tips on dimensions ............................................... 8 5 IDF Component Outline Tools 8 5.1 idfcyl ....................................................... 9 5.2 idfrect ...................................................... 10 5.3 dxf2idf ...................................................... 11 6 idf2vrml 12 IDF Exporter 1 / 12 Reference manual Copyright This document is Copyright © 2014-2015 by it’s contributors as listed below. You may distribute it and/or modify it under the terms of either the GNU General Public License (http://www.gnu.org/licenses/gpl.html), version 3 or later, or the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/), version 3.0 or later. All trademarks within this guide belong to their legitimate owners. Contributors Cirilo Bernardo Feedback Please direct any bug reports, suggestions or new versions to here: • About KiCad document: https://gitlab.com/kicad/services/kicad-doc/issues • About KiCad software: https://gitlab.com/kicad/code/kicad/issues • About KiCad software i18n: https://gitlab.com/kicad/code/kicad-i18n/issues Publication date and software version Published on January 26, 2014. IDF Exporter 2 / 12 1 Introduction to the IDFv3 exporter The IDF exporter exports an IDFv3 1 compliant board (.emn) and library (.emp) file for communicating mechanical dimensions to a mechanical CAD package. -

Bridging the Gap Between Precise RT-Level Power/Timing Estimation and Fast High-Level Simulation

Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik Bridging the Gap between Precise RT-Level Power/Timing Estimation and Fast High-Level Simulation A method for automatically identifying and characterising combinational macros in synchronous sequential systems at register-transfer level and subsequent executable high-level model generation with respect to non-functional properties Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften von Dipl.-Inform. Kai Hylla Gutachter: Prof. Dr. Wolfgang Nebel Prof. Dr. Wolfgang Rosenstiel Tag der Disputation: 13. Januar 2014 Abstract Knowing a system’s power dissipation and timing behaviour is mandatory for today’s system development and key to an effective design space exploration. Not only does battery lifetime or design of the power supply directly depend on the power dissipation of the system. Second-order effects such as thermal behaviour or degradation effects that are directly or indirectly affected by the power dissipation must be considered, too. Various techniques for power estimation exist at different levels of abstraction. Low-level approaches provide accurate estimation results but require a lot of computational effort. High- level approaches however, allow fast and early estimates, but lack of a deeper knowledge and understanding of the hardware, implementing the behaviour. Therefore, they can only give rough estimates. What is missing is an approach allowing fast and early estimates with respect to as many relevant hardware artefacts and physical properties as possible. This doctoral thesis tackles the problem of a fast, yet accurate power and timing estimation of embedded hardware modules at a high-level of abstraction. A comparatively time consuming low-level estimation is performed once in order to obtain an accurate estimate. -

Industrial Circuit Board Design and Microprocessor Programming Bachelor of Science Thesis in Mechatronics

Industrial circuit board design and microprocessor programming Bachelor of Science thesis in Mechatronics FREDRIK HÖGBERG Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2017 REPORT NO. XXXX XXXX Industrial circuit boar! design and %icroprocessor pro$ram%in$ FREDRIK HÖGBERG Depart%ent of Signal and S'ste%s CH)*MERS UNI,ERSIT- OF TE(HNO*OG- Gothenbur$, S/eden 2017 Industrial circuit board design and microprocessor pro$ra%%in$ FREDRIK HÖGBERG FREDRIK HÖGBERG, 2017 Technical report no xxxx544 Depart%ent of Signals and S'ste%s Chal%ers +ni6ersit' of Technolo$' SE-412 96 G;tebor$ S/eden Telephone + 46 (0)31-772 1000 (o6er5 Hot Screen 2000 is an industrial heat press machine that can be used to attach screen prints on clothin$. This thesis will go in to details on ho/ the circuit board and pro$ra% was ma!e for this %achine. Chal%ers Reproservice G;tebor$. S/eden 2017 CHALMERS Signals and Systems, Bachelor@s Thesis XXXX5XX I Abstract The %ain obAect of this proAect is to design and %aBe circuitr' to control a industrial heat press %achine. The circuitr' consist of a 0 la'er boar! containin$ a %icro controller. displa' %odule. )( DC module. te%perature controller and electronics to control electromechanical devices. The fra%e of reference /ill $o through the basics steps in designin$ and %anufacturin$ electrical circ"itry /ith digital and analo$ technolo$y and explain the basics of the most com%on electrical components use! in circuitr' toda'. The fra%e of reference /ill also sho/ ho/ to create sche%atic and circuit design "sin$ Ki()D and ho/ to pro$ra% a Microchi& %icroprocessor in the C pro$ra%ing lan$"a$e. -

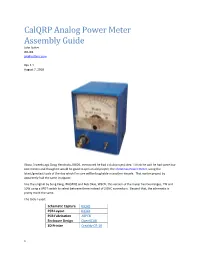

Calqrp Analog Power Meter Assembly Guide John Sutter W1JDS [email protected]

CalQRP Analog Power Meter Assembly Guide John Sutter W1JDS [email protected] Rev 1.1 August 7, 2018 About 3 weeks ago Doug Hendricks, KI6DS, mentioned he had a club project idea. I think he said he had some low cost meters and thought it would be good to spin an old project, the Christmas Power Meter, using the latest/greatest tools of the day which I’m sure will be laughable in another decade. That earlier project by apparently had the same instigator. Like the original by Song Kang, WA3AYQ and Bob Okas, W3CD, this version of the meter has two ranges, 1W and 10W using a SPDT switch to select between them instead of 2 BNC connectors. Beyond that, the schematic is pretty much the same. The tools I used: Schematic Capture KiCAD PCB Layout KiCAD PCB Fabrication AllPCB Enclosure Design OpenSCAD 3D Printer Creality CR-10 1 The Circuit As mentioned earlier the schematic matches the Christmas Power Meter pretty closely. SW1 is used to switch the power from the BNC connector into either the 10W load consisting of four 200 Ω 3 Watt carbon film resistors or the 1W load consisting of two 100 Ω ½ Watt carbon film resistors. The diodes are used as detectors with the resulting voltage filtered by the capacitors. The resistors are used to adjust the full-scale current to 200 μA. More on that later. FIGURE 1 SCHEMATIC A germanium diode was used on the 1 W range due to its lower voltage drop. More on that later. If you decide to use a through hole switch, the maximum shaft diameter is 6.3 mm. -

Minor Changes and Bug Fixes

List of fixed bugs in DipTrace 4.1.3.1 if compared to 4.1.3.0 PCB Layout 1. If IPC-7351 models are used, STEP export does not work. 2. When entering text into table cells "Shift + U" works as a Hotkey. 3. When importing KiCad 5.1 files, SMD pads on the Bottom layer may be imported incorrectly. Schematics 1. When entering text into table cells "Shift + U" works as a Hotkey.. 2. Back Annotate does not update supplier information. List of fixed bugs in DipTrace 4.1.3.0 if compared to 4.1.2.0 General 1. Snap EDA: multiple clicks for page switching result in a long "freezing". PCB Layout 4. The panelization parameters are reset when opening a schematic file in the PCB Layout after starting. 5. D-shape pads are displayed incorrectly in the Mirror mode. 6. The Highlight Net for the Obround and D-shape pads is displayed incorrectly in the Mirror mode. 7. TrueType text is shifted in BOM HTML. 8. DXF with multilayer blocks is imported incorrectly 9. Export of arcs with a very small angle and extra-large radius to Gerber has been changed. 10. Chamfer of the corners of a rectangular board outline may result in incorrect formation of outlines in Gerber when panelizing with Edge Rails. 11. After changing any of the markings parameters for a group of selected objects, the marking for selected Mounting Hole and Fiducial may appear. 12. Dimension objects are not updated automatically after changing the shape dimensions in the shape properties. -

CADSTAR FPGA TRAINING Agenda

CADSTAR FPGA TRAINING Agenda 1. ALDEC Corporate Overview 2. Introduction to Active-HDL 3. Design Entry Methods 4. Efficient Design Management 5. Design Verification – Running Simulation 6. Design Verification- Debugging 7. Synthesis and Implementation in Flow Manager 8. Using the PCB interface Corporate Overview Aldec Focus - Background • Founded 1984 – Dr. Stanley Hyduke • Privately held, profitable and 100% product revenue funded • Leading EDA Technology – VHDL and Verilog Simulation – SystemVerilog – SystemC Co-Verification – Server Farm Manager – IP Cores – Hardware assisted Acceleration/Emulation and Prototyping • Over 30,000 active licenses worldwide • Several key Patents in Verification Technology • Office Locations: – Direct Sales and Support • United States • Japan • Canada • France • ROW – Distribution Channel Corporate Milestones Technology Focus Design Creation • Text, block diagram and state diagram entry • Automatic testbench generation • Automatically created parameterized blocks • Variety of IP cores Verification • Multiple language support (VHDL, [System]Verilog, C++, SystemC) • Assertions (OpenVera, PSL, SystemVerilog) • Direct compilation and common kernel simulation • Co-simulation Interfaces(VHPI/VPI, Matlab/Simulink, SWIFT, …) Technology Focus – cont. Hardware Validation • Hardware assisted acceleration of HDL simulation • Emulation and ASIC prototyping • Hardware / software co-simulation (Embedded Systems, SoC) Niche Solution • Actel CoreMP7 Designs Co-verification (ARM7) • DO-254 Verification Solution • Actel RTAX-S/SL -

Performed the Most Often. in FPGA Design Flow, Functional and Gate

performed the most often. In FPGA design flow, functional and gate-level timing simulation is typically performed when designers suspect that there might be a mismatch between RTL and functional or gate-level timing simulation results, which can lead to an incorrect design. The mismatch can be caused for several reasons discussed in more detail in Tip #59. Note that the nomenclature of simulation types is not consistent. The same name, for instance “gate-level simulation”, can have slightly different meaning in simulation flows of different FPGA vendors. The situation is even more confusing in ASIC simulation flows, which have many more different simulation types, such as transistor-level, and dynamic simulation. The following figure shows simulation types designers can perform during Xilinx FPGA synthesis and physical implementation process. Figure 1: Simulation types Xilinx FPGA designers can perform simulation after each level of design transformation from the original RTL to the bitstream. The following example is a 12-bit OR gate implemented in Verilog. module sim_types(input [11:0] user_in, output user_out); assign user_out = |user_in; endmodule XST post-synthesis simulation model is implemented using LUT6 and LUT2 primitives, which are parts of Xilinx UNISIMS RTL simulation library. wire out, out1_14; LUT6 #( .INIT ( 64'hFFFFFFFFFFFFFFFE )) out1 ( .I0(user_in[3]), .I1(user_in[2]), .I2(user_in[5]), .I3(user_in[4]), .I4(user_in[7]), .I5(user_in[6]), .O(out)); LUT6 #( .INIT ( 64'hFFFFFFFFFFFFFFFE )) out2 ( .I0(user_in[9]), .I1(user_in[8]), .I2(user_in[11]), .I3(user_in[10]), .I4(user_in[1]), .I5(user_in[0]), .O(out1_14)); LUT2 #( .INIT ( 4'hE )) out3 ( .I0(out), .I1(out1_14), .O(user_out) ); Post-synthesis simulation model can be generated using the following command: $ netgen -w -ofmt verilog -sim sim.ngc post_synthesis.v Post-translate simulation model is implemented using X_LUT6 and X_LUT2 primitives, which are parts of Xilinx SIMPRIMS simulation library.