Intel 8255 - Wikipedia, the Free Encyclopedia

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Z80 Microprocessor Architecture

DESIGN AND FABRICATION OF AN ELECTRONIC SYSTEM FOR MONITORING AND CONTROLLING TEMPERATURE, LIGHT ILLUMINANCE AND HUMIDITY IN A GREENHOUSE WYCLIFFE OBANDA NYANYA I56/0243/2003 A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE (ELECTRONICS AND INSTRUMENTATION) IN THE SCHOOL OF PURE AND APPLIED SCIENCES OF KENYATTA UNIVERSITY APRIL 2010 DECLARATION I declare that the work presented in this thesis is my original work and has not been presented for a degree in any other university or for any other award. WYCLIFFE OBANDA NYANYA Signature………………………… Date………… PHYSICS DEPARTMENT KENYATTA UNIVERSITY We confirm that the candidate carried out the work reported in this thesis under our supervision. DR. PATRICK M. KARIMI Signature…………………….......... Date……...... PHYSICS DEPARTMENT KENYATTA UNIVERSITY P. O. BOX 43844-00100 GPO NAIROBI-KENYA DR. ABDALLAH S. MERENGA Signature……………………….... Date …………… PHYSICS DEPARTMENT KENYATTA UNIVERSITY P. O. BOX 43844-00100 GPO NAIROBI- KENYA ii DEDICATION This work is dedicated to my wife, Elizabeth, my daughters Sharon and Louise, my son Mark and to my late father Herbert Ambundo who would have loved to see it all. iii ACKNOWLEDGEMENTS I would like to take this opportunity to thank all my lecturers in the physics department for instilling confidence in me when pursuing this course. Special thanks go to my supervisors, Dr. P. M. Karimi and Dr. A. S. Merenga, for their guidance throughout this research. I also wish to thank my colleague John Githaiga for his useful suggestions. The technicians in the Physics department were very helpful to me during the construction of the system. I also wish to thank my wife Elizabeth Obanda for her moral support and patience. -

Microprocessor Interfacing Techniques

MICROPROCESSOR INTERFACING TECHNIQUES AUSTIN LESEA SYBEX RODNAYZAKS c o to n en MCMXCVn MICROPROCESSOR INTERFACING TECHNIQUES AUSTIN -LESEA RODNAY ZAKS SYBEX Published by: SYBEX Incorporated 2161 Shattuck Avenue Berkeley, California 94704 In Europe: SYBEX-EUROPE 313 rue Lecourbe 75015-Paris, France DISTRIBUTORS L P. ENTERPRISES 313 KINGSTON ROAD ILFORD, Essex. IG1 IPj Tel: 01-553 U $9.95 (USA) FF66 (Europe) FO REWARD Every effort has been made to supply complete and accurate information. However, Sybex assumes no responsibility for its use; nor any infringements of patents or other rights of third parties which would result. No license is granted by the equipment manufacturers under any patent or patent rights. Manufacturers reserve the right to change circuitry at any time without notice. In particular, technical characteristics and prices are subject to rapid change. Comparisons and evaluations are presented for their educational value and for guidance principles. The reader is referred to the manu- facturer's data for exact specifications. Copyright Q) 1977 SYBEX Inc. World Rights reserved. No part of this publication may be stored in a retrieval system, copied, transmitted, or reproduced in any way, including, but not limited to, photocopy, photography, magnetic or other recording, without the prior written permission of the publisher. Library of Congress Card Number: 77-20627 ISBN Number: 0-89588-000-8 Printed in the United States of America Printing 109 8 76 5 43 2 1 CONTENTS PREFACE .5 L INTRODUCTION 7 Concepts, Techniques to be discussed, Bus Introduction, Bus Details II. ASSEMBLING THE CENTRAL PROCESSING UNIT ....... 17 Introduction, The $080, The 6800, The Z-80: Dynamic Memory, The 8085 III. -

Micro Processors and Interfacing Devices

MPMC Course File Contents required for course file 1. Cover Page 2. Syllabus copy 3. Vision of the Department 4. Mission of the Department 5. PEOs and POs 6. Course objectives and outcomes 7. Brief notes on the importance of the course and how it fits into the curriculum 8. prerequisites 9. Instructional Learning Outcomes 10. Course mapping with PEOs and POs 11. Class Time Table 12. Individual Time Table 13. Micro Plan with dates and closure report 14. Detailed notes 15. Additional topics 16. University Question papers of previous years 17. Question Bank 18. Assignment topics 19. Unit wise Quiz Questions 20. Tutorial problems 21. Known gaps ,if any 22. Discussion topics 23. References, Journals, websites and E-links 24. Quality Control Sheets 25. Student List 26. Group-Wise students list for discussion topics 1.cover page GEETHANJALI COLLEGE OF ENGINEERING AND TECHNOLOGY DEPARTMENT OF Electronics and Communication Engineering (Name of the Subject ) : Microprocessors and Microcontrollers Course file (JNTU CODE – 56012) Programme : UG Branch: EEE Version No : 0 Year: III Document No: GCET/ECE/56012/01 Semester: II No. of pages : Classification status (Unrestricted / Restricted ) : Unrestricted Distribution List : Dept. Library, Dept Office, Concerned Faculty Prepared by Updated by: 1) Name : M.Laxmi 1) Name 2) Sign : 2) Sign : 3) Design : Assoc. Professor. 3) Design 4) Date : 12/12/2014 4) Date : Verified by : 1) Name : * For Q.C Only. 2) Sign : 1) Name : 3) Design : 2) Sign : 4) Date : 3) Design : 4) Date : Approved by : (HOD ) 1) Name -

Microprocessors and Interfacing 8086, 8051, 8096, and Advanced Processors

Microprocessors and Interfacing 8086, 8051, 8096, and advanced processors N. Senthil Kumar Professor Department of Electrical and Electronics Engineering Mepco Schlenk Engineering College Sivakasi, Tamil Nadu Press M. Saravanan Professor Department of Electrical and Electronics Engineering Thiagarajar College of Engineering Madurai, Tamil Nadu S. Jeevananthan UniversityProfessor Department of Electrical and Electronics Engineering Pondicherry Engineering College Puducherry S.K. Shah OxfordProfessor and Head Department of Electrical Engineering MS University of Baroda Vadodara, Gujarat © Oxford University Press. All rights reserved. 3 Oxford University Press is a department of the University of Oxford. It furthers the University’s objective of excellence in research, scholarship, and education by publishing worldwide. Oxford is a registered trade mark of Oxford University Press in the UK and in certain other countries. Published in India by Oxford University Press YMCA Library Building, 1 Jai Singh Road, New Delhi 110001, India © Oxford University Press 2012 The moral rights of the author/s have been asserted. First published in 2012 All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing of Oxford University Press, or as expressly permitted by law, by licence, or under terms agreed with the appropriate reprographics rights organization. Enquiries concerning reproduction outside the scope of the above should be sent to the Rights Department, Oxford University Press, at the address above. Press You must not circulate this work in any other form and you must impose this same condition on any acquirer. ISBN-13: 978-0-19-807906-4 ISBN-10: 0-19-807906-0 Typeset in Times New Roman by Trinity Designers & Typesetters, Chennai Printed in India byUniversity Tara Art Printers (P) Ltd, Noida Oxford © Oxford University Press. -

Lecture1423813120.Pdf

Lecture Note On Microprocessor and Microcontroller Theory and Applications Subject Code:BEE-1501 Semester: 5th Branch: EE and EEE Syllabus Disclaimer This document does not claim any originality and cannot be used as a substitute for prescribed textbooks. The information presented here is merely a collection by the committee members for their respective teaching assignments. Various sources as mentioned at the end of the document as well as freely available material from internet were consulted for preparing this document. The ownership of the information lies with the respective authors or institutions. Further, this document is not intended to be used for commercial purpose and the committee members are not accountable for any issues, legal, or otherwise, arising out of this document. The committee members make no representations or warranties with respect to the accuracy or completeness of the contents of this document and specially disclaim any implied warranties of merchantability or fitness for a particular purpose. The committee members shall not be liable for any loss or profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages. MODULE: 1 1. INTRODUCTION TO MICROPROCESSOR AND MICROCOMPUTER ARCHITECTURE: A microprocessor is a programmable electronics chip that has computing and decision making capabilities similar to central processing unit of a computer. Any microprocessor- based systems having limited number of resources are called microcomputers. Nowadays, microprocessor can be seen in almost all types of electronics devices like mobile phones, printers, washing machines etc. Microprocessors are also used in advanced applications like radars, satellites and flights. Due to the rapid advancements in electronic industry and large scale integration of devices results in a significant cost reduction and increase application of microprocessors and their derivatives. -

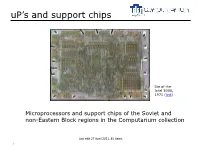

Up's and Support Chips

uP’s and support chips Die of the Intel 8008, 1971 (link) Microprocessors and support chips of the Soviet and non-Eastern Block regions in the Computarium collection Last edit 27 April 2021, 45 items 1 Sections ► Soviet and Eastern Block ► Western and other Regions ( = non-Eastern Block), Up to the 486 period. 2 Soviet and Eastern Block Soviet series (labels are in Cyrillic!): • 580 : i8080 compatible • 1801: PDP-11 compatible • 1804: AMD 2903 compatible • 1810: i8086 compatible • 1816: i8046 compatible • 1821: i8085 compatible • 1858: Z80 compatible See here: Soviet_integrated_circuit_designation history of computing in the Soviet Union conversion table from Cyrillic to Latin alphabet • 3 KR580VM80A Manufact. Electropribor, Rodon Country CCCP Model KR580VM80A Year 1979 Type 8 bit µP Speed 2.5 MHz Clone of i8080A Function microprocessor Clone of the Intel 8080A microprocessor which was introduced in 1974 in the USA. Gift Carlo MULLESCH, COMPUTARIUM http://www.cpushack.com/soviet-cpus.html#2 Database 1360, 1382 4 KR580IK57 Manufact. Country CCCP Model KR580IK57 Year 1989 Type DMA controller Speed Clone of i8257 Function support Clone of the Intel 8257 programmable DMA controller for the 8080 uP family. Gift Carlo MULLESCH http://www.cpushack.com/soviet-cpus.html#2 Database 1361 https://datasheetspdf.com/pdf/702169/IntelCorporation/8257/1 5 KR580VN59 Manufact. Kvantor Country CCCP (Ukraine) Model KR580VN59 Year 1989 Type interrupt controller Speed Clone of i8257 Function support Clone of the Intel 8259 priority interrupt controller for the 8080 uP family. Gift Carlo MULLESCH http://www.cpushack.com/soviet-cpus.html#2 Database 1362 https://datasheetspdf.com/pdf/702169/IntelCorporation/8257/1 6 KR580VG75 Manufact. -

Computers and Microprocessors

Computers and Microprocessors Lecture 35 PHYS3360/AEP3630 1 Contents • Input/output standards • Microprocessor evolution • Computer languages & operating systems • Information encryption/decryption 2 Input/Output Ports • USB (universal serial bus) – intelligent high-speed connection to devices – up to 480 Mbit/s (USB 2.0 Hi-Speed) – USB hub connects multiple devices – enumeration: computer queries devices – supports hot swapping, hot plugging • Parallel – short cable, Enhanced PP up to 2 Mbit/s – common for printers, simpler devices – bidirectional, parallel data transfer (IEEE 1284) – Intel 8255 controller chip 3 Input/Output Ports (2) • Serial – one bit at a time – RS-232 (recommended standard 232) serial port – used with long cables (not longer than ~15 m OK) – low speeds (up to 115 kbit/s) – still widely used to interface instruments – additional standards available: • E.g. RS-422/485 differential signals for better noise immunity, can support speeds in access of 10 Mbit/s (becomes cable- length dependent) 4 Input/Output Ports (3) • IEEE-488 (GPIB) – Has been around for 30 years, many instruments are equipped with it – Allows daisy-chaining up to 15 devices – Updated versions have speeds up to 10Mbit/s 5 Microprocessor Evolution • Generally characterized by the “word” size (registers and data bus) – 8-bit, 16-bit, 32-bit, 64-bit – addressable memory related to the word size • Intel 8080 (1974) – 8-bit, first truly usable µ−processor (40 DIP) – seven 8-bit registers (six of which can be combined as three 16-bit registers) – 6K transistors, -

Parallel Communication Interface and Functional Block Diagram

PARALLEL COMMUNICATION INTERFACE AND FUNCTIONAL BLOCK DIAGRAM The Intel 8255 (or i8255 ) Programmable Peripheral Interf ace chip is a peripheral chip originally developed for the Intel 8085 m icroprocessor, and as such is a member of a large array of such chips, known as the MCS-85 Family.This chip was later also used with the Intel 8086 and its descendants. It was later made (cloned) by many other manufacturers. It is made in DIP 40 and PLCC 44 pins encapsulated versions. This chip is used to give the CPU access to programmable parallel I/O, and is similar to other such chips like the Motorola 6520 PIA (Peripheral Interface Adapter) the MOS Technology 6522 (Versatile Interface Adapter) and the MOS Technology CIA (Complex Interface Adapter) all developed for the 6502 family. Other such chips are the 2655 Programmable Peripheral Interface from the Signetics 2650 family of microprocessors, the 6820 PIO (Peripheral Input/Output) from the Motorola 6800 family, the Western Design Center WDC 65C21, an enhanced 6520, and many others.The 8255 is widely used not only in many microcomputer/microcontroller systems especially Z-80 base d, home computers such as SV-328 and all MSX, but also in the system board of the best known original IBM-PC, PC/XT, PC/jr, etc. and clones.However, most often the functionality the 8255 offered is now not implemented with the 8255 chip itself anymore, but is embedded in a larger VLSI chip as a sub function. The 8255 chip itself is still made, and is sometimes used together with a micro controller to expand its I/O capabilities.