Intel® Core™ I7-800 and I5-700 Desktop Processor Series Datasheet, Volume 2 /Processor/Datashts/322165.Pdf

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intel® Server Board S3420GP

Intel® Server Board S3420GP Technical Product Specification Intel order number E65697-010 Revision 2.4 January, 2011 Enterprise Platforms and Services Division - Marketing Revision History Intel® Server Board S3420GP TPS Revision History Date Revision Modifications Number Feb. 2009 0.3 Initial release. May 2009 0.5 Update block diagram. July. 2009 0.9 Updated POST error code and diagram. Aug. 2009 1.0 Updated MTBF. Nov. 2009 1.1 Additional details for memory configuration. Dec. 2009 1.2 Added Intel® Server Board S3420GPV details. Dec. 2009 2.0 Updated processor name. Jan. 2010 2.1 Corrected the typo. Apr. 2010 2.2 Corrected the typo, updated processor name and remove CCC certification marking information. July. 2010 2.3 Corrected the typo. Jan.2011 2.4 Corrected the typo. Added RDIMM support on S3420GPV. Updated Table 45. Add USB device readiness beep code information. ii Revision 2.4 Intel order number E65697-010 Intel® Server Board S3420GP TPS Disclaimers Disclaimers Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. -

2Nd Generation Intel Core Processor Family with Intel 6 Series Chipset Development Kit User Guide

2nd Generation Intel® Core™ Processor Family with Intel® 6 Series Chipset Development Kit User Guide March 2011 Document Number: 325208 About This Document INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. Intel may make changes to specifications and product descriptions at any time, without notice. Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Intel processor numbers are not a measure of performance. -

Multiprocessing Contents

Multiprocessing Contents 1 Multiprocessing 1 1.1 Pre-history .............................................. 1 1.2 Key topics ............................................... 1 1.2.1 Processor symmetry ...................................... 1 1.2.2 Instruction and data streams ................................. 1 1.2.3 Processor coupling ...................................... 2 1.2.4 Multiprocessor Communication Architecture ......................... 2 1.3 Flynn’s taxonomy ........................................... 2 1.3.1 SISD multiprocessing ..................................... 2 1.3.2 SIMD multiprocessing .................................... 2 1.3.3 MISD multiprocessing .................................... 3 1.3.4 MIMD multiprocessing .................................... 3 1.4 See also ................................................ 3 1.5 References ............................................... 3 2 Computer multitasking 5 2.1 Multiprogramming .......................................... 5 2.2 Cooperative multitasking ....................................... 6 2.3 Preemptive multitasking ....................................... 6 2.4 Real time ............................................... 7 2.5 Multithreading ............................................ 7 2.6 Memory protection .......................................... 7 2.7 Memory swapping .......................................... 7 2.8 Programming ............................................. 7 2.9 See also ................................................ 8 2.10 References ............................................. -

Desktop 3Rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, Desktop Intel® Celeron® Processor Family, and LGA1155 Socket

Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, Desktop Intel® Celeron® Processor Family, and LGA1155 Socket Thermal Mechanical Specifications and Design Guidelines (TMSDG) January 2013 Document Number: 326767-005 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. A “Mission Critical Application” is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined”. -

S2600GZ and S2600GL

Intel® Server Board S2600GZ/GL Technical Product Specification Revision 2.4 October 2014 Revision History Intel® Server Board S2600GZ/GL TPS Revision History Date Revision Modifications Number January 2012 1.0 First public release. Deleted section 6.9.2 Fan Profile. Deleted chapter 11 - Environmental Limits Specification. March 2012 1.1 . Added chapter 12 - BIOS Setup Utility. Added Figure 17. Intel® Server Board S2600GZ/GL PCI Layout. Added support for Intel® Xeon® processor E5-2600 v2 product family . Updated memory support tables August 2013 2.0 . Corrected POST code table - E0h – E3h . Updated reference documents table . Corrected Table 39 - pin out for on-board 7-pin SATA connectors. Updated PCIe Gen 3 support verbiage – section 3.2.5 . Added Phase Shedding support verbiage – section 3.2.4.1.1 February 2014 2.1 . Updated BIOS Setup options to include Phase Shedding option, PCIe Gen3 support option. Updated BIOS Setup options to include Extended ATR option, PFloor tuning option, Memory Mapped I/O Size option, PCIe AER Support option, Log Correctable Errors option and System Early POST Timeout option. Corrected Figure 9 and Figure 16 – PCIe Gen1x48GB/s April 2014 2.2 . Updated BIOS Setep options to include Phase Shedding and Memory SPD Override options. Updated Table 37. System Status LED State Definitions – Remove the “Battery Failure” from Description column. June 2014 2.3 . Updated Table 51. SystemStatus LED State Definitions – Remove the “Battery Failure” from Description column. October 2014 2.4 . Add note for Figure 29. ii Revision 2.4 Intel® Server Board S2600GZ/GL TPS Disclaimers Disclaimers INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. -

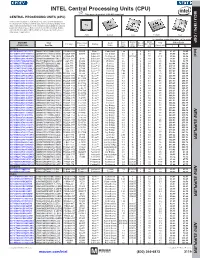

CPU) MCU / MPU / DSP This Page of Product Is Rohs Compliant

INTEL Central Processing Units (CPU) MPU /DSP MCU / This page of product is RoHS compliant. CENTRAL PROCESSING UNITS (CPU) Intel Processor families include the most powerful and flexible Central Processing Units (CPUs) available today. Utilizing industry leading 22nm device fabrication techniques, Intel continues to pack greater processing power into smaller spaces than ever before, providing desktop, mobile, and embedded products with maximum performance per watt across a wide range of applications. Atom Celeron Core Pentium Xeon For quantities greater than listed, call for quote. MOUSER Intel Core Cache Data Price Each Package Processor Family Code Freq. Size No. of Bus Width TDP STOCK NO. Part No. Series Name (GHz) (MB) Cores (bit) (Max) (W) 1 10 Desktop Intel 607-DF8064101211300Y DF8064101211300S R0VY FCBGA-559 D2550 Atom™ Cedarview 1.86 1 2 64 10 61.60 59.40 607-CM8063701444901S CM8063701444901S R10K FCLGA-1155 G1610 Celeron® Ivy Bridge 2.6 2 2 64 55 54.93 52.70 607-RK80532RC041128S RK80532RC041128S L6VR PPGA-478 - Celeron® Northwood 2.0 0.0156 1 32 52.8 42.00 40.50 607-CM8062301046804S CM8062301046804S R05J FCLGA-1155 G540 Celeron® Sandy Bridge 2.5 2 2 64 65 54.60 52.65 607-AT80571RG0641MLS AT80571RG0641MLS LGTZ LGA-775 E3400 Celeron® Wolfdale 2.6 1 2 64 65 54.93 52.70 607-HH80557PG0332MS HH80557PG0332MS LA99 LGA-775 E4300 Core™ 2 Conroe 1.8 2 2 64 65 139.44 133.78 607-AT80570PJ0806MS AT80570PJ0806MS LB9J LGA-775 E8400 Core™ 2 Wolfdale 3.0 6 2 64 65 207.04 196.00 607-AT80571PH0723MLS AT80571PH0723MLS LGW3 LGA-775 E7400 Core™ 2 Wolfdale -

LGA1150 Socket — Application Guide

LGA1150 Socket Application Guide September 2013 Order No.: 328999-002 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. -

Comptia A+ Complete Study Guide A+ Essentials (220-601) Exam Objectives

4830bperf.fm Page 1 Thursday, March 8, 2007 10:03 AM CompTIA A+ Complete Study Guide A+ Essentials (220-601) Exam Objectives OBJECTIVE CHAPTER Domain 1.0 Personal Computer Components 1.1 Identify the fundamental principles of using personal computers 1 1.2 Install, configure, optimize and upgrade personal computer components 2 1.3 Identify tools, diagnostic procedures and troubleshooting techniques for personal computer components 2 1.4 Perform preventative maintenance on personal computer components 2 Domain 2.0 Laptops and Portable Devices 2.1 Identify the fundamental principles of using laptops and portable devices 3 2.2 Install, configure, optimize and upgrade laptops and portable devices 3 2.3 Identify tools, basic diagnostic procedures and troubleshooting techniques for laptops and portable devices 3 2.4 Perform preventative maintenance on laptops and portable devices 3 Domain 3.0 Operating Systems 3.1 Identify the fundamentals of using operating systems 4 3.2 Install, configure, optimize and upgrade operating systems 5 3.3 Identify tools, diagnostic procedures and troubleshooting techniques for operating systems 6 3.4 Perform preventative maintenance on operating systems 6 Domain 4.0 Printers and Scanners 4.1 Identify the fundamental principles of using printers and scanners 7 4.2 Identify basic concepts of installing, configuring, optimizing and upgrading printers and scanners 7 4.3 Identify tools, basic diagnostic procedures and troubleshooting techniques for printers and scanners 7 Domain 5.0 Networks 5.1 Identify the fundamental -

Five9ns T3110 Tower Server

FIVE9NS DATA SHEET Note: This data sheet is for informational purposes. It is not a commitment to deliver hardware features or functionality. The development, release and timing of features and functionality described in this document are at the sole discretion of Five9 Network Systems. FIVE9NS T3110 TOWER SERVER The Five9NS T3110 is an entry-level, single socket, tower server. Powered by an Intel processor, this high-performance system provides I/O slot flexibility that enables seamless integration into a variety of OEM applications. HIGHLIGHTS: Flexible Tower Server Variety of expansion slots The Five9NS T3110 was designed with OEM needs in mind. With its Tower form factor rich feature set – including 7 expansion slots, remote management Supports Windows, Linux and capabilities, and high performance Intel 3400 series processor it’s an Solaris Operating Systems ideal fit for commercial printing and healthcare environments. The Remote system management Five9NS T3110 tower server is on the Oracle Solaris Hardware capabilities ideal for central Compatibility List (HCL). office and other demanding environments Easy to customize and integrate Specialty Services into existing infrastructure Easy to scale out as business OEM customers can choose from a host of services that will accelerate needs grow the integration process and reduce time to market. With our in-house Product Lifecycle Management service, Five9NS is uniquely positioned to architect systems for OEM customers. The Five9NS T3110 tower server is customizable and you can brand it as your own. We also provide free engineering support via experts who understand the unique requirements of OEM customers. The Five9NS Product Lifecycle Management service aims to help you proactively manage your product lifecycle. -

Intel® Celeron™ P4000 and U3000 Mobile Processor Series

Intel® Celeron™ P4000 and U3000 Mobile Processor Series External Design Specification — Volume One This is volume 1 of 2. Refer to Document 416057 for Volume 2 Rev 1.5 March 2010 Intel Confidential Document Number:442690 INFORMATIONLegal Lines and Disclaimers IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. -

HP Pavilion Dv6 Entertainment PC

HP Pavilion dv6 Entertainment PC Maintenance and Service Guide © Copyright 2011 Hewlett-Packard Development Company, L.P. ATI Mobility Radeon is a registered trademark of Advanced Micro Devices, Inc. Bluetooth is a trademark owned by its proprietor and used by Hewlett- Packard Company under license. Intel and Core are trademarks of Intel Corporation in the U.S. and other countries. Microsoft and Windows are U.S. registered trademarks of Microsoft Corporation. SD Logo is a trademark of its proprietor. The information contained herein is subject to change without notice. The only warranties for HP products and services are set forth in the express warranty statements accompanying such products and services. Nothing herein should be construed as constituting an additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein. First Edition: January 2011 Document Part Number: 634586-001 Safety warning notice WARNING! To reduce the possibility of heat-related injuries or of overheating the computer, do not place the computer directly on your lap or obstruct the computer air vents. Use the computer only on a hard, flat surface. Do not allow another hard surface, such as an adjoining optional printer, or a soft surface, such as pillows or rugs or clothing, to block airflow. Also, do not allow the AC adapter to contact the skin or a soft surface, such as pillows or rugs or clothing, during operation. The computer and the AC adapter comply with the user-accessible surface temperature limits defined by the International Standard for Safety of Information Technology Equipment (IEC 60950). -

Computer Hardware and Servicing

GOVERNMENT OF TAMILNADU DIRECTORATE OF TECHNICAL EDUCATION CHENNAI – 600 025 STATE PROJECT COORDINATION UNIT Diploma in Computer Engineering Course Code: 1052 M – Scheme e-TEXTBOOK on Computer Hardware and Servicing for VI Semester Diploma in Computer Engineering Convener for Computer Engineering Discipline: Tmt.A.Ghousia Jabeen Principal TPEVR Government Polytechnic College Vellore- 632202 Team Members for Computer Hardware and Servicing: Mr. M. Suresh Babu HOD / Computer Engineering, N.P.A. Centenary Polytechnic College, Kotagiri – 643217 Mr. H.Ganesh Lecturer (SG) / Computer Engineering, N.P.A. Centenary Polytechnic College, Kotagiri – 643217 Dr. S.Sharmila HOD / IT P.S.G. Polytechnic College, Coimbatore – 641001. Validated by Dr. S. Brindha HOD/Computer Networks, PSG Polytechnic College, Coimbatore – 641001. CONTENTS Unit No. Name of the Unit Page No. 1 MOTHERBOARD COMPONENTS 1 2 MEMORY AND I/O DEVICES 33 3 DISPLAY, POWER SUPPLY AND BIOS 91 4 MAINTENANCE AND TROUBLE SHOOTING OF 114 DESKTOP & LAPTOP COMPUTERS 5 MOBILE PHONE SERVICING 178 Unit-1 Motherboard Components UNIT -1 MOTHERBOARD COMPONENTS Learning Objectives: Learner should be able to ➢ Acquire the skills of motherboard and its components ➢ Explain the basic concepts of processor. ➢ Differentiate the types of processor technology ➢ Describe the concepts of chipsets ➢ Differentiate the features of PCI,AGP, USB and processor bus Introduction: To troubleshoot the PC effectively, a student must be familiar about the components and its features. This chapter focuses the motherboard and its components. Motherboard is an important component of the PC. The architecture and the construction of the motherboard are described. This chapter deals the various types of processors and its features.