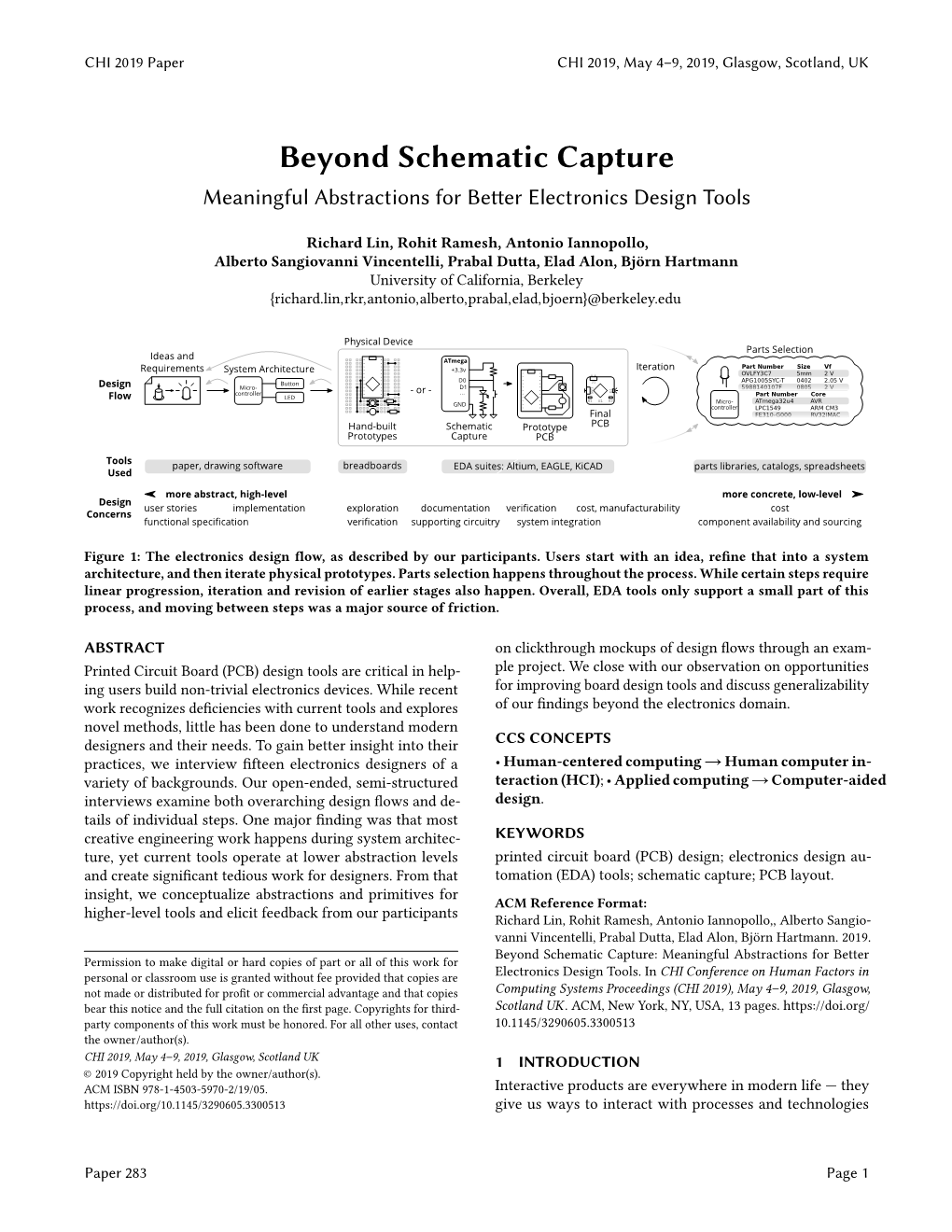

Beyond Schematic Capture Meaningful Abstractions for Better Electronics Design Tools

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Multicap 9 Schematic Capture User Guide

Electronics WorkbenchTM Multicap 9 Schematic Capture User Guide TitleShort-Hidden (cross reference text) February 2006 371889A-01 Support Worldwide Technical Support and Product Information ni.com National Instruments Corporate Headquarters 11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100 Worldwide Offices Australia 1800 300 800, Austria 43 0 662 45 79 90 0, Belgium 32 0 2 757 00 20, Brazil 55 11 3262 3599, Canada 800 433 3488, China 86 21 6555 7838, Czech Republic 420 224 235 774, Denmark 45 45 76 26 00, Finland 385 0 9 725 725 11, France 33 0 1 48 14 24 24, Germany 49 0 89 741 31 30, India 91 80 41190000, Israel 972 0 3 6393737, Italy 39 02 413091, Japan 81 3 5472 2970, Korea 82 02 3451 3400, Lebanon 961 0 1 33 28 28, Malaysia 1800 887710, Mexico 01 800 010 0793, Netherlands 31 0 348 433 466, New Zealand 0800 553 322, Norway 47 0 66 90 76 60, Poland 48 22 3390150, Portugal 351 210 311 210, Russia 7 095 783 68 51, Singapore 1800 226 5886, Slovenia 386 3 425 4200, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 0 8 587 895 00, Switzerland 41 56 200 51 51, Taiwan 886 02 2377 2222, Thailand 662 278 6777, United Kingdom 44 0 1635 523545 For further support information, refer to the Technical Support Resources and Professional Services page. To comment on National Instruments documentation, refer to the National Instruments Web site at ni.com/info and enter the info code feedback. -

Printed Circuit Board Design: a Guide for EE210 Students

Printed Circuit Board Design: A Guide for EE210 Students So, you took EE210 and learned all about how to capture schematics and perform simulations in Multisim, but now you want to make a PCB for your new circuit design. The 30-minute run through of Ultiboard left you scratching your head and you want to know how to make a PCB for REAL. This guide will show you the complete process for designing a printed circuit board, which includes schematic capture, simulation, and layout. Depending on the circuit you are making a PCB for, this process should take 3-5 hours to complete. What is a PCB? A printed circuit board, or PCB, is an assembly that mechanically supports electronic components while electrically connecting them through conductive traces. PCBs are typically constructed of a fiberglass substrate called FR4 that is covered in copper on both sides. The substrate acts as the mechanical core of the PCB that holds everything in place, while the copper layers are used to form traces, which are the copper connections that electrically connect each component Why make a PCB? You have constructed many circuits on a breadboard as part of your EE210 lab and you may wonder: Why go through all the trouble of making a PCB? There are several reasons to move a circuit from a breadboard to a PCB. PCBs are more mechanically stable, offer better performance if well designed, and can be mass produced. For these reasons, PCB design is often an essential part of designing electronics. What you will need • Computer with Multisim and Ultiboard • Printer Both of these materials can be found in Electrical Engineering Department computer labs. -

Introduction to Multisim Schematic Capture and SPICE Simulation

Introduction to Multisim Schematic Capture and SPICE Simulation By: Erik Luther Janell Rodriguez Introduction to Multisim Schematic Capture and SPICE Simulation By: Erik Luther Janell Rodriguez Online: < http://cnx.org/content/col10369/1.3/ > CONNEXIONS Rice University, Houston, Texas This selection and arrangement of content as a collection is copyrighted by Erik Luther, Janell Rodriguez. It is licensed under the Creative Commons Attribution 2.0 license (http://creativecommons.org/licenses/by/2.0/). Collection structure revised: September 26, 2006 PDF generated: October 26, 2012 For copyright and attribution information for the modules contained in this collection, see p. 81. Table of Contents 1 Introduction 1.1 Objectives for the National Instruments Multisim Course . 1 1.2 Interactive Schematic Capture and Layout in National Instruments Multisim . 4 1.3 Exercise: Introducing the National Instruments Multisim Environment . .. 9 2 Schematic Capture 2.1 Electrical and Electronic Components Available in National Instruments Multisim . 11 2.2 Exercise: Finding and Placing Components in National Instruments Multisim . .. 19 2.3 Electrical and Electronic Component Manipulation in National Instruments Mul- tisim .......................................................................................21 2.4 Exercise: Drawing A Schematic in National Instruments Multisim . 26 3 Circuits 3.1 Creating Circuits in Multisim . .. 29 3.2 Using Electrical Rules Checking in National Instruments Multisim . 31 3.3 Creating and Using Sub-Circuits in National Instruments Multisim . 33 3.4 Generating Schematic Reports and Annotation in National Instruments Multisim . 36 4 Simulation 4.1 Simulating Circuits using the SPICE in National Instruments Multisim . 39 4.2 Instrumenting a Circuit Simulation in National Instruments Multisim . .. 44 4.3 Exercise: Instrumenting Simulated Circuits in National Instruments Multisim . -

The Printed Circuit Designer's Guide To... Executing

Executing Complex PCBs 2nd Edition Scott Miller Freedom CAD Services The Printed Circuit Designer's Guide to...™ Executing Complex PCBs 2nd Edition Scott Miller FREEDOM CAD SERVICES INC. © 2019 BR Publishing Inc. All rights reserved. BR Publishing Inc. dba: I-Connect007 942 Windemere Dr. NW Salem, OR 97304 U.S.A. ISBN: 978-0-9980402-4-0 Visit I-007eBooks.com for more books in this series. I-Connect007.com Peer Reviewers John R. Watson, CID Building Control Division Legrand, North America John R. Watson, CID, has worked in the PCB design field for nearly 20 years. In that time, he has held almost every position available. As the senior PCB engineer, John leads a team of 50+ designers in multiple divisions spanning the world in the Building Control Division of Legrand North America. Although he is a highly sought out speaker and writer, John’s passion still lies with mentoring and teaching, espe- cially young people. Stephen V. Chavez, CID/CID+ IPC Designers Council Executive Board Stephen V. Chavez, CID/CID+, is a member of the IPC Designers Council Executive Board and a lead electrical designer at a large, globally recognized aerospace company. He is an IPC CID+ certified designer and has been involved with the PCB design industry, both domestically and internationally, for over 28 years. Further, Stephen is an IPC CID designer certification instructor (CIT) with EPTAC Corporation and VP of the Phoenix chapter of the IPC Designers Council. He has also been a keynote speaker at several design forums at IPC APEX EXPO and other industry confer- ences and seminars and has published several industry articles to date. -

XSCHEM PDF Manual

XSCHEM 0.29 Manual and Tutorials XSCHEM : schematic capture and netlisting EDA tool Xschem is a schematic capture program, it allows creation of hierarchical representation of circuits with a top down approach . By focusing on interfaces, hierarchy and instance properties a complex system can be described in terms of simpler building blocks. A VHDL or Verilog or Spice netlist can be generated from the drawn schematic, allowing the simulation of the circuit. Key feature of the program is its drawing engine written in C and using directly the Xlib drawing primitives; this gives very good speed performance, even on very big circuits. The user interface is built with the Tcl-Tk toolkit, tcl is also the extension language used. Features hierarchical schematic drawings, no limits on size any object in the schematic can have any sort of properties (generics in VHDL, parameters in Spice or Verilog) new Spice/Verilog primitives can be created, and the netlist format can be defined by the user tcl extension language allows the creation of scripts; any user command in the drawing window has an associated tcl comand VHDL / Verilog / Spice netlist, ready for simulation Behavioral VHDL / Verilog code can be embedded as one of the properties of the schematic block, Xschem runs on UNIX systems with X11 and Tcl-Tk toolkit installed. Documentation XSCHEM manual Download Current release Old XSCHEM releases on Sourceforge SVN: svn checkout svn://repo.hu/xschem/trunk License 1 XSCHEM 0.29 Manual and Tutorials The software is released under the GNU GPL, -

A Visual Tutorial for Schematics

A Tutorial for Schematics - the PSpice Schematic Capture Utility * Schematics Netlist X_U1 $N_0002 $N_0003 $N_0004 $N_0005 $N_0001 UA741 V_VCC $N_0004 0 dc 10 V_VEE $N_0005 0 dc -10 V_Vin $N_0006 0 dc 0 ac 1 R_R1 $N_0006 $N_0007 2732 R_R2 $N_0007 $N_0002 2732 R_R4 $N_0003 $N_0001 1.52k R_R3 0 $N_0003 10k C_C1 $N_0007 $N_0001 1n C_C2 0 $N_0002 1n X_U2 $N_0008 $N_0009 $N_0004 $N_0005 vout UA741 R_R1B $N_0001 $N_0010 2732 R_R2B $N_0010 $N_0008 2732 Outline/Contents PART I. PSPICE FUNDAMENTALS I. Introductory Remarks ……………………………………………………………… 3 A. Spice, PSpice and Schematics B. Font Conventions C. The Passive Sign Convention and PSpice II. What is Schematics and what can it do for you? ………………………………….... 4 III. Units and Unit Prefixes ………………………………………………………..…… 4 PART II. CONSTRUCTING AND SIMULATING A DC CIRCUIT I. Drawing Circuit Diagrams with Schematics …………………………………….….. 5 A. Getting Parts …………………………………………………………………….. 6 B. Changing a Part’s Name and Attributes ………………………………………… 7 C. Arranging Parts and Pin Numbers ………………………………………………. 8 D. Wiring Parts ……………………………………………………………………... 8 E. The Analog Ground ………………………………………………………………9 F. Saving Schematics ………………………………………………………………. 9 II. Getting Results ………………………....………………………………………..….. 10 A. The Netlist, Arrgh! B. Naming Nodes …………………………………………………………………. 10 C. Displaying Results on the Schematic ………………………………………….. 11 D. Printing your Drawing …………………………………………………………. 11 III. Running PSpice from Schematics and Choosing an Analysis Type ……………….. 13 A. Obtaining a Bias Point Detail ……………………………………………… 14 B. Obtaining a dc Sweep ……………..………………….…………………… 15 IV. Running and Using PROBE ……………………………………………………….. 16 A. Adding Traces B. Using Markers C. Other PROBE Features - Label, Cursor, Copying and Saving ……………….. 19 V. Printing your Drawing. ……………………………..……………………………… 12 VI. Your First Schematic ………………………………………………………………. 20 PART III. CONSTRUCTING AND SIMULATING AN AC CIRCUIT I. Obtaining an ac Analysis and making Bode Plots …………………………………. -

Eeschema.Pdf

Eeschema Eeschema ii January 22, 2019 Eeschema iii Contents 1 Introduction to Eeschema 1 1.1 Description ...................................................... 1 1.2 Technical overview .................................................. 1 2 Generic Eeschema commands 3 2.1 Mouse commands ................................................... 4 2.1.1 Basic commands ............................................... 4 2.1.2 Block operations ............................................... 4 2.2 Hotkeys ........................................................ 5 2.3 Grid .......................................................... 7 2.4 Zoom selection .................................................... 7 2.5 Displaying cursor coordinates ............................................. 8 2.6 Top menu bar ..................................................... 8 2.7 Upper toolbar ..................................................... 8 2.8 Right toolbar icons .................................................. 10 2.9 Left toolbar icons ................................................... 11 2.10 Pop-up menus and quick editing ............................................ 11 3 Main top menu 14 3.1 File menu ....................................................... 14 3.2 Preferences menu ................................................... 15 3.2.1 Manage Symbol Library Tables ........................................ 16 3.2.1.1 Add a new library ......................................... 16 3.2.1.2 Remove a library .......................................... 16 3.2.1.3 -

Starting with Geda at the Cambridge University Engineering Department

Starting with gEDA at the Cambridge University Engineering Department July 29, 2005 1 CONTENTS CONTENTS Contents 1 Introduction 6 2 gEDA Manager 9 3 Prerequisite 12 4 First steps with Schematic Capture 14 4.1 Add a component . 14 4.2 Create a component . 15 4.3 Edit the attributes . 17 4.4 Copy the components . 18 4.5 Wire the Schematic . 18 4.6 Add a title border . 19 4.7 Print out the Schematic . 20 5 First steps with PCB Layout 22 5.1 Create a PCB file . 22 5.2 Import the schematic . 23 5.3 Route the PCB . 24 5.4 Print out the PCB . 29 6 First steps with Gerber Viewer 32 6.1 View the gerber files . 32 7 First steps with NGSPICE 35 7.1 Gathering the symbols and the models . 35 7.2 Creating the Schematic . 36 7.3 Generation of the netlist . 38 7.4 Simulate your circuit with NGSPICE . 38 7.5 Simulate your circuit with GSPICEUI . 39 8 Frequently Asked Questions (FAQ) 43 8.1 About Schematic Capture . 43 8.1.1 I can't find the component I need! . 43 8.2 About gsch2pcb . 43 8.2.1 gsch2pcb return “Bad expression”? . 43 8.3 About PCB Layout . 43 8.3.1 My component look weird! . 43 8.3.2 What are the rule to make a PCB? . 43 8.3.3 What If I change my schematic after having created my PCB? . 44 8.3.4 How to route the PCB by hand? . 44 2 CONTENTS CONTENTS 8.4 About Spice . -

Best Free Pcb Cad

Best free pcb cad click here to download Now, before we get into the five best and free PCB design programs, it is to design schematics, you can do no wrong by going with TinyCAD. Do you need a free PCB design software or tool to put in practice the new electronic PCBWeb is a free CAD application for designing and manufacturing. Free PCB CAD Software. This is a comparison of printed circuit board design software. Our criteria for including a PCB CAD program are: There should be a. CircuitMaker is the best free PCB design software by Altium for Open Source Hardware Designers, Hackers, Makers, Students and Hobbyists.Projects · Components · Blog · Hubs. 10 best free pcb designing software open source software download. TinyCAD helps user to draw circuit diagrams and export it as a PCB. Eagle is a very good piece of software. Specifically, the non-free versions scale up to much bigger targets. Meanwhile, you have all of those What is the best free PCB designing application. I always recomment FreePCB, but it lacks one component you Anyone who thinks its the best more than likely hasn't used anything else. The world of PCB CAD software has been very active in recent years – so much so that it's easy to lose track of all the players and products. PCB design: you need a CAD program for your project, but which is best? There are They range from free or inexpensive to high-end/premium. They come. Free CAD Software. Start by downloading our free CAD software. -

Computer Aided Design of Electronic Devices

TOMSK POLYTECHNIC UNIVERSITY O.A. Kozhemyak, D.N. Ogorodnikov COMPUTER AIDED DESIGN OF ELECTRONIC DEVICES It is recommended for publishing as a study aid by the Editorial Board of Tomsk Polytechnic University Tomsk Polytechnic University Publishing House 2014 1 UDC 621.38(075.8) BBC 31.2 K58 Kozhemyak O.A. K58 Computer aided design of electronic devices: study aid / O.A. Kozhemyak, D.N. Ogorodnikov; Tomsk Polytechnic University. – Tomsk: TPU Publishing House, 2014. – 130 p. This textbook focuses on the basic notions, history, types, technology and applications of computer-aided design. Methods of electronic devices simulation, automated design of power electronic devices and components, constructive- technological design are considered and discussed. Some features of the popular electronics CADs are also shown. There are a lot of practical examples using CADs of electronics. The textbook is designed at the Department of Industrial and Medical Electronics of TPU. It is intended for students majoring in the specialty „Electronics and Nanoelectronics‟. UDC 621.38(075.8) BBC 31.2 Reviewer Cand.Sc, Head of Laboratory, Tomsk State University of Control Systems and Radioelectronics Aleksandr V. Osipov © STE HPT TPU, 2014 © Kozhemyak O.A., Ogorodnikov D.N., 2014 © Design. Tomsk Polytechnic University Publishing House, 2014 2 Introduction. CAD around Us ........................................................................... 5 What is CAD? ................................................................................................ 5 Overview -

Exhibitor Profiles

National Electronics Week 11 – 12 March 2014, Gallagher Convention Centre, Midrand Exhibitor profiles Allan Mckinnon & Associates Deltronics Stand number: B17 Contact: Vangeli Glyptis Stand number: 4-18 Contact: Rob Sterling Tel: 083 309-9785 | [email protected] | Tel: 021 705-7741 | [email protected] | www.deltronics.co.za www.ama-sa.co.za & www.testerion.co.za Deltronics is an innovative contract electronics design company specialising in the design of custom products, embedded systems and Allan McKinnon and associates have been supplying the South African wireless technologies. We focus on fully understanding all aspects of the electronics industry with equipment, consumables and process clients’ requirements. Deltronics is a distributor of Altium Designer, Tasking assistance for over 30 years. Products, JTAG Technologies, JTAG Studio Live and Topor Auto Router. We’re also a registered Altium, Tasking and JTAG Technologies training Asic Design Services facility with certified trainers experienced from entry level to FPGA and Simulation. Deltronics provides product training and will guide you to Stand number: 4-54 Contact: Steve Santamarina successful designs. Visit our stand for competitions and specials on all Tel: 011 315-8316 | [email protected] | www.asic.co.za products listed above. ASIC Design Services distributes electronic components and electronic design automation software and offers design, consulting and training Dizzy Enterprises services. Our product lines include Microsemi (FPGAs, multi-chip Stand number: 4-38 Contact: Dane du Plooy packages (memories, processors), Mentor Graphics (PCB layout, analysis, HDL simulation, wiring harness software), HALO (magnetics), Holt (avionics Tel: 072 435-0005 | [email protected] | www.dizzy.co.za ICs), DownStream Technologies (CAM software) and XJTAG (PCB test The Proteus Design Suite is a schematic capture and PCB design equipment). -

Integrated Circuit Test Engineering Iana.Grout Integrated Circuit Test Engineering Modern Techniques

Integrated Circuit Test Engineering IanA.Grout Integrated Circuit Test Engineering Modern Techniques With 149 Figures 123 Ian A. Grout, PhD Department of Electronic and Computer Engineering University of Limerick Limerick Ireland British Library Cataloguing in Publication Data Grout, Ian Integrated circuit test engineering: modern techniques 1. Integrated circuits - Verification I. Title 621.3’81548 ISBN-10: 1846280230 Library of Congress Control Number: 2005929631 ISBN-10: 1-84628-023-0 e-ISBN: 1-84628-173-3 Printed on acid-free paper ISBN-13: 978-1-84628-023-8 © Springer-Verlag London Limited 2006 HSPICE® is the registered trademark of Synopsys, Inc., 700 East Middlefield Road, Mountain View, CA 94043, U.S.A. http://www.synopsys.com/home.html MATLAB® is the registered trademark of The MathWorks, Inc., 3 Apple Hill Drive Natick, MA 01760- 2098, U.S.A. http://www.mathworks.com Verifault-XL®, Verilog® and PSpice® are registered trademarks of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134, U.S.A. http://www.cadence.com/index.aspx T-Spice™ is the trademark of Tanner Research, Inc., 2650 East Foothill Blvd. Pasadena, CA 91107, U.S.A. http://www.tanner.com/ Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency.