3.3 Volt Electronic Fuse

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Application Note

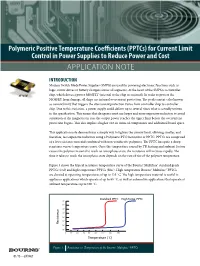

Polymeric Positive Temperature Coefficients (PPTCs) for Current Limit Control in Power Supplies to Reduce Power and Cost APPLICATION NOTE INTRODUCTION Modern Switch Mode Power Supplies (SMPS) are used for powering electronic functions such as logic, motor drives or battery chargers across all segments. At the heart of the SMPS is a controller MF-MSMF chip, which drives a power MOSFET (internal to the chip or external). In order to protect the MOSFET from damage, all chips use internal overcurrent protection. The peak current (also known as current limit) that triggers the overcurrent protection varies from controller chip to controller chip. Due to this variation, a power supply could deliver up to several times what is actually written in the specification. This means that designers must use larger and more expensive inductors to avoid saturation of the magnetics in case the output power reaches the upper limit before the overcurrent protection begins. This also implies a higher cost in terms of components and additional board space. This application note demonstrates a simple way to tighten the current limit, allowing smaller, and therefore, less expensive inductors using a Polymeric PTC thermistor or PPTC. PPTCs are comprised of a low resistance material combined with non-conductive polymers. The PPTC has quite a sharp resistance versus temperature curve. Once the temperature caused by I²R heating and ambient factors causes the polymer material to reach an amorphous state, the resistance will increase rapidly. The time it takes to reach the amorphous state depends on the rate of rise of the polymer temperature. Figure 1 shows the typical resistance temperature curve of the Bourns® Multifuse® standard grade PPTCs (red) and high temperature PPTCs (blue). -

Andover Continuumtm Family of Security Products

Andover ContinuumTM Family of Security Products TAC goes well beyond traditional security systems with our integrated approach. By combining everything from video monitoring to access control to intrusion detection, we deliver a more complete security understanding. 02 Andover Continuum Family of Security Products Features Powerful System-Wide Control From Workstations or the Web – Andover Continuum gives you a single view of all your security systems, through user- friendly workstations or over secure web links. For example, you can create reports for any event, with details down to the exact access point, so you can troubleshoot security breaches more effectively, or recognize and correct faulty equipment more rapidly. You can also connect security systems with personnel information, so you know exactly who accessed what areas and when. With a single picture of security, and one view of all systems, you can monitor, control and secure your facilities like never before: • Access Control – protect every access point in PRODUct AT A GLANCE your building • Intrusion Detection – detect early, respond rapidly • Powerful interfaces for graphics, schedules, • Digital Video Management – the latest trends, reports, alarms, personnel, technology, seamlessly integrated programming and more • Monitor live and recorded video from a Respond Immediately to New Threats Digital Video Management System In today’s world, the security risk at a site may • Import and synchronize personnel records change in an instance. TAC has designed Andover from HR databases with ease using LDAP or Continuum to act swiftly in the event of heightened CSV files risk. We have added features such as “Area Lockdown” and “Conditional Level-Based Access • Battery backed storage for up to 480,000 Rights” to provide the most secure environment personnel records in times of elevated threats. -

Failure Precursors for Polymer Resettable Fuses Shunfeng Cheng, Student Member, IEEE,Kwoktom,Member, IEEE, and Michael Pecht, Fellow, IEEE

374 IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY, VOL. 10, NO. 3, SEPTEMBER 2010 Failure Precursors for Polymer Resettable Fuses Shunfeng Cheng, Student Member, IEEE,KwokTom,Member, IEEE, and Michael Pecht, Fellow, IEEE Abstract—Resettable fuses have been widely used in overcur- product from an expected normal operating condition (i.e., a rent or overtemperature circuit protection designs in computers, “healthy” system) as well as assessment of the future reliability automotive circuits, telecommunications equipment, and medical of the product based on current and historic conditions [6]. devices. Abnormal behavior of a resettable fuse can damage a circuit. This paper identifies and experimentally assesses the PHM can provide advance warning of failures; reduce the failure precursor parameters of a polymer positive temperature life cycle cost of a product by decreasing inspection costs, coefficient resettable fuse. It is shown that the degradation of the downtime, and inventory; and assist in the design and logistical resettable fuse can be monitored, detected, and predicted based on support of fielded and future products [2]. the monitoring of these precursor parameters. No prior studies have reported on the in situ monitoring Index Terms—Failure modes, mechanisms, and effects analy- and prognostics of failures of PPTC resettable fuses in ac- sis (FMMEA), failure precursors, polymer positive temperature tual applications. In this paper, the potential failure precursor coefficient (PPTC), prognostics and health management (PHM), parameters, which are indicative of an impending failure [1], resettable fuse, trip. are identified by a systematic method: failure modes, mecha- nisms, and effects analysis (FMMEA). A series of experimental I. INTRODUCTION tests is conducted to verify the precursors. -

Are You Safe with Drones in the Sky? Designing Reliable Drones Using Proper Circuit Protection

Application Note: Designing Reliable Drones using Proper Circuit Protection Are you safe with Drones in the sky? Designing Reliable Drones using Proper Circuit Protection A drone filming a Pamplona-style “running of the bulls” at Virginia Motorsports Park suddenly dips into the crowd below, injuring spectators... a 15kg. camera drone drops out of the sky during a ski race in Italy, narrowly missing Austrian Marcel Hirscher before smashing into the slope behind him... a rogue drone smashes through a fifth-story office window in Cape Town, South Africa, striking unsuspecting race car driver David Perel in the head... a drone narrowly misses colliding with an Airbus A320 as it takes off from London’s Heathrow airport… a drone hits the Seattle Great Wheel - believed to be the largest Ferris wheel of its kind on the West Coast, standing 175 feet tall - near downtown Seattle’s waterfront, crashing into a nearby pier and prompting a police response. Introduction/Overview No doubt “pilot losing control” is behind many drone growth looks even more rapid, with the Federal Aviation incidents and crashes. But what’s behind that “loss of Administration predicting that sales will grow from control?” After all, even small recreational drones depend roughly 2.5 million this year to 7 million by 2020, with on a host of subsystems – GPS, receiver antennae, WiFi 4.3 million being sold to hobbyists and 2.7 million units I/O ports and electronic speed controllers – to stay in the being sold for professional and commercial applications. air. Lose one and that UAV becomes a UFO pretty quickly. -

ON Semiconductor Is

ON Semiconductor Is Now To learn more about onsemi™, please visit our website at www.onsemi.com onsemi and and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba “onsemi” or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided “as-is” and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. “Typical” parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. -

WO 2012/080996 Al 21 June 2012 (21.06.2012) P O P C T

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT) (19) World Intellectual Property Organization International Bureau (10) International Publication Number (43) International Publication Date WO 2012/080996 Al 21 June 2012 (21.06.2012) P O P C T (51) International Patent Classification: (72) Inventors; and H01M 2/20 (2006.01) H01M 10/052 (2010.01) (75) Inventors/Applicants (for US only): TRACEY, James H01M 10/44 (2006.01) H01R 11/24 (2006.01) [IE/IE]; 8 Sandy Lane, Ballymoney, Gorey, County Wex H01M 10/46 (2006.0 1) H01M 4/58 (20 10.0 1) ford (IE). MAGUIRE, Damien [IE/IE]; 26 Burnaby Court, Greystones, County Wicklow (IE). O'DONOVAN, (21) International Application Number: John [IE/IE]; Siochain, Kilmurray, Gorey, County Wex PCT/IE201 1/000066 ford (IE). (22) International Filing Date: (74) Agents: O'BRIEN, John, A. et al; c/o John A. O'Brien & 14 December 201 1 (14. 12.201 1) Associates, Third Floor, Duncairn House, 14 Carysfort Av (25) Filing Language: English enue, Blackrock, County Dublin (IE). (26) Publication Language: English (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, (30) Priority Data: AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, 2010/0785 16 December 2010 (16. 12.2010) IE CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, (71) Applicant (for all designated States except US) : JTM DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, POWER LIMITED [IE/IE]; 20 Village Mill, Enterprise HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, Park, Rathnew, Country Wicklow (IE). -

Introduction to Automotive Ignition Systems

Introduction to Automotive Ignition Systems Authors: Jose Padilla, Product Marketing Manager, Ignition Devices Philippe di Fulvio, Automotive Field Application Engineer Charlie Cai, Product Marketing Manager, TVS Diodes Introduction to Automotive Ignition Systems 2 Electric passenger vehicles are still in a nascent phase of development. Currently, only 1% (550,000 vehicles) of the world’s cars use electric power. The reasons for such low and slow market penetration is due to the short range of the batteries, the lower price of the electric vehicles for the same power, and/or the scarce number of models available in the market. Also, the electric grid infrastructure essential to serve this application is incomplete and the number of charging poles unable to support a large electric vehicle fleet. This is why the US Department of Energy estimates that 82% of all new vehicles will continue to run on fossil fuel for the foreseeable future. Subsequently, in order to reduce the environmental impact of cars we must focus on making gas-fueled vehicles “greener”. In other words, we need to optimize the efficiency of the engine. A good design of the vehicle’s electronic ignition system offers the best way to guarantee a controlled, safe, and optimal combustion. The Inductor Discharge Ignition System (IDI) To understand a vehicle’s electronic ignition system, we created a simplified ignition system diagram below along with a detailed explanation of the IDI system: Figure 1. The Inductive Discharge Ignition system Littelfuse, Inc. Contact Littelfuse 8755 West Higgins Road, Suite 500 www.littelfuse.com • Phone: +1 773-628-1000 Chicago, Illinois 60631 Contact Littelfuse Introduction to Automotive Ignition Systems 3 Before we discuss the IDI in detail, remember that the spark event in the combustion chamber of the gasoline engine is controlled by the ignition system. -

Hlapplication Note

HL application note Dr. Alfons Graf Siemens AG, HL PS TM Hannes Estl Siemens AG, HL PS TM2 Fuse Function with PROFET Highside Power Switches Abstract: The protection functions originally incorporated in smart power switches for self-protection have become so sophisticated that they are now capable of protecting not only themselves but also the connected load including leads and plug-in contacts. Although in the past this was primarily the task of fuses, the reduction in the number of fuses in new vehicle generations from approx. 80 to the present 40 is evidence of the trend towards replacing fuses by semiconductors. This article shows how correct dimensioning and placement of smart power switches not only enables fuses to be replaced but can also significantly improve protection behavior. In the case of thermal operation of the protection functions, for example, a similar but in some applications more favorable behavior can be achieved than with the current vehicle fuse, whereas active current sensing allows virtually any fuse behavior to be implemented. We then examine the various influencing factors such as manufacturing variations or temperature, but also the magnitude of the operating voltage which is important particularly for the new 42V electrical system. Finally, the unlikely event of destruction of the semiconductor and the associated failure of the protection function will be analyzed in greater detail. Correct dimensioning for lamp or motor load switching will be clarified with the aid of a number of practical examples. HL PS -

Ctg Product List

Product List Crestwood Technology Group 914.779.3500 | [email protected] CTGNOW.com Any part, any platform, we can help. Here is a quick overview of parts and material we provide. Expendables Rotables ATA Chapters Actives INTEGRATED CIRCUITS Batteries Actuators ATA Chapters AC to DC Switching Converters Bonding Leads Air Regulators Accessory Gearboxes Analog Cable Assemblies APUs Air Analog – Digital Converter Connectors Ballast Units Air Conditioning Angular and linear Position Sensors Contacts Boroscopes Airborn Auxiliary Power Appdlication Processor and SOC Fans Cargo Liners Auto Flight Audio Processor Fasteners Cargo Nets Central Maintenance System Controllers Filters Cargo Panels Communications Converters Hardware Cockpit Avionics Doors CPLD Inductors Composites Electrical Power CPUs Lamps/LEDs Compressors Engine Controls Current miters Placards/Decals Disks Engine Exhaust Current Mode PWM Controller Relays Displays Engine Fuel and Control Current Sensor Tape Doors Engine Indicating DC to DC Controller Drive-Shafts Engine Oil Digital Elevator Assemblies Equipment / Furnishings Consumables Digital – Analog Converter Engine Components Fire Protection D-RAM Engines Flight Controls Adhesives, Tapes & Sealants DSP Evacuation Slides and Life Fuel Solvents EE-PROM Rafts Fuselage Composite Materials EPROM Fire Extinguishers Hardware Shop Supplies FPGA Flap Carriages Helicopter Vibration Oils, Greases & Lubricants Hall Effect Sensor Fuel Pumps Hydraulic Power Paints & Coatings Hot Swap Controller Gear Box Ice and Rain Protection Industrial -

Encyclopedia of Electronic Components Volume 1

Encyclopedia of Electronic Components Volume 1 Charles Platt Encyclopedia of Electronic Components Volume 1 by Charles Platt Copyright © 2013 Helpful Corporation. All rights reserved. Printed in the United States of America. Published by O’Reilly Media, Inc., 1005 Gravenstein Highway North, Sebastopol, CA 95472. O’Reilly books may be purchased for educational, business, or sales promotional use. Online editions are also available for most titles (http://my.safaribooksonline.com). For more information, contact our corporate/institu- tional sales department: 800-998-9938 or [email protected]. Editor: Brian Jepson Cover Designer: Mark Paglietti Production Editor: Melanie Yarbrough Interior Designer: Edie Freedman and Nellie McKes- Proofreader: Melanie Yarbrough son Indexer: Judy McConville Illustrator: Charles Platt Photographer: Charles Platt Cover Production: Randy Comer October 2012: First Edition Revision History for the First Edition: 2012-10-03 First release See http://oreilly.com/catalog/errata.csp?isbn=9781449333898 for release details. Nutshell Handbook, the Nutshell Handbook logo, and the O’Reilly logo are registered trademarks of O’Reilly Media, Inc. Encyclopedia of Electronic Components Volume 1, the cover images, and related trade dress are trademarks of O’Reilly Media, Inc. Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trade- marks. Where those designations appear in this book, and O’Reilly Media, Inc., was aware of a trademark claim, the designations have been printed in caps or initial caps. While every precaution has been taken in the preparation of this book, the publisher and authors assume no responsibility for errors or omissions, or for damages resulting from the use of the information contained herein. -

Offline Non-Isolated Flyback Converter Protection WHITE PAPER

Offline Non-Isolated Flyback Converter Protection WHITE PAPER ABSTRACT This paper examines the use of resettable polymer fuses for protecting offline flyback converters. Using a thermal model of the resettable fuse surrounding solder pads and copper to optimize the Multifuse® Polymer PTC trip time so that the converter is protected during overloads, there are two potential positions Resettable Fuses considered for polymer Positive Temperature Coefficient (PTC) resettable fuses in the circuit. One position is directly on the winding and the other position is beyond the control loop. Results are taken from the converter and compared with a simulation. Figure 1. Photograph of Converter 5/16 • e/MF1602 Offline Non-Isolated Flyback Converter Protection White Paper INTRODUCTION L1 C1 R1 Multifuse® Polymer PTC D6 D3 Resettable Fuses C3 C4 D1 90-275 Vac D2 MF-MSMF075 UCC28880 TX1 5 Vdc D5 D4 P1 S1 0.5 A C2 R2 U1 SM91047EL C5 R3 C6 Figure 2. Circuit Diagram of Offline Non-Isolated Flyback Converter Polymer PTC resettable fuses are used for protecting circuits from overloads, albeit with the following drawbacks: 1. Difference between rated hold current and trip current. Typically, the trip current is twice the hold current with trip times of greater than ten seconds. This paper shows how the trip time can be reduced significantly. 2. Sensitivity to ambient temperature, leading to significant derating. The resistance of a resettable fuse at 100 °C can be 220 % of its nominal value at 25 °C. However, high temperature polymer PTCs, are now available and exhibit an increase of 150 % of their resistance which is comparable to typical high power MOSFETs at 100 °C as shown in figure 2. -

NIS5132 Series +12 Volt Electronic Fuse

NIS5132 Series +12 Volt Electronic Fuse The NIS5132 is a cost effective, resettable fuse which can greatly enhance the reliability of a hard drive or other circuit from both catastrophic and shutdown failures. It is designed to buffer the load device from excessive input voltage which can damage sensitive circuits. It also includes an overvoltage http://onsemi.com clamp circuit that limits the output voltage during transients but does not shut the unit down, thereby allowing the load circuit to continue 3.6 AMP, 12 VOLT operation. Two thermal options are available, latching and auto−retry. ELECTRONIC FUSE Features • Integrated Power Device • Power Device Thermally Protected • No External Current Shunt Required DFN10 • 9 V to 18 V Input Range CASE 485C • 44 mW Typical • Internal Charge Pump MARKING DIAGRAM • Internal Undervoltage Lockout Circuit • Internal Overvoltage Clamp (MN1 and MN2 versions) 1 Pin Function 32 1 GND • G ESD Ratings: Human Body Model (HBM); 2000 V AYW 2 dv/dt G Machine Model (MM); 200 V 3 Enable/Fault • These Devices are Pb−Free and are RoHS Compliant 4 ILIMIT 5NC Typical Applications 6−10 SOURCE 11 (flag) VCC • Hard Drives • Mother Board Power Management 32 = Latching Version with VClamp 32B = Latching Version without VClamp 32H = Auto−Retry Version with VClamp A = Assembly Location Y = Year W = Work Week G = Pb−Free Package (Note: Microdot may be in either location) ORDERING INFORMATION See detailed ordering and shipping information in the ordering information section on page 10 of this data sheet. © Semiconductor Components Industries, LLC, 2014 1 Publication Order Number: July, 2014 − Rev.