Power Macintosh 5400 Computer Developer Note

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Power Macintosh 5400 Technical Information 1996.Pdf

Specificalions for Power Macintosh 5400 series computers Technical Information Main unit Processor A PowerPC™ 603e processor with the following features: • 180 megahertz (MHz) processor clock • built-in floating point unit (FPU) • 40 MHz system bus • 32 kilobytes (K) internal cache ( 16K data, 16K instruction) Memory • 16 megabytes (MB) of dynamic random-access memory (DRAM), expandable to a maximum of 136 MB in two sockets. The main logic board has 8 MB of DRAM soldered to it, and an 8 MB DRAM DIMM is installed in one of the sockets. DRAM DIMMs installed later should be 64-bit wide, 168-pin fast-paged mode, with 70-nanosecond (ns) RAM access time or faster. • I MB of built-in video RAM • 4 MB of read-only memory (ROM) • 8K of nonvolatile parameter memory • One socket for an optional High Performance Module (256K Level 2 Cache) Internal disk drives The following drives were installed in your computer at the factory: • Apple SuperDrive 1.4 MB high-density floppy disk drive • Apple ATA (AT Attachment) hard disk drive, also known as an Integrated Device Electronics (IDE) hard disk drive • Tray-loading CD-ROM drive (5.25-inch, 1/2-height 8x-speed). Video Graphic modes supported Your Power Macintosh 5400 series computer can display the graphic modes listed in the following table. In addition, your computer can display video input in some modes. Resolution Color depth Vertical scan rate · Video lop~ supp,orted 640 x 480 16-bit 60 Hz and 67 Hz yes 800 x 600 16-bit 60 Hz yes, 8-bit or less color depth 800 x 600 8-bit 72 Hz no 832 x 624 8-bit 75 Hz yes Video output With the optional Apple External Video Connector kit, your computer can be connected to an Apple Video Presentation System or a liquid crystal display (LCD) panel. -

Peterson Taken Into Custody Student Concern: by CATHERINE Hopkr:\'SON and Rodney Square

An Associated Collegiate Press Four-Star All-American Newspaper FRIDAY • • November 22, 1996 THE Volume 123 Number 22 on-Profit Org. U.S. Postage Paid ewark, DE Penni! o. 26 250 Student Center· University of Delaware·Newark, DE 19716 Peterson taken into custody Student concern: BY CATHERINE HOPKr:\'SON AND Rodney Square. FBI agents pushed A GELA ANDRIOLA through a crowd of reporters and Cirr \c,,·., Etliton cameramen. Several onlookers shouted WILMI GTO Brian C. ·'baby killer·· at the accused. from Peterson. accu~ed in the murder of a Peterson was arraigned at 2 p.m. in university student"' baby. turned Magistrate Court 18 at Gander Hill himself in to the FBI yesterday morning Prison in Wilmington. He is being held He had been considered a fugitive without bail. DUSC since Tuesday. Peter~on and freshman Peterson was not required to enter a Amy S. Grossberg face first-degree plea. but Hurley said hi s client will murder charges and pos~ibly the death plead not guilty if the case goes to trial. penalty for allegedly leaving However. Hurley admitted. ''If he dawn Gro ssbe rg's were guilty. he would plead not guilty. till newborn baby in Everybody pleads not guilty. a trash bin ··we take the position that he did not oubide the murder.·· Hurley said. "He's not Delaware student Comfort Inn innocent. He did something wrong but shortly after the we· re not sure what he did wrong:· government has baby' s deli very Hurley would not comment on the on ov. II. facts of the case or possible defense power, needs help The child died strategies, but ;,uggested there was a of ··s kull "strong probability . -

![[Open-E.P.U.B PDF] Power Mac 5400 Manual](https://docslib.b-cdn.net/cover/9089/open-e-p-u-b-pdf-power-mac-5400-manual-999089.webp)

[Open-E.P.U.B PDF] Power Mac 5400 Manual

Power Mac 5400 Manual Download Power Mac 5400 Manual Use as the Power Off Timer setting. 7. Click Send. 8. Select the time period you want before the product goes to sleep as the Sleep Timer setting. 9. Click Send. 10. Click OK to close the open program windows. Parent topic: The Power Off and Sleep Timers Changing the Power Off and Sleep Timer Settings - Mac 5400.7) (Reference (c)). They are processed in accordance with DoD 5400.7-R (Reference (d)). • Requests for information from systems of records controlled by the Office of Personnel Management (OPM), although maintained by a DoD Component. These are processed in accordance with policies established by OPM (Reference (e)). Mac of the Day: Power Mac G5 Quad, introduced 2005.10.19.With two 2.5 GHz dual-core G5 CPUs, the G5 Quad was the most powerful PowerPC Mac ever and introduced PCI Express Apple Macintosh Service Manuals PowerBook G3 G4 ColorSync AirPort. Power Macintosh 5400-120 Power Macintosh 5400-160 Power Macintosh 5400-180. Power your analytics with storage optimized for mass capacity. Momentus 7200 FDE.1 SATA Product Manual; Momentus 5400 FDE.4 SATA Product Manual;. 5400.6: 5400.6.The 233 and 266 MHz desktop models shipped with 4 GB hard drives, and the 300 MHz with a 6 GB drive, all at 5400 RPM. This model, sometimes referred to as. Of Apple Computer, Inc. Finder, Power Mac, iMac, and iBook are trademarks of Apple. Manual or the other documentation provided with your Nikon product are. Thank you for your purchase of a Nikon COOLPIX5400 digital camera. -

PC Compatibility Cards

K Service Source PC Compatibility Cards 7" 100 MHz Card, 12" 100 MHz Card, 12" 166-P Card, and 12" PR166 Card K Service Source Basics PC Compatibility Cards Basics Overview - 1 Overview The PC compatibility cards are for use with Power Macintosh models having peripheral component interface (PCI) expansion slots. They allow MS-DOS and Windows applications to run directly on a Power Macintosh computer. There are several types of Apple PC Compatibility cards, and installation procedures differ for each: • 12-inch 100 MHz card: features a 100-MHz Pentium processor • 7-inch 100-MHz card: features a 100 MHz 5x86 processor • 12-inch 166 MHz-P card: features a 166 MHz Pentium processor • 12-inch PR166 card: features a 166 performance rated (PR) 6x86 processor Basics Overview - 2 With each of these cards, the PowerPC processor operates independently of the processor on the PC Compatibility Card so that Macintosh and MS-DOS or Windows applications can run concurrently. Basics General Compatibility Information - 3 General Compatibility Information The original 100 MHz PC compatibility cards (7-inch and 12-inch) are compatible with the following software and equipment: • Microsoft MS-DOS 6.22 • Windows 3.1 • Windows for Workgroups 3.11 • Windows 95 (not compatible with WindowNT or OS/2) • Sound Blaster-16 • Apple displays • Most third-party VGA and SVGA displays • Power Macintosh 5400, 6400 (7-inch card only), 7200, 7500, 7600, 8500, and 9500 series computers Basics General Compatibility Information - 4 The 166 MHz-P and PR166 cards are compatible with the following software and equipment: • Microsoft MS-DOS 6.22 • Windows 3.1 • Windows for Workgroups 3.11 • Windows 95 (not compatible with WindowNT or OS/2) • Sound Blaster-16 • Apple displays • Most third-party VGA and SVGA displays The 166 MHz-P card is compatible with the Power Macintosh 4400, 7220, 7200, 7300, 7500, 7600, 8500, 8600, 9500, and 9600 series computers, while the PR166 card is only compatible with the Power Macintosh 4400/ 200 and 7220/200 (Far East only) computers. -

The Powerpc Macs: Model by Model

Chapter 13 The PowerPC Macs: Model by Model IN THIS CHAPTER: I The PowerPC chip I The specs for every desktop and portable PowerPC model I What the model numbers mean I Mac clones, PPCP, and the future of PowerPC In March 1994, Apple introduced a completely new breed of Mac — the Power Macintosh. After more than a decade of building Macs around the Motorola 68000, 68020, 68030, and 68040 chips, Apple shifted to a much faster, more powerful microprocessor — the PowerPC chip. From the start, Apple made it clear it was deadly serious about getting these Power Macs into the world; the prices on the original models were low, and prices on the second-generation Power Macs dropped lower still. A well- equipped Power Mac 8500, running at 180 MHz, with 32MB of RAM, a 2 GB hard drive, and a eight-speed CD-ROM drive costs about $500 less than the original Mac SE/30! When the Power Macs were first released, Apple promised that all future Mac models would be based on the PowerPC chip. Although that didn’t immediately prove to be the case — the PowerBook 500 series, the PowerBook 190, and the Quadra 630 series were among the 68040-based machines released after the Power Macs — by the fall of 1996, Macs with four-digit model numbers (PowerPC-based Power Macs, LCs, PowerBooks, and Performas) were the only computers still in production. In less than two years, 429 430 Part II: Secrets of the Machine the Power Mac line has grown to over 45 models. -

Power Macintosh 5500 and 6500 Computers

Developer Note Power Macintosh 5500 and 6500 Computers Developer Note © Apple Computer, Inc. 1997 Apple Computer, Inc. Corporation, used under license © 1997 Apple Computer, Inc. therefrom. All rights reserved. The word SRS is a registered trademark No part of this publication may be of SRS Labs, Inc. reproduced, stored in a retrieval Simultaneously published in the United system, or transmitted, in any form or States and Canada. by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of LIMITED WARRANTY ON MEDIA AND Apple Computer, Inc., except to make a REPLACEMENT backup copy of any documentation If you discover physical defects in the provided on CD-ROM. Printed in the manual or in the media on which a software United States of America. product is distributed, ADC will replace the The Apple logo is a trademark of media or manual at no charge to you Apple Computer, Inc. provided you return the item to be replaced Use of the “keyboard” Apple logo with proof of purchase to ADC. (Option-Shift-K) for commercial ALL IMPLIED WARRANTIES ON THIS purposes without the prior written MANUAL, INCLUDING IMPLIED consent of Apple may constitute WARRANTIES OF MERCHANTABILITY trademark infringement and unfair AND FITNESS FOR A PARTICULAR competition in violation of federal and PURPOSE, ARE LIMITED IN DURATION state laws. TO NINETY (90) DAYS FROM THE DATE No licenses, express or implied, are OF THE ORIGINAL RETAIL PURCHASE granted with respect to any of the OF THIS PRODUCT. technology described in this book. Even though Apple has reviewed this Apple retains all intellectual property manual, APPLE MAKES NO WARRANTY rights associated with the technology OR REPRESENTATION, EITHER EXPRESS described in this book. -

![[Rar Ebook PDF] Power Mac 5400 Manual](https://docslib.b-cdn.net/cover/5927/rar-ebook-pdf-power-mac-5400-manual-3595927.webp)

[Rar Ebook PDF] Power Mac 5400 Manual

Power Mac 5400 Manual Download Power Mac 5400 Manual Apple Macintosh Service Manuals PowerBook G3 G4 ColorSync AirPort. Power Macintosh 5400-120 Power Macintosh 5400-160 Power Macintosh 5400-180. Power Macintosh 5400 on Apple Computerin 15. Huhtikuuta 1996 julkaisema tietokone. Laite sisälsi PCI-liitännän ja Power Macintosh 6300-160:n päivitetyn emolevyn.. Euroopassa ja Aasiassa laitteesta myytiin versiota, jossa oli Applelle poikkeuksellisesti musta Press the power button to turn on your Mac. If the battery is removable: Shut down your Mac. Remove the battery. Press the power button and hold it for 5 seconds. Press the power button again to turn on your computer. How to speed up iMac, Mac Mini, Mac Pro. Shut down your computer. Unplug a power cord and wait 15 seconds. Plug the power cord in. Power Macintosh 5400 (M3046) Power Macintosh 6500-250 (M6127LL-A). StyleWriter (M8000) Power Mac 5400 User’s manual. Previous. Next. List. Scan of manual cover.Power Mac G5 Memory - 3 Figure 1 5. Unplug the power cord. 6. Hold the side access panel and lift the latch on the back of the computer. (Figure 2) Warning: The edges of the access panel and the enclosure can be sharp. Be very careful when handling them. 7. Remove the access panel and place it on a flat surface covered by a soft, clean cloth.Mcculloch Power Mac 6 Chainsaw Workshop downloadable pdf Service and Repair Manual. McCulloch 1-53 Chain Saw Service Repair Shop Manual 127p Download Now. 350 McCulloch Chainsaw PDF manuals. Add to Cart Downladable Service Manual. This is one of the more tedious chainsaws to tear down a McCulloch Mac 120. -

Power Macintosh/Performa 5000 Series

K Service Source Power Macintosh/Performa 5000 Series Power Macintosh 5400/120, 5400/180, 5400/200, 5500/225 International Performas 5400/160, 5400/180, 5420, 5420/180 K Service Source Basics Power Macintosh/Performa 5400 and 5500 Series Basics System Overview - 1 System Overview The Power Macintosh 5400/5500 computer series combines RISC-based PowerPC performance, full multimedia features, and low cost in a sleek all-in-one design. The design includes expansion slots for communications and PCI cards, as well as other video-in, video tuner, and video- out options. Disk storage includes an IDE hard drive in a variety of capacities and a trayloading CD-ROM drive. Basics Rev. B, 5000 Series - 2 Rev. B, 5000 Series Apple introduced an updated 5000 series version several months after introduction. Referred to in this manual as “Rev. B,” the updated version incorporates design changes that are not backward-compatible. Models in the 5500 series are made entirely with Rev. B parts. To determine which version you are servicing, remove the front bezel and note the location of the speakers. If the speakers are part of the front bezel, the unit is the original version. To service the original version, follow the manual for take-apart procedures and parts information, unless the procedures specify Rev. B. If the speakers are attached to the sides of the metal chassis, the unit is Rev. B. To service Rev. B models, follow the manual, substituting Rev. B procedures and parts. Basics Configurations - 3 Configurations Power Macintosh 5400/120 A configuration of the Power Macintosh 5400/120 for the Education channel includes the AppleCD 1200i 8x-speed CD-ROM drive. -

UAC Cuts Voodoo's Funding

MlT's The Weather Oldest and Large t Today: Rainy, windy, 40°F (4°C) Tonight: Clear, cold, 34°F (10C) ewspaper Tomorrow: Cloudy, 42°F (S°C) Details, Page 2 UAC Cuts Voodoo's Funding, Approves Logan Finals Shuttle By Dan McGuire The motion came as council Carter said that the amount of NEWSEDrrOR members debated whether Voodoo money given to Voodoo could be The Undergraduate Association would make good use of the money increased after discussions between Council held its last meeting of the allocated to it the VA and Voodoo staff. In the term Wednesday evening, approv- "Voodoo has not come out all meantime, the VA Executive ing an amended version of the this term," said Edward A. Gordon Committee could issue emergency Finance Board recommendations for '99, a member of Finboard. "Over funds if the need arose, Carter said. spring term funding for student half of the people on campus, fresh- activities and an airport shuttle dur- men and sophomores, have never Campu publications discussed ing finals week. seen more than two or three issues The debate over the future of After some debate, the council of Voodoo ... Voodoo can do better," Voodoo's funding evolved into a voted to approve an amended ver- he said. discussion of how much money stu- sion of the Finboard recommenda- "I think that the money that dent publications need from the VA. tions. UA Vice President Dedric A. we're giving them is keeping Voodoo, along with Carter '98 made a motion to give [Voodoo] from dying when it should Counterpoint and The Thistle, are at Voodoo $1,600 for the spring term die. -

Crescendo/L2 G3 Manual

Installation Manual Installation Manual Crescendo™/L2 Processor Upgrade Cards © 2000 Sonnet Technologies, Inc. All rights reserved. Sonnet Technologies, Inc. 15 Whatney Irvine, California 92618-2808 USA Sales: 1-949-587-3500 Fax: 1-949-457-6350 Customer Service: 1-949-472-2772 (Monday–Friday, 8 am–5 pm Pacific Time) Customer Service E-mail: [email protected] Domestic Sales E-mail: [email protected] Website: www.sonnettech.com Sonnet, the Sonnet logotype, Simply Fast, the Simply Fast logotype, and Crescendo are trademarks of Sonnet Technologies, Inc. Macintosh, Mac and the Mac logo are trademarks of Apple Computer, Inc., registered in the U.S. and other countries. The PowerPC name and the PowerPC logotype are trademarks of International Business Machines Corporation, used under license therefrom. Motorola is a registered trademark of Motorola, Inc. Other product names are trademarks of their respective owners. Product specifications are subject to change without notice. This manual may not be copied, in whole or in part, without the written consent of Sonnet Technologies, Inc. Your rights to software distributed by Sonnet is governed by its accompanying software license agreement. Sonnet has made every effort to ensure the accuracy of this manual. Product specifications are subject to change without notice. Manual Number: Z-BG3-MNL-E Release: v 1.0 Printed in the U.S.A. Contents Preface iv Before You Get Started v 1 Power Macintosh 4400 and 7220 Installation 1 2 Power Macintosh 5400, 5500, and 9 Performa 54XX Installation 3 Power -

Technology Plan 2011-2016-Finalxxx

Valley Center-Pauma Unified School District Technology Plan 2011-16 VALLEY CENTER–PAUMA UNIFIED SCHOOL DISTRICT FIVE-YEAR TECHNOLOGY PLAN 2011-2016 CDS CODE # 37-75614 Contact: Jon Goodman, Director of Learning & Information Services or Olivia Leschick, Administrator in Charge Of Special Projects Valley Center-Pauma Unified School District 28751 Cole Grade Road Valley Center, CA 92082 (760) 749-0464 FAX (760) 749-1208 [email protected] [email protected] 1 Valley Center-Pauma Unified School District Technology Plan 2011-16 TABLE OF CONTENTS 1. Plan Duration……………………………………………………………………………………....4 2. Stakeholders………………………………………………………………………………………..4 3. Curriculum………………………………………………………………………………………....5 • 3a Description of current teachers and students access to technology tools both during the day and outside school hours…………………………………………………………...........5 • 3b Description of VCPUSD current use of hardware & software to support teaching/learning……………………………………………………………………………..7 • 3c Summary of VCPUSD curricular goals supported in this plan…………………………...8 • 3d Clear goals, measurable objectives, annual benchmarks & implementation plan for using technology to improve teaching & learning by supporting VCUSD curricular goals…………………………………………………………………………………………..9 • 3e Goals, measurable objectives, annual benchmarks & implementation plan for how and when students will acquire technology & information literacy skills needed to succeed in the classroom and the workplace………………………………………………………………..11 • 3f Goals, & an implementation plan that describes -

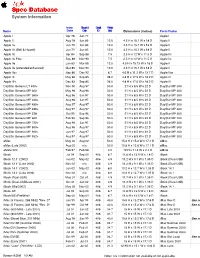

System Information

System Information Intro. Discont' d Gestalt Weight Name Date Date ID (lbs.) Dimensions (inches) Form Factor Apple I Apr 76 Jan 77 Apple I Apple II Aug 78 Jun 83 12.0 4.5 H x 15.1 W x 18 D Apple II Apple II+ Jun 79 Jun 83 12.0 4.5 H x 15.1 W x 18 D Apple II Apple II+ (Bell & Howell) Jun 79 Jun 83 12.0 4.5 H x 15.1 W x 18 D Apple II Apple IIc Apr 84 Sep 88 7.5 2.5 H x 12 W x 11.5 D Apple IIc Apple IIc Plus Sep 88 Nov 90 7.5 2.5 H x 12 W x 11.5 D Apple IIc Apple IIe Jan 83 Mar 85 12.0 4.5 H x 15.13 W x 18 D Apple II Apple IIe (extended/enhanced) Mar 85 Nov 93 12.0 4.5 H x 15.1 W x 18 D Apple II Apple IIgs Sep 86 Dec 92 8.7 4.6 H x 11.2 W x 13.7 D Apple IIgs Apple III May 80 Sep 85 26.0 4.8 H x 17.5 W x 18.2 D Apple III Apple III+ Dec 83 Sep 85 26.0 4.8 H x 17.5 W x 18.2 D Apple III DayStar Genesis LT 400+ Nov 96 Aug 97 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 300 May 96 Aug 96 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 360+ Aug 96 Jan 97 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 400+ Aug 96 Jan 97 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 450+ Aug 97 Aug 97 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 466+ Aug 97 Aug 97 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 528 Oct 95 Sep 96 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 600 Feb 96 Sep 96 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 720+ Aug 96 Jan 97 50.0 21 H x 8.5 W x 22 D DayStar MP 300 DayStar Genesis MP 800+ Aug 96 Aug 97 50.0 21 H x 8.5 W x 22 D DayStar