SCH3221 Data Sheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

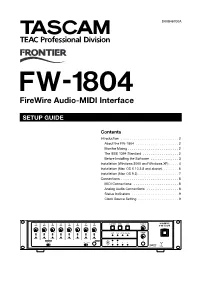

FW-1804 Firewire Audio-MIDI Interface

» D00846700A FW-1804 FireWire Audio-MIDI Interface SETUP GUIDE Contents Introduction ...............................2 About the FW-1804 .......................2 Monitor Mixing ...........................2 The IEEE 1394 Standard ...................2 Before Installing the Software ...............3 Installation (Windows 2000 and Windows XP) .....4 Installation (Mac OS X 10.2.8 and above).........6 Installation (Mac OS 9.2)......................7 Connections ...............................8 MIDI Connections ........................8 Analog Audio Connections .................8 Status Indicators .........................9 Clock Source Setting ......................9 Introduction About the FW-1804 • COMPUTER selects the signals from the DAW passed through the FireWire connection. The level of the signals from the computer is set using the master output control The FW-1804 provides your computer with high-quality of the DAW software and the two analog outputs may be audio facilities: eight channels of analog input and two of selected (using the software Control Panel) for output of output, with two channels of digital audio I/O through these signals. coaxial connections and eight channels of digital I/O through optical connections—at up to 96 kHz 24-bit. There • INPUTS selects the stereo mix of the analog, optical and are also two physical MIDI input and four physical output coaxial signals for monitoring. ports. • BOTH allows the computer signals to be monitored It is connected to the host computer using a single 6-pin to mixed with the input signals. 6-pin IEEE 1394 cable (supplied) that carries audio and Individual channels can be set to unity gain by pressing and MIDI information back and forth between the FW-1804 holding the computer's [Shift] key while clicking on the and the computer. -

Tms320dm643x DMP Peripherals Overview Reference Guide (Rev. A

TMS320DM643x DMP Peripherals Overview Reference Guide Literature Number: SPRU983A June 2007 2 SPRU983A–June 2007 Submit Documentation Feedback Contents Preface ............................................................................................................................... 4 1 Overview.................................................................................................................... 5 2 Asynchronous External Memory Interface (EMIF)............................................................ 6 3 DDR2 Memory Controller ............................................................................................. 6 4 DSP Megamodule Internal Direct Memory Access (IDMA) Controller ................................. 7 5 DSP Megamodule Interrupt Controller (INTC) ................................................................. 7 6 DSP Megamodule Power-Down Controller (PDC) ............................................................ 8 7 Enhanced Direct Memory Access (EDMA) Controller....................................................... 8 8 Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) Module....................................................................................................................... 8 9 General-Purpose Input/Output (GPIO)............................................................................ 8 10 High-End CAN Controller (HECC).................................................................................. 9 11 Host Port Interface (HPI) ............................................................................................. -

United States Patent (19) 11 Patent Number: 6,157,976 Tien Et Al

USOO6157976A United States Patent (19) 11 Patent Number: 6,157,976 Tien et al. (45) Date of Patent: Dec. 5, 2000 54 PCI-PCI BRIDGE AND PCI-BUS AUDIO OTHER PUBLICATIONS ACCELERATOR INTEGRATED CIRCUIT PCI System Architecture, Tom Shanley/Don Anderson, 75 Inventors: Paul Tien, Fremont; Cheng-Yeuan 1995, pp. 381-382. Tsay, Pleasanton; Rsong-Hsiang Shiao, Fremont, all of Calif. Primary Examiner Ayaz R. Sheikh Assistant Examiner Rupal D. Dharia 73 Assignee: ESS Technology, Fremont, Calif. Attorney, Agent, or Firm-Gray Cary Ware & Freidenrich 57 ABSTRACT 21 Appl. No.: 09/074,657 A semiconductor device with an embedded PCI 2.1 com 22 Filed: May 6, 1998 pliant bridge provides expanded functionality as System 51511 Int. Cl. ............................. GO6F13FOO700; GO6F 13/38/ level implementationsp of a PCI-to-PCI bridge,9. and enhances 52 U.S. Cl. ............................ 710/129, 710/127, 710/64; the level of integration possible. The embedded PCI-to-PCI 345/435; 84/604; 84/621; 84/622; 84/647 bridge allows the creation of multi-function, multimedia 58) Field of Search 345/435: 710/127 add-on cards Supporting multiple devices. Multi-function, 710129,6484/602,604 621 622 647. multimedia Subsystems that provide audio, graphics, MPEG, s w is s s 454. 70425s etc., are mapped into a bridged-to PCI-bus that keeps Such s traffic off the main PCI-bus. The advantage for the system or 56) References Cited add-in card Vendor is that the various multimedia chips that are combined can come from different Sources, providing an U.S. PATENT DOCUMENTS optimized and highly customized combination of functions. -

Profire Lightbridge User Guide | 2 Introduction 1

34-in/36-out FireWire Lightpipe Interface User Guide English Table of Contents English . 2 Introduction . 2 What’s in the Box . 2 About ProFire Lightbridge . 3 ProFire Lightbridge Features . 4 System Requirements . 5 Controls and Connectors . 6 Front Panel . 6 Rear Panel . 7 Driver Installation . 8 Hardware Connections . 8 Audio . 8 MIDI . 9 Word Clock . 9 Using ProFire Lightbridge . 9 The Software Control Panel . 10 Hardware Page . 10 About Page . 13 Word Clock Synchronization . 14 Understanding Word Clock . 14 Specifications . 18 Warranty . 19 Warranty Terms . 19 Warranty Registration . 19 M-Audio ProFire Lightbridge User Guide | 2 Introduction 1 hank you for purchasing M-Audio’s ProFire Lightbridge interface. ProFire Lightbridge uses the ADAT optical T I/O standard to bring extensive digital connectivity to your studio. With its four ADAT optical inputs, four ADAT optical outputs, S/PDIF coaxial input and output, and stereo analog outputs, ProFire Lightbridge lets you connect a variety of devices to your FireWire-equipped digital audio workstation. Using the high-bandwidth, industry-standard FireWire (IEEE1394) protocol, ProFire Lightbridge gives your DAW up to 34 audio inputs and 36 outputs while connecting to your computer via a single cable. This makes it perfect for multi-channel transfers to and from external multitrack recorders. ProFire Lightbridge is also ideal for linking your DAW to an external digital mixer, or for connecting to another computer hosting soft synths and signal processors. This manual will explain the features and operation of ProFire Lightbridge. Even if you are an experienced recording enthusiast, please take a moment to read this guide and familiarize yourself with all of the unique features of your ProFire Lightbridge. -

US-16X08 Reference Manual

D01247020B US-16x08USB2.0 Audio Interface/Mic Preamp Reference Manual Before connecting this unit to a computer, you must download and install a dedicated driver. Contents 1 – Introduction ..............................................3 Windows 8 ....................................................................23 Features ..................................................................................3 Windows 7 ....................................................................23 Conventions used in this manual ..................................3 Mac OS X and iTunes ........................................................24 iOS ..........................................................................................24 2 – Names and functions of parts ..................4 Front panel ............................................................................4 9 – MIDI Implementation Chart ...................25 Rear panel ..............................................................................5 10 – Troubleshooting ...................................26 3 – Installation ................................................6 Troubleshooting ................................................................26 System requirements.........................................................6 11 – Specifications ........................................28 Windows ..........................................................................6 Specifications .....................................................................28 Mac OS X..........................................................................6 -

3.4.1 SPI - Serial Peripheral Interface

DIPLOMARBEIT Herr Axel Schneider Entwicklung einer updatefähigen Embedded-Linux-Hardwareplattform zum Einsatz in einer speziellen Gerätesteuerung Mittweida, 2012 Fakultät Elektro- und Informationstechnik DIPLOMARBEIT Entwicklung einer updatefähigen Embedded-Linux-Hardwareplattform zum Einsatz in einer speziellen Gerätesteuerung Autor: Herr Axel Schneider Studiengang: Elektrotechnik Schwerpunkt Energiesystemtechnik Seminargruppe: ET07wE-D Erstprüfer: Prof. Dr.-Ing. Thomas Beierlein Zweitprüfer: Dipl.-Ing. (FH) Jan Färber Einreichung: Mittweida, 17.08.2012 Bibliografische Angaben: Schneider, Axel: Entwicklung einer updatefähigen Embedded-Linux-Hardwareplatt- form für den Einsatz in einer speziellen Gerätesteuerung - 2012 – 74 Seiten, 43 Abbildungen, 13 Tabellen, 3 Anlagen , Mittweida, Hochschule Mittweida (FH), University of Applied Sciences, Fakultät Elektro- und Informationstechnik Diplomarbeit, 2012 Referat: Das Projekt „Pfeifen-Orgel mit dynamischer Stimmung“ ist ein Steuerungssystem zur Verbesserung der Klangqualität einer Orgel. Das System besteht aus dezentralen Elementen und einer zentralen Steuerung. Diese Arbeit befasst sich mit der Entwicklung der zentralen Einheit, der Zentralen Ak- tor-Steuerung. Ihre Aufgabe umfasst grundlegend die Mikrocontroller gestützte Da- tenverarbeitung und Kommunikation über spezielle, im Projekt benötigte Peripherie. Für die an diese Arbeit angrenzende Entwicklung der Steuerungssoftware, verfügt die Hardwareplattform über ein angepasstes Embedded Linux. Inhaltsverzeichnis Inhaltsverzeichnis...............................................................................................I -

Front Panel I/O Connectivity Design Guide

Front Panel I/O Connectivity Design Guide Revision 1.1 July 2018 Document Number: 600569 Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Intel technologies’ features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com. Intel technologies may require enabled hardware, specific software, or services activation. Check with your system manufacturer or retailer. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548- 4725 or visit www.intel.com/design/literature.htm. Intel and the Intel logo are trademarks of Intel Corporation in the U.S. -

Apogee Ensemble Thunderbolt Audio Interface

Apogee Ensemble Thunderbolt Audio Interface User’s Guide Fall 2014 Contents Overview!...........................................................................................................5 Introduction!................................................................................................................5 Features!.......................................................................................................................5 Package Contents!......................................................................................................6 Ensemble Thunderbolt Panel Tour!...........................................................................7 Front Panel!.................................................................................................................7 Rear Panel!..................................................................................................................8 Display!........................................................................................................................9 Input Settings Display Screen!..................................................................................9 Getting Started!...............................................................................................10 Precautions when powering Ensemble On/Off!......................................................10 Thunderbolt Notes!....................................................................................................10 Ensemble Software!..................................................................................................11 -

User's Guide M-Audio Ozone

M-Audio Ozone version: MA-Ozone_052803 User’s Guide Introduction . .2 M-Audio Ozone Features . .2 M-Audio Ozone Overview . .2 What’s in the Box . .3 Guide to Getting Started . .4 M-Audio Ozone Panel Features . .4 Top Panel . .4 Rear Panel . .6 M-Audio Ozone Driver Installation . .7 Driver Installation for Windows . .7 Windows XP: . .8 Windows 2000: . .12 Windows ME: . .16 Windows 98SE: . .18 M-Audio Ozone and the Windows Sound System . .23 Macintosh Driver Installation . .23 OMS Installation . .24 M-Audio Ozone Driver Installation . .24 OMS Configuration (Mac OS9 only) . .25 M-Audio Ozone and the Mac OS 9 Sound Manager . .27 M-Audio Ozone and Mac OS X . .27 The M-Audio Ozone Control Panel . .28 Application Software Setup . .30 M-Audio Ozone Hardware Installation . .31 M-Audio Ozone Audio Setup and Control . .31 Using the Mic and Instrument Inputs . .33 Setting Input Gain . .34 Phantom Power . .34 Using the Aux Inputs . .35 Using Direct Monitor . .36 M-Audio Ozone MIDI Setup and Control . .37 MIDI Functions In Standalone Mode . .39 Utilizing the Programming Assignment Keys . .39 Technical Support & Contact Information . .44 M-Audio Ozone Warranty Information . .45 M-Audio Ozone Technical Specifications . .46 Appendix A - MIDI Controller Information . .47 Appendix B - M-Audio Ozone Block Diagram . .48 Introduction Congratulations on your purchase of the M-Audio Ozone. The M-Audio Ozone is an innovative product—a powerful combination of MIDI controller and audio interface with microphone and instrument preamps that will turn your computer into a virtual music production studio. You may use your M-Audio Ozone in conjunction with a USB-equipped PC or Macintosh computer and appropriate music software to enter a full range of MIDI note and controller information, as well as record and play back your voice, guitar, or external sound modules. -

Serial Communication Buses

Computer Architecture 10 Serial Communication Buses Made wi th OpenOffi ce.org 1 Serial Communication SendingSending datadata oneone bitbit atat oneone time,time, sequentiallysequentially SerialSerial vsvs parallelparallel communicationcommunication cable cost (or PCB space), synchronization, distance ! speed ? ImprovedImproved serialserial communicationcommunication technologytechnology allowsallows forfor transfertransfer atat higherhigher speedsspeeds andand isis dominatingdominating thethe modernmodern digitaldigital technology:technology: RS232, RS-485, I2C, SPI, 1-Wire, USB, FireWire, Ethernet, Fibre Channel, MIDI, Serial Attached SCSI, Serial ATA, PCI Express, etc. Made wi th OpenOffi ce.org 2 RS232, EIA232 TheThe ElectronicElectronic IndustriesIndustries AllianceAlliance (EIA)(EIA) standardstandard RS-232-CRS-232-C (1969)(1969) definition of physical layer (electrical signal characteristics: voltage levels, signaling rate, timing, short-circuit behavior, cable length, etc.) 25 or (more often) 9-pin connector serial transmission (bit-by-bit) asynchronous operation (no clock signal) truly bi-directional transfer (full-duplex) only limited power can be supplied to another device numerous handshake lines (seldom used) many protocols use RS232 (e.g. Modbus) Made wi th OpenOffi ce.org 3 Voltage Levels RS-232RS-232 standardstandard convertconvert TTL/CMOS-levelTTL/CMOS-level signalssignals intointo bipolarbipolar voltagevoltage levelslevels toto improveimprove noisenoise immunityimmunity andand supportsupport longlong cablecable lengthslengths TTL/CMOS → RS232: 0V = logic zero → +3V…+12V (SPACE) +5V (+3.3V) = logic one → −3V…−12V (MARK) Some equipment ignores the negative level and accepts a zero voltage level as the "OFF" state The "dead area" between +3V and -3V may vary, many receivers are sensitive to differentials of 1V or less Made wi th OpenOffi ce.org 4 Data frame CompleteComplete one-byteone-byte frameframe consistsconsists of:of: start-bit (SPACE), data bits (7, 8), stop-bits (MARK) e.g. -

Getting Started with Microchip's Low Pin Count USB Solutions

Slide 1 Getting Started with Microchip's Low Pin Count USB solutions Welcome to “Getting Started with Microchip’s Low Pin Count USB Solutions”. This self-directed course is intended to provide the user with a quick overview of the USB, introduce the new Low Pin Count USB Development kit, and Microchip’s Full-Speed USB Firmware Framework to ease the development of your own USB applications quickly. Slide 2 Class Prerequisites O Attendees should have a the following: - A general knowledge of the Universal Serial Bus (USB) - A working knowledge of the C programming language - Familiarity with Microchip’s High Performance PIC18 Microcontrollers Getting Started with Microchip’s Low Pin Count USB Solutions Slide 2 In order to fully benefit from this self-directed course the user should have a very basic knowledge of the USB, have programmed in C, and be familiar with Microchip’s High Performance PIC18 Microcontrollers. Once completed, the user should complete the Project Labs listed in the Low Pin-Count USB Development kit user’s guide. Slide 3 Agenda O High-level overview of the USB and how it relates to the PIC18F1XK50 Device - Physical and Logical Topologies - “Plug and Play” - Communication O Overview of Microchip’s Low Pin Count USB Solutions - Low Pin-Count USB Development Kit - Microchip’s Full Speed USB Firmware Framework Getting Started with Microchip’s Low Pin Count USB Solutions Slide 3 This class will begin with an overview, albeit moderately high-level, of the USB. This is a complex protocol. Therefore, you should not feel discouraged if you don’t understand everything the first time through this class. -

Memory Technology and Trends for High Performance Computing Contract #: MDA904-02-C-0441

Memory Technology and Trends for High Performance Computing Contract #: MDA904-02-C-0441 Contract Institution: Georgia Institute of Technology Project Director: D. Scott Wills Project Report 12 September 2002 — 11 September 2004 This project explored the impact of developing memory technologies on future supercomputers. This activity included both a literature study (see attached whitepaper), plus a more practical exploration of potential memory interfacing techniques using the sponsor recommended HyperTransport interface. The report indicates trends that will affect interconnection network design in future supercomputers. Related publications during the contract period include: 1. P. G. Sassone and D. S. Wills, On the Scaling of the Atlas Chip-Scale Multiprocessor, to appear in IEEE Transaction on Computers. 2. P. G. Sassone and D. S. Wills, Dynamic Strands: Collapsing Speculative Dependence Chains for Reducing Pipeline Communication, to appear in IEEE/ACM International Symposium on Microarchitecture, Portland, OR, December 2004. 3. B. A. Small, A. Shacham, K. Bergman, K. Athikulwongse, C. Hawkins, and D. S. Wills, Emulation of Realistic Network Traffic Patterns on an Eight-Node Data Vortex Interconnection Network Subsystem, to appear in OSA Journal of Optical Networking. 4. P. G. Sassone and D. S. Wills, On the Extraction and Analysis of Prevalent Dataflow Patterns, to appear in The IEEE 7th Annual Workshop on Workload Characterization (WWC-7), 8 pages, Austin, TX, October 2004. 5. H. Kim, D. S. Wills, and L. M. Wills, Empirical Analysis of Operand Usage and Transport in Multimedia Applications, in Proceedings of the 4th IEEE International Workshop on System-on-Chip for Real-Time Applications(IWSOC'04), pages 168-171, Banff, Alberta, Canada, July 2004.