A Digital Controller for the Omega West Reactor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

The Observer's Handbook for 1912

T he O bservers H andbook FOR 1912 PUBLISHED BY THE ROYAL ASTRONOMICAL SOCIETY OF CANADA E d i t e d b y C. A, CHANT FOURTH YEAR OF PUBLICATION TORONTO 198 C o l l e g e St r e e t Pr in t e d fo r t h e So c ie t y 1912 T he Observers Handbook for 1912 PUBLISHED BY THE ROYAL ASTRONOMICAL SOCIETY OF CANADA TORONTO 198 C o l l e g e St r e e t Pr in t e d fo r t h e S o c ie t y 1912 PREFACE Some changes have been made in the Handbook this year which, it is believed, will commend themselves to observers. In previous issues the times of sunrise and sunset have been given for a small number of selected places in the standard time of each place. On account of the arbitrary correction which must be made to the mean time of any place in order to get its standard time, the tables given for a particualar place are of little use any where else, In order to remedy this the times of sunrise and sunset have been calculated for places on five different latitudes covering the populous part of Canada, (pages 10 to 21), while the way to use these tables at a large number of towns and cities is explained on pages 8 and 9. The other chief change is in the addition of fuller star maps near the end. These are on a large enough scale to locate a star or planet or comet when its right ascension and declination are given. -

Chapter 16 the Sun and Stars

Chapter 16 The Sun and Stars Stargazing is an awe-inspiring way to enjoy the night sky, but humans can learn only so much about stars from our position on Earth. The Hubble Space Telescope is a school-bus-size telescope that orbits Earth every 97 minutes at an altitude of 353 miles and a speed of about 17,500 miles per hour. The Hubble Space Telescope (HST) transmits images and data from space to computers on Earth. In fact, HST sends enough data back to Earth each week to fill 3,600 feet of books on a shelf. Scientists store the data on special disks. In January 2006, HST captured images of the Orion Nebula, a huge area where stars are being formed. HST’s detailed images revealed over 3,000 stars that were never seen before. Information from the Hubble will help scientists understand more about how stars form. In this chapter, you will learn all about the star of our solar system, the sun, and about the characteristics of other stars. 1. Why do stars shine? 2. What kinds of stars are there? 3. How are stars formed, and do any other stars have planets? 16.1 The Sun and the Stars What are stars? Where did they come from? How long do they last? During most of the star - an enormous hot ball of gas day, we see only one star, the sun, which is 150 million kilometers away. On a clear held together by gravity which night, about 6,000 stars can be seen without a telescope. -

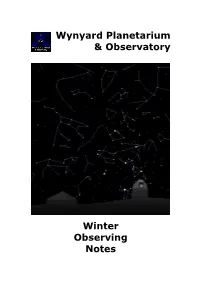

Winter Observing Notes

Wynyard Planetarium & Observatory Winter Observing Notes Wynyard Planetarium & Observatory PUBLIC OBSERVING – Winter Tour of the Sky with the Naked Eye NGC 457 CASSIOPEIA eta Cas Look for Notice how the constellations 5 the ‘W’ swing around Polaris during shape the night Is Dubhe yellowish compared 2 Polaris to Merak? Dubhe 3 Merak URSA MINOR Kochab 1 Is Kochab orange Pherkad compared to Polaris? THE PLOUGH 4 Mizar Alcor Figure 1: Sketch of the northern sky in winter. North 1. On leaving the planetarium, turn around and look northwards over the roof of the building. To your right is a group of stars like the outline of a saucepan standing up on it’s handle. This is the Plough (also called the Big Dipper) and is part of the constellation Ursa Major, the Great Bear. The top two stars are called the Pointers. Check with binoculars. Not all stars are white. The colour shows that Dubhe is cooler than Merak in the same way that red-hot is cooler than white-hot. 2. Use the Pointers to guide you to the left, to the next bright star. This is Polaris, the Pole (or North) Star. Note that it is not the brightest star in the sky, a common misconception. Below and to the right are two prominent but fainter stars. These are Kochab and Pherkad, the Guardians of the Pole. Look carefully and you will notice that Kochab is slightly orange when compared to Polaris. Check with binoculars. © Rob Peeling, CaDAS, 2007 version 2.0 Wynyard Planetarium & Observatory PUBLIC OBSERVING – Winter Polaris, Kochab and Pherkad mark the constellation Ursa Minor, the Little Bear. -

Relative Fission Product Yield Determination in the Usgs

RELATIVE FISSION PRODUCT YIELD DETERMINATION IN THE USGS TRIGA MARK I REACTOR by Michael A. Koehl © Copyright by Michael A. Koehl, 2016 All Rights Reserved A thesis submitted to the Faculty and the Board of Trustees of the Colorado School of Mines in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Nuclear Engineering). Golden, Colorado Date: ____________________ Signed: ________________________ Michael A. Koehl Signed: ________________________ Dr. Jenifer C. Braley Thesis Advisor Golden, Colorado Date: ____________________ Signed: ________________________ Dr. Mark P. Jensen Professor and Director Nuclear Science and Engineering Program ii ABSTRACT Fission product yield data sets are one of the most important and fundamental compilations of basic information in the nuclear industry. This data has a wide range of applications which include nuclear fuel burnup and nonproliferation safeguards. Relative fission yields constitute a major fraction of the reported yield data and reduce the number of required absolute measurements. Radiochemical separations of fission products reduce interferences, facilitate the measurement of low level radionuclides, and are instrumental in the analysis of low-yielding symmetrical fission products. It is especially useful in the measurement of the valley nuclides and those on the extreme wings of the mass yield curve, including lanthanides, where absolute yields have high errors. This overall project was conducted in three stages: characterization of the neutron flux in irradiation positions within the U.S. Geological Survey TRIGA Mark I Reactor (GSTR), determining the mass attenuation coefficients of precipitates used in radiochemical separations, and measuring the relative fission products in the GSTR. Using the Westcott convention, the Westcott flux, ; modified spectral index, ; neutron temperature, ; and gold-based cadmium ratiosφ were determined for various sampling√⁄ positions in the USGS TRIGA Mark I reactor. -

Constellation Studies - Equatorial Sky in Winter

Phys1810: General Astronomy 1 W2014 Constellation Studies - Equatorial Sky in Winter Preparation before the observing session - Read "Notes on Observing" thoroughly. - Find all the targets listed below using Starry Night and your star charts. - Note: The observatory longitude is 97.1234° W, the latitude is 49.6452° N and elevation is 233 meters. - Observe any predicted events and record your observations during the observing session In the list of constellations below, the name of the constellation is underlined followed by the genitive case of the name in parenthesis followed by the three-letter abbreviation. Note that references to stars such as α UMa, spoken as alpha Ursae Majoris (note genitive case), literally means alpha of Ursa Major. The Greek letters are usually assigned in order of brightness in the constellation (α -- brightest). Note that the constellation, Ursa Major, is a major exception to this rule. As soon as you get to the observatory the following 3 constellations should be sketched on a full page diagram making sure that their relative positions to each other and to the horizon are drawn as accurately as possible - this means completing the sketch in about 15 minutes. You need to repeat the sketch one hour later. Be sure to indicate the time and the location of the horizon on your diagram. Ursa Major (Ursae Majoris) UMa: (The Great Bear, The Big Dipper, The Plow) Through all ages, Ursa Major has been known under various names. It is linked with the nymph Kallisto, the daughter of Lycaon, a king of Arcadia in Greek mythology. Moving along the asterism of the dipper from the lip identify the stars Dubhe (α UMa), Merak (β UMa), Phecda (γ UMa), Megrez (δ UMa), Alioth (ε UMa), Mizar (ζ UMa), and Alkaid (η UMa). -

Focus on Zeta Ursae Majoris - Mizar

Vol. 3 No. 2 Spring 2007 Journal of Double Star Observations Page 51 Stargazers Corner: Focus on Zeta Ursae Majoris - Mizar Jim Daley Ludwig Schupmann Observatory (LSO) New Ipswich, New Hampshire Email: [email protected] Abstract: : This is a general interest article for both the double star viewer and armchair astronomer alike. By highlighting an interesting pair, hopefully in each issue, we have a place for those who love doubles but may have little interest in the rigors of measurements and the long lists of results. Your comments about these mini-articles are welcomed. Arabs long ago named Alcor “Saidak” or “the proof” as Introduction they too used it as a test of vision. Alcor shares nearly My first view of a double star through a telescope the same space motion with Mizar and about 20 other was an inspiring sight and just as with many new stars in what is called the Ursa Major stream or observers today, the star was Mizar. As a beginning moving cluster. The Big Dipper is considered the amateur telescope maker (1951) I followed tradition closest cluster in the solar neighborhood. Alcor’s and began to use closer doubles for resolution testing apparent separation from Mizar is more than a quar- the latest homemade instrument. Visualizing the ter light year and this alone just about rules out this scale of binaries, their physical separation, Keplerian wide pair from being a physical (in a binary star motion, orbital period, component diameters and sense) system and the most recent line-of-sight dis- spectral characteristics, all things I had heard and tance measurements give a difference between them read of, seemed a bit complicated at the time and, I of about 3 light years, ending any ideas of an orbiting might add, more so now! Through the years I found pair. -

The Observer's Handbook for 1915

T he O b s e r v e r ’s H a n d b o o k FOR 1915 PUBLISHED BY The Royal Astronomical Society Of Canada E d i t e d b y C . A. CHANT SEVENTH YEAR OF PUBLICATION TORONTO 198 C o l l e g e S t r e e t Pr in t e d f o r t h e S o c ie t y CALENDAR 1915 T he O bserver' s H andbook FOR 1915 PUBLISHED BY The Royal Astronomical Society Of Canada E d i t e d b y C. A. CHANT SEVENTH YEAR OF PUBLICATION TORONTO 198 C o l l e g e S t r e e t Pr in t e d f o r t h e S o c ie t y 1915 CONTENTS Preface - - - - - - 3 Anniversaries and Festivals - - - - - 3 Symbols and Abbreviations - - - - -4 Solar and Sidereal Time - - - - 5 Ephemeris of the Sun - - - - 6 Occultation of Fixed Stars by the Moon - - 8 Times of Sunrise and Sunset - - - - 8 The Sky and Astronomical Phenomena for each Month - 22 Eclipses, etc., of Jupiter’s Satellites - - - - 46 Ephemeris for Physical Observations of the Sun - - 48 Meteors and Shooting Stars - - - - - 50 Elements of the Solar System - - - - 51 Satellites of the Solar System - - - - 52 Eclipses of Sun and Moon in 1915 - - - - 53 List of Double Stars - - - - - 53 List of Variable Stars- - - - - - 55 The Stars, their Magnitude, Velocity, etc. - - - 56 The Constellations - - - - - - 64 Comets of 1914 - - - - - 76 PREFACE The H a n d b o o k for 1915 differs from that for last year chiefly in the omission of the brief review of astronomical pro gress, and the addition of (1) a table of double stars, (2) a table of variable stars, and (3) a table containing 272 stars and 5 nebulae. -

CONSTELLATION URSA MAJOR, the GREAT BEAR Ursa Major (Also Known As the Great Bear) Is a Constellation in the Northern Celestial Hemisphere

CONSTELLATION URSA MAJOR, THE GREAT BEAR Ursa Major (also known as the Great Bear) is a constellation in the northern celestial hemisphere. It was one of the 48 constellations listed by Ptolemy (second century AD), and remains one of the 88 modern constellations. It can be visible throughout the year in most of the northern hemisphere. Its name stands as a reference to and in direct contrast with Ursa Minor, "the smaller bear", with which it is frequently associated in mythology and amateur astronomy. The constellation's most recognizable asterism, a group of seven relatively bright stars commonly known as the "Big Dipper", "the Wagon" or "the Plough", both mimics the shape of the lesser bear (the "Little Dipper") and is commonly used as a navigational pointer towards the current northern pole star, Polaris in Ursa Minor. The Big Dipper and the constellation as a whole have mythological significance in numerous world cultures, usually as a symbol of the north. Being the third largest constellation in the night sky, with 1279.66 square degrees of surface area Ursa Major is home to many deep-sky objects including seven Messier objects, four other NGC objects and I Zwicky 18, the youngest known galaxy in the visible universe. The official constellation boundaries, set by Eugène Delporte in 1930, form a 28-sided irregular polygon. It is bordered by eight other constellations: Draco to the north and northeast, Boötes to the east, Canes Venatici to the east and southeast, Coma Berenices to the southeast, Leo and Leo Minor to the south, Lynx to the southwest and Camelopardalis to the northwest. -

NRC Collection of Abbreviations

I Nuclear Regulatory Commission c ElLc LI El LIL El, EEELIILE El ClV. El El, El1 ....... I -4 PI AVAILABILITY NOTICE Availability of Reference Materials Cited in NRC Publications Most documents cited in NRC publications will be available from one of the following sources: 1. The NRC Public Document Room, 2120 L Street, NW., Lower Level, Washington, DC 20555-0001 2. The Superintendent of Documents, U.S. Government Printing Office, P. 0. Box 37082, Washington, DC 20402-9328 3. The National Technical Information Service, Springfield, VA 22161-0002 Although the listing that follows represents the majority of documents cited in NRC publica- tions, it is not intended to be exhaustive. Referenced documents available for inspection and copying for a fee from the NRC Public Document Room include NRC correspondence and internal NRC memoranda; NRC bulletins, circulars, information notices, inspection and investigation notices; licensee event reports; vendor reports and correspondence; Commission papers; and applicant and licensee docu- ments and correspondence. The following documents in the NUREG series are available for purchase from the Government Printing Office: formal NRC staff and contractor reports, NRC-sponsored conference pro- ceedings, international agreement reports, grantee reports, and NRC booklets and bro- chures. Also available are regulatory guides, NRC regulations in the Code of Federal Regula- tions, and Nuclear Regulatory Commission Issuances. Documents available from the National Technical Information Service Include NUREG-series reports and technical reports prepared by other Federal agencies and reports prepared by the Atomic Energy Commission, forerunner agency to the Nuclear Regulatory Commission. Documents available from public and special technical libraries include all open literature items, such as books, journal articles, and transactions. -

Annual Report Procurement Organization Sandia National Laboratories Fiscal Year 1996

MAY SANDIA REPORT SAND97-0725 • UC-900 Unlimited Release Printed April 1997 Annual Report Procurement Organization .. ,: ,~ _" Sandia National Laboratories e-• \~.~<. l~ \{/ Fiscal Year 1996 D. L. Palmer Prepared by Sandia National Laborator'es Albuquerque, New 87185 and Livermore, California, 94550, Sandia is a multipro , m '1aboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy under Contr~ct DE-AC04°94AL115000, / - < \\'. ( ', . ' : . ..,- : . ' _·· i :•: Approved for.@bltc'release; ,; · , .: . ,'' SF2900O(8-81) Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation. NOTICE: This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Govern ment nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, prod uct, or process disclosed, or represents that its use would not infringe pri vately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Govern ment, any agency thereof, or any of their contractors. Printed in the United States of America. This report has been reproduced directly from the best available copy. -

Introduction

Cambridge University Press 978-1-107-53420-9 - The Cambridge Double Star Atlas Bruce Macevoy and Wil Tirion Excerpt More information INTRODUCTION This new edition of the Cambridge Double Star Atlas Jim Mullaney’s choice of nineteenth century double is designed to improve its utility for amateur star catalog labels has been retained as a tribute both astronomers of all skill levels. to his original Atlas concept and to the bygone astral For the first time in a publication of this type, the explorers who discovered over 90% of the systems in the focus is squarely on double stars as physical systems,so target list (see Appendix D). These labels are also a far as these can be identified with existing data. convenient link to the legacy double star literature and a Using the procedures described in Appendix A, the compact labeling style for the Atlas charts. However, target list of double stars has been increased to 2,500 as a convenience to the digital astronomer, the target systems by adding 1,100 “high probability” physical list provides both the Henry Draper (HD) and double and multiple stars and deleting more than Smithsonian (SAO) catalog numbers for each system. 850 systems beyond the reach of amateur telescopes The first will identify each system in the research or lacking any evidence of a physical connection. literature and online astronomical databases, the second Wil Tirion has completely relabeled the Atlas charts is a compact targeting command or search keyword to reflect these changes, and left in place the previous recognized by most GoTo telescope mounts and edition’s double star icons as a basis for comparison. -

Early Reactors from Fermi’S Water Boiler to Novel Power Prototypes

Early Reactors From Fermi’s Water Boiler to Novel Power Prototypes by Merle E. Bunker n the urgent wartime period of the Canyon. Fuel for the reactor consumed the morning and then spend his afternoons down Manhattan Project, research equip- country’s total supply of enriched uranium at the reactor. He always analyzed the data ment was being hurriedly com- (14 percent uranium-235). To help protect as it was being collected. He was very I mandeered for Los Alamos from uni- this invaluable material, two machine-gun insistent on this point and would stop an versities and other laboratories. This equip- posts were located at the site. experiment if he did not feel that the results ment was essential for obtaining data vital to The reactor (Fig. 1) was called LOPO (for made sense.” On the day that LOPO the design of the first atomic bomb. A nuclear low power) because its power output was achieved criticality, in May 1944 after one reactor, for example, was needed for checking virtually zero. This feature simplified its final addition of enriched uranium, Fermi critical-mass calculations and for measuring design and construction and eliminated the was at the controls. fission cross sections and neutron capture and need for shielding. The liquid fuel, an LOPO served the purposes for which it scattering cross sections of various materials, aqueous solution of enriched uranyl sulfate, had been intended: determination of the particularly those under consideration as was contained in a l-foot-diameter stainless- critical mass of a simple fuel configuration moderators and reflectors.