Wolfson WM9715L Audio Codec and Touch Screen Controller

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Mobile Audio IC Industry Report, 2007-2008

Mobile Audio IC Industry Report, 2007-2008 MobileaudioICismainlyappliedtomobilephoneandMP3 playersandnowitisextendedtogameconsole,hand-held navigation,digitalcameraandotherfields.However, applicationinthesefieldsisstillsmall,Comparedtothatin mobilephoneandMP3players.MobilephoneaudioICis dividedintothreecategories,namelymelodyIC,CODEC,and audioamplifierIC.TheaudioICofMP3playersmainlyadopts MP3decoderICandCODEC. MelodyICmarketprospectsarebleak.Keyglobalmobile phonemanufacturers,likeNokia,Motorola,Sony-Ericssonand Siemens,seldomadoptmelodyIC.Especiallysince2005,the fourbigproducershavegenerallyusedapplicationprocessor andcustomizedanalogbaseband toreplacemelodyIC.In earlystage,mainlyJapanesemobilephoneproducers, Samsung,LGandChinesehandsetproducersadoptedmelody ICchips.Nowadays,onlyJapanesemanufacturersstillinsist onadoptingmelodyIC,andtherestallhavegivenitup. ThereareonlyasmallnumberofaudioCODECmanufacturers,mainlyTI,AKMandWolfson Microelectronics.Audio CODECmarketentrythresholdisveryhigh,andonlythemanufacturersmasteringDELTA-SIGMAconversioncan winthemselvesaplaceinthefield.What'smore,audioCODECis mostlyappliedtocompressedmusicplayers,and especiallyahugeamountisusedinMP3anddigitalcamera.ToCODECproducers,mobilephoneisonlytheir sidelinebusiness,aboutwhichtheydon'tcaremuch,iftheyloseit.AsforMP3player,Wolfson isabsolutelythe marketdominator,monopolizingthemarket.Asfornon-portablemusicplayerslikeCDplayerandprofessional acousticsequipment,ADI,AKMandCirrussharethemarket.Wolfson isseldominvolvedinthehigh-quality audiomarket.Thesemanufacturersarecomparativelyconservative,andtheydon'tpaymuchattentiontoportable -

MAX3946 1Gbps to 11.3Gbps, SFP+ Laser Driver with Laser Impedance

19-5182; Rev 1; 5/11 EVALUATION KIT AVAILABLE 1Gbps to 11.3Gbps, SFP+ Laser Driver with Laser Impedance Mismatch Tolerance MAX3946 General Description Features The MAX3946 is a +3.3V, multirate, low-power laser S 225mW Power Dissipation Enables < 1W SFP+ diode driver designed for Ethernet and Fibre Channel Modules transmission systems at data rates up to 11.3Gbps. S Up to 100mW Power Consumption Reduction by This device is optimized to drive a differential transmit- Enabling the Use of Unmatched FP/DFB TOSAs ter optical subassembly (TOSA) with a 25I flex circuit. The unique design of the output stage enables use of S Supports SFF-8431 SFP+ MSA and SFF-8472 unmatched TOSAs, greatly reducing headroom limita- Digital Diagnostic tions and lowering power consumption. S 225mW Power Dissipation at 3.3V (IMOD = 40mA, The device receives differential CML-compatible signals IBIAS = 60mA Assuming 25I TOSA) with on-chip line termination. It can deliver laser modula- S Single +3.3V Power Supply tion current of up to 80mA, at an edge speed of 22ps S Up to 11.3Gbps (NRZ) Operation (20% to 80%), into a 5I to 25I external differential load. S Programmable Modulation Current from 10mA to The device is designed to have a symmetrical output 100mA (5I Load) stage with on-chip back terminations integrated into its outputs. A high-bandwidth, fully differential signal S Programmable Bias Current from 5mA to 80mA path is implemented to minimize deterministic jitter. An S Programmable Input Equalization equalization block can be activated to compensate for S Programmable Output Deemphasis the SFP+ connector. -

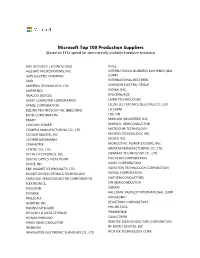

Microsoft Top 100 Production Suppliers (Based on FY14 Spend for Commercially Available Hardware Products)

Microsoft Top 100 Production Suppliers (Based on FY14 spend for commercially available hardware products) AAC ACOUSTIC TECHNOLOGIES INTEL ALLEGRO MICROSYSTEMS, INC. INTERNATIONAL BUSINESS MACHINES (IBM ALPS ELECTRIC COMPANY CORP.) AMD INTERNATIONAL RECTIFIER AMPEREX TECHNOLOGY, LTD. JOHNSON ELECTRIC GROUP AMPHENOL KIONIX, INC. ANALOG DEVICES KYOCERA/AVX ASKEY COMPUTER CORPORATION LAIRD TECHNOLOGIES ATMEL CORPORATION LELON ELECTRONICS (SUZHOU) CO., LTD BIZLINK TECHNOLOGY INC (BIZCONN) LG CHEM BOYD CORPORATION LITE-ON BRADY MARLOW INDUSTRIES, INC. CHICONY POWER MARVELL SEMICONDUCTOR COMPEQ MANUFACTURING CO., LTD. MICROCHIP TECHNOLOGY COOLER MASTER, INC. MICRON TECHNOLOGY, INC. COOPER BUSSMANN MOLEX, INC. CYMMETRIK MONOLITHIC POWER SYSTEMS, INC. CYNTEC CO., LTD. MURATA MANUFACTURING CO., LTD. DELTA ELECTRONICS, INC. NEWMAX TECHNOLOGY CO., LTD. DIGITAL OPTICS VISTA POINT NICHICON CORPORATION DIODE, INC. NIDEC CORPORATION E&E MAGNETICS PRODUCTS, LTD. NUVOTON TECHNOLOGY CORPORATION ELLINGTON ELECTRONICS TECHNOLOGY NVIDIA CORPORATION FAIRCHILD SEMICONDUCTOR CORPORATION NXP SEMICONDUCTORS FLEXTRONICS ON SEMICONDUCTOR FOXCONN OSRAM FOXLINK PALCONN, PALPILOT INTERNATIONAL CORP. FREESCALE PANASONIC GOERTEK, INC. PEGATRON CORPORATION HANNSTAR BOARD PHILIPS PLDS HITACHI-LG DATA STORAGE PRIMESENSE HONDA PRINTING QUALCOMM HYNIX SEMICONDUCTOR REALTEK SEMICONDUCTOR CORPORATION INFINEON RF MICRO DEVICES, INC. INNOVATOR ELECTRONIC SHENZHEN CO., LTD RICHTEK TECHNOLOGY CORP. ROHM CORPORATION SAMSUNG DISPLAY SAMSUNG ELECTRONICS SAMSUNG SDI SAMSUNG SEMICONDUCTOR SEAGATE SHEN ZHEN JIA AI MOTOR CO., LTD. SHENZHEN HORN AUDIO CO., LTD. SHINKO ELECTRIC INDUSTRIES CO., LTD. STARLITE PRINTER, LTD. STMICROELECTRONICS SUNG WEI SUNUNION ENVIRONMENTAL PACKAGING CO., LTD TDK TE CONNECTIVITY TEXAS INSTRUMENTS TOSHIBA TPK TOUCH SOLUTIONS, INC. UNIMICRON TECHNOLOGY CORP. UNIPLAS (SHANGHAI) CO., LTD. UNISTEEL UNIVERSAL ELECTRONICS INCORPORATED VOLEX WACOM CO., LTD. WELL SHIN TECHNOLOGY WINBOND WOLFSON MICROELECTRONICS, LTD. X-CON ELECTRONICS, LTD. YUE WAH CIRCUITS CO., LTD. -

C 2016 Anupam Das UNDERSTANDING and MITIGATING the PRIVACY RISKS of SMARTPHONE SENSOR FINGERPRINTING

c 2016 Anupam Das UNDERSTANDING AND MITIGATING THE PRIVACY RISKS OF SMARTPHONE SENSOR FINGERPRINTING BY ANUPAM DAS DISSERTATION Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2016 Urbana, Illinois Doctoral Committee: Associate Professor Nikita Borisov, Chair Associate Professor Matthew Caesar Associate Professor Romit Roy Choudhury Assistant Professor Paris Smaragdis Professor Dan Boneh, Stanford University ABSTRACT The widespread use of smartphones in our everyday life gives rise to pri- vacy concerns. Fingerprinting smartphones can jeopardize user privacy by enabling remote identification of users without users' awareness. In this dissertation we study the feasibility of using onboard sensors such as micro- phones, accelerometers and gyroscopes to fingerprint smartphones. During fabrication, subtle imperfections arise in device sensors which induce distinc- tive anomalies in the generated signal. Using machine learning techniques we can distinguish smartphones generating such distinctive anomalies. We first look at fingerprinting smartphones through onboard microphones and speakers. We explore different acoustic features and analyze their ability to successfully fingerprint smartphones. Our study identifies the prominent acoustic features capable of fingerprinting smartphones with a high success rate, and also examines the impact of background noise and other variables on fingerprinting accuracy. Next, we surreptitiously fingerprint smartphones us- ing the imperfections of motion sensors (i.e., accelerometers and gyroscopes) embedded in modern smartphones, through a web page. We analyze how well motion sensor fingerprinting works under real-world constraints by col- lecting data from a large number of smartphones under both lab and public environments. -

CP/M-80 Kaypro

$3.00 June-July 1985 . No. 24 TABLE OF CONTENTS C'ing Into Turbo Pascal ....................................... 4 Soldering: The First Steps. .. 36 Eight Inch Drives On The Kaypro .............................. 38 Kaypro BIOS Patch. .. 40 Alternative Power Supply For The Kaypro . .. 42 48 Lines On A BBI ........ .. 44 Adding An 8" SSSD Drive To A Morrow MD-2 ................... 50 Review: The Ztime-I .......................................... 55 BDOS Vectors (Mucking Around Inside CP1M) ................. 62 The Pascal Runoff 77 Regular Features The S-100 Bus 9 Technical Tips ........... 70 In The Public Domain... .. 13 Culture Corner. .. 76 C'ing Clearly ............ 16 The Xerox 820 Column ... 19 The Slicer Column ........ 24 Future Tense The KayproColumn ..... 33 Tidbits. .. .. 79 Pascal Procedures ........ 57 68000 Vrs. 80X86 .. ... 83 FORTH words 61 MSX In The USA . .. 84 On Your Own ........... 68 The Last Page ............ 88 NEW LOWER PRICES! NOW IN "UNKIT"* FORM TOO! "BIG BOARD II" 4 MHz Z80·A SINGLE BOARD COMPUTER WITH "SASI" HARD·DISK INTERFACE $795 ASSEMBLED & TESTED $545 "UNKIT"* $245 PC BOARD WITH 16 PARTS Jim Ferguson, the designer of the "Big Board" distributed by Digital SIZE: 8.75" X 15.5" Research Computers, has produced a stunning new computer that POWER: +5V @ 3A, +-12V @ 0.1A Cal-Tex Computers has been shipping for a year. Called "Big Board II", it has the following features: • "SASI" Interface for Winchester Disks Our "Big Board II" implements the Host portion of the "Shugart Associates Systems • 4 MHz Z80-A CPU and Peripheral Chips Interface." Adding a Winchester disk drive is no harder than attaching a floppy-disk The new Ferguson computer runs at 4 MHz. -

Week 49, 2018 – Friday 7Th December Click Here to View the Email As a PDF

Shipping Regulations and Guidance Week 49, 2018 – Friday 7th December Click Here to view the email as a PDF. Forward this email to a friend Flag State Regulations and Guidance Updates UK – has released a new marine guidance notice entitled 'ILO Work in Fishing Convention, 2007 (No. 188) – Fishermen's Work Agreements'. Australia – has released an amendment order to marine order 'Certificates of survey - national law'. Marshall Islands – has published a new marine safety advisory entitled 'Guidance on the Development of a Ship Implementation Plan for the Consistent Implementation of the 0.50% Sulphur Limit under MARPOL Annex VI'. Panama – has updated three circulars: 'Ballast Water Management Convention 2004, Panama Policy' 'Adoption of Amendments to MARPOL 73/78, Annex VI Panama Policy on IMO- DCS scheme'. 'Correction of Deficiencies found in ASI InspectionsCorrection of Deficiencies found in ASI Inspections'. Isle of Man – has issued a new shipping notice entitled 'SOLAS Chapter XI-2 & the ISPS Code'. Singapore – has released a new port marine circular entitled 'Johor Bahru Port Limits'. Recent Class Society Guidance American Bureau of Shipping – has released a new guidance document entitled 'Guide for Enhanced Shaft Alignment', and has updated seven collections of documents: 'Guide for Building and Classing International Naval Ships' 'Rules for Building and Classing Offshore Support Vessels' 'Rules for Building and Classing High-Speed Naval Craft' 'Rules for Building and Classing Mobile Offshore Drilling Units' 'Rules for Building and Classing High-Speed Craft' 'Rules for Building and Classing Steel Vessels' 'Rules for Building and Classing Steel Vessels Under 90 Meters in Length'. Bureau Veritas – has has issued a new guidance document entitled 'Rules for the Classification of Diving Systems'. -

Data Transfer Node (DTN) Tests on the GÉANT Testbeds Service (GTS)

09-12-2020 Data Transfer Node (DTN) Tests on the GÉANT Testbeds Service (GTS) Grant Agreement No.: 856726 Work Package WP6 Task Item: Task 2 Document ID: GN4-3-20-265f683 Authors: Iacovos Ioannou (CYNET), Damir Regvart (CARNET), Joseph Hill (UvA/SURF), Maria Isabel Gandia (CSUC/RedIRIS), Ivana Golub (PSNC), Tim Chown (Jisc), Susanne Naegele Jackson (FAU/DFN) © GÉANT Association on behalf of the GN4-3 project. The research leading to these results has received funding from the European Union’s Horizon 2020 research and innovation programme under Grant Agreement No. 856726 (GN4-3). Abstract Many research projects need to transfer large amounts of data and use specialised Data Transfer Nodes (DTNs) to optimise the efficiency of these transfers. In order to help NRENs to better support user communities who seek to move large volumes of data across their network, a DTN Focus Group was set up in the Network Technologies and Services Development work package (WP6) of the GN4-3 project, which has performed several activities around DTN deployment, the results of which are summarised in this document. Table of Contents Executive Summary 1 1 Introduction 2 2 The DTN Survey and DTN Wiki 5 3 Optimising DTN Configurations 6 3.1 Networking 6 3.1.1 Socket Parameters 7 3.1.2 TCP Socket Parameters 7 3.1.3 NIC Driver Settings 8 3.1.4 MTU Settings 8 3.2 Storage 9 3.2.1 Bus vs Disk Speed 9 3.2.2 Spinning versus Solid State Disks 9 3.2.3 NVMe 9 3.2.4 RAID 10 3.2.5 Remote Storage 10 3.3 Architecture 10 3.3.1 Fast Cores vs Many Cores 10 3.3.2 NUMA 10 3.3.3 -

European Technology Media & Telecommunications Monitor

European Technology Media & Telecommunications Monitor Market and Industry Update H1 2013 Piper Jaffray European TMT Team: Eric Sanschagrin Managing Director Head of European TMT [email protected] +44 (0) 207 796 8420 Jessica Harneyford Associate [email protected] +44 (0) 207 796 8416 Peter Shin Analyst [email protected] +44 (0) 207 796 8444 Julie Wright Executive Assistant [email protected] +44 (0) 207 796 8427 TECHNOLOGY, MEDIA & TELECOMMUNICATIONS MONITOR Market and Industry Update Selected Piper Jaffray H1 2013 TMT Transactions TMT Investment Banking Transactions Date: June 2013 $47,500,000 Client: IPtronics A/S Transaction: Mellanox Technologies, Ltd. signed a definitive agreement to acquire IPtronics A/S from Creandum AB, Sunstone Capital A/S and others for $47.5 million in cash. Pursuant to the Has Been Acquired By transaction, IPtronics’ current location in Roskilde, Denmark will serve as Mellanox’s first research and development centre in Europe and IPtronics A/S will operate as a wholly-owned indirect subsidiary of Mellanox Technologies, Ltd. Client Description: Mellanox Technologies Ltd. is a leading supplier of end-to-end InfiniBand and June 2013 Ethernet interconnect solutions and services for servers and storage. PJC Role: Piper Jaffray acted as exclusive financial advisor to IPtronics A/S. Date: May 2013 $46,000,000 Client: inContact, Inc. (NasdaqCM: SAAS) Transaction: inContact closed a $46.0 million follow-on offering of 6,396,389 shares of common stock, priced at $7.15 per share. Client Description: inContact, Inc. provides cloud contact center software solutions. PJC Role: Piper Jaffray acted as bookrunner for the offering. -

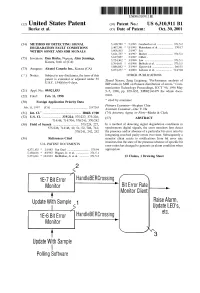

Update W Sample Polling Software U.S

USOO6310911B1 (12) United States Patent (10) Patent No.: US 6,310,911 B1 Burke et al. (45) Date of Patent: Oct. 30, 2001 (54) METHOD OF DETECTING SIGNAL 5,418,789 5/1995 Gersbach et al. ..................... 371/5.2 DEGRADATION FAULT CONDITIONS 5,467,341 11/1995 Matsukane et al. ................... 370/17 WITHIN SONET AND SDH SIGNALS 5,606,563 2/1997 Lee. 5,621,737 * 4/1997 Bucher .................................. 371/5.1 (75) Inventors: panist, Nips Alan Jennings, 5,724,3625,627,837 3/19985/1997 Gillett.Lau ....................................... 371/5.1 s 5,764,651 * 6/1998 Bullock et al. .. ... 371/5.5 rr. A 5,886,842 * 3/1999 Ziperovich ...... ... 360/51 (73) Assignee: Alcatel Canada Inc., Kanata (CA) 6,073,257 * 4/2000 Labonte et al. ...................... 714/704 (*) Notice: Subject to any disclaimer, the term of this OTHER PUBLICATIONS patent is extended or adjusted under 35 Zhand Xiaoru, Zneg Lieguang: "Performance analysis of U.S.C. 154(b) by 0 days. BIP codes in SDH on Poisson distribution of errors.” Com munication Technology Proceedings, ICCT '96, 1996 May (21) Appl. No.: 09/021,833 5–7, 1996, pp. 829–832, XP002146479 the whole docu (22) Filed: Feb. 11, 1998 ment. (30) Foreign Application Priority Data * cited by examiner Primary Examiner Stephen Chin Feb. 11, 1997 (CA) .................................................. 2197263 ASSistant Examiner-Dac V. Ha (51) Int. Cl." ................................................. H04B 17700 (74) Attorney, Agent, or Firm Marks & Clerk (52) U.S. Cl. .......................... 375/224; 375/227; 375/228; (57) ABSTRACT 714/48; 714/704; 370/241; 370/242 (58) Field of Search .................................... -

Conexant Systems, Inc

Conexant Systems, Inc. Notice of Annual Meeting, Proxy Statement and 2009 Annual Report on Form 10-K Corporate Overview Conexant develops innovative semiconductor solutions for imaging, audio, embedded-modem, and video applications, which are all areas where the company has established leadership positions. Conexant is a fabless company headquartered in Newport Beach, Calif., and has key design centers in the U.S., China, and India, and sales offi ces worldwide. CONEXANT SYSTEMS, INC. D. SCOTT MERCER CHAIRMAN AND CHIEF EXECUTIVE OFFICER To Our Shareholders: Conexant today is a company transformed. We are now a company to Wall Street in a series of investor meetings and smaller, leaner, and more profi table enterprise focused on successfully accessed the capital markets by executing a public delivering operational excellence and innovative semiconductor offering of new shares, raising a net amount of $21.2 million. solutions for imaging, audio, embedded-modem, and video surveillance applications. In each of these areas, we’re We are now focused on retiring, refi nancing, or restructuring committed to building on the leading positions we’ve established. our convertible notes, which are “puttable” in March 2011. In the past few months, we have been responding to requests by During fi scal 2009 we made outstanding progress across multiple note holders to exchange new shares of common stock for fronts. In the face of extraordinarily challenging economic convertible notes, which improves our balance sheet without conditions, we improved our fi nancial performance, strengthened negatively affecting our enterprise value. Satisfying our our capital structure, and introduced a full slate of compelling convertible debt remains one of our highest company priorities, new products. -

Press Release

Press Release Wolfson licenses Oxford Digital’s TinyCore DSP Edinburgh, UK, 5 January 2011 – Wolfson Microelectronics plc, a global leader in the design and development of mixed-signal semiconductors and Audio Hubs that combine to deliver High Definition Audio solutions, has today announced a licence agreement with audio processing specialist Oxford Digital Limited to use its digital signal processor (DSP) core in a selection of Wolfson’s industry-leading Audio Hub products. Oxford Digital’s TinyCore DSP core delivers a low-power, low gate count, highly configurable solution which simplifies the software development process, allowing easy porting of audio function algorithms thereby reducing the time-to-market for customers. Wolfson’s architecture-defining Audio Hubs blend together many of Wolfson’s successful audio components to deliver world-class audio performance, significantly enhanced battery life, longer music playback time and more end user features at a lower total cost. Crucially, Wolfson’s Audio Hubs enable system designers to optimally manage increasingly complex multiple use cases in portable multimedia applications including smartphones, tablet computers, e-book readers, navigation devices and media players. Eddie Sinnott, Portfolio Director at Wolfson Microelectronics, said, “We selected Oxford Digital’s TinyCore DSP due to its efficiency at executing certain key High Definition Audio algorithms, which our customers tell us provide them with a differentiator in their market place. Our choice was helped by the ease of its software porting process, excellent power efficiency, scalability and rapid time-to-market, all of which complement our architecture.” John Richards, CEO of Oxford Digital, said, “Wolfson is a leader in high-quality and low-power mixed-signal audio and we are excited to be working with them on integrating our IP into their products. -

Linux Commands Cheat Sheet

LINUX COMMANDS CHEAT SHEET by Gokhan Kosem, www.ipcisco.com System Information Commands User Information Commands shows user&group ids of the current uname -a shows Linux system info id user uname -r shows kernel release info last shows the last users logged on cat /etc/redhat-release shows installed redhat version whoami shows who you are logged in as uptime displays system running/life time who shows who is logged into the system shows who is logged in and what hostname shows system host name w they do hostname -I shows ip addresses of the host groupadd test creates group “test” creates “Gokhan” account with last reboot displays system reboot history useradd -c “GK” -m Gokhan comment “GK” date displays current date and time userdel Gokhan deletes account “Gokhan” usermod -aG Networkers adds account “Gokhan” to the cal displays monthly calendar Gokhan “Networkers” group mount shows mounted filesy-stems File Permission changes ownership of a File Commands chown user file/directory shows file type and access changes user and group for a file or ls -l chown user:group filename permission directory ls -a lists also hidden files r (read) permission, 4 ls -al lists files and directories detailly w (write) permission, 2 File Permissions pwd shows present directory x (execute) permission, 1 mkdir directory creates a directory -= no permission rm xyz deletes file xyz File Owner owner/group/everyone deletes directory /xyz and its 777 | Owner, Group, Everyone has rm -r /xyz contents recursively rwx permissions forcefully deletes abc file without