Precision Voltage-To-Current Converter/Transmitter Xtr110

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Optoisolators Transistors

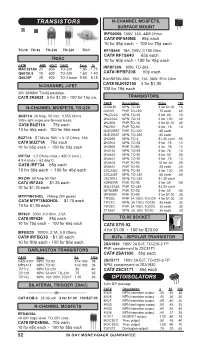

TRANSISTORS TRANSISTORS CAT# Description Price 100 2N2222A NPN, TO-18 2 for $1.50 .60 2N2906 PNP, TO-18 2 for $1.00 .35 PN2907 PNP, TO-92 5 for .75 .10 2N3055 NPN, TO-3 $2.35 each 2.00 TO-18 TO-92 TO-202 TO-218 TO-220 TO-3 2N3904 NPN, TO-92 5 for .75 .13 2N3906 PNP, TO-92 5 for .75 .13 TRIAC 2N4124 NPN, TO-92 5 for .75 .13 2N4400 NPN, TO-92 5 for .50 .08 CAT# AMP VOLT CASE Each 10 2N4401 NPN, TO-92 5 for .75 .13 Q6025P 25 600 TO-3 base 3.00 2.50 2N4403 PNP, TO-92 10 for .80 .05 2N5401 PNP, TO-92 .25 each .20 SCR 2N5416 PNP, TO-39 $1.95 each 2SC2352 NPN, TO-92 3 for 1.00 .29 8A 200V TO-202 SCR. 200 uA gate current. 2SC3457 NPN, TO-220 .65 each .50 CAT# S306B1 45¢ each • 10 for 40¢ each 2SC5511 NPN, TO-220 .95 each .75 BC556B PNP, TO-92 5 for $1.00 Gate sensitive SCR, Teccor T106F41. D33D30 NPN, TO-92 5 for $1.00 .16 Off-state voltage: 50V. Gate trigger, D45H5 PNP, TO-220 .75 each .65 Gate: 200uA 3-pin DIP package. KSP8599 PNP, TO-92 5 for .50 .08 CAT# T106F41 2 for $1.00 MJL1302A PNP, TO-264 $3.00 each MPS8599 PNP, TO-92 5 for .50 .08 N-CHANNEL J-FET PN2222A NPN, TO-92 5 for .80 .15 TIP31C NPN, 3A 100V, TO220 .45 each .35 30V 350MW. -

TRANSISTORS N-CHANNEL MOSFETS, SURFACE MOUNT IRF540NS 100V, 33A, 44M Ohms

TRANSISTORS N-CHANNEL MOSFETS, SURFACE MOUNT IRF540NS 100V, 33A, 44M Ohms. CAT# IRF540NS 95¢ each 10 for 85¢ each • 100 for 70¢ each TO-18 TO-92 TO-218 TO-220 TO-3 RF1S640 18A, 200V, 0.180 Ohm CAT# RF1S640 65¢ each TRIAC 10 for 60¢ each • 100 for 45¢ each CAT# AMP VOLT CASE Each 10 900v. TO-263. MAC223A8 25 600 TO-220 1.85 1.75 IRFBF20S Q6015L5 15 600 TO-220 1.60 1.40 CAT# IRFBF20S 60¢ each Q6025P 25 600 TO-3 base 5.50 5.15 BUK92150-55A. 55V, 11A, 36W, 97m Ohm. CAT# BUK92150 4 for $1.00 N-CHANNEL J-FET 100 for 19¢ each 30V 350MW. TO-92 package. CAT# 2N5638 5 for $1.00 • 100 for 15¢ ea. TRANSISTORS CAT# Description Price 100 N-CHANNEL MOSFETS, TO-220 D33D30 NPN, TO-92 5 for $1.00 .16 D45H5 PNP, TO-220 .75 each .65 BUZ11A 26 Amp, 50 Volt, 0.055 Ohms. PN2222A NPN, TO-92 5 for .80 .15 With right-angle pre-formed leads. 2N2222A NPN, TO-18 2 for 1.00 .40 2N2906 PNP, TO-18 2 for $1.00 .35 CAT# BUZ11A 75¢ each PN2907 PNP, TO-92 5 for .75 .10 10 for 65¢ each 100 for 55¢ each MJE2955T PNP, TO-220 .65 each MJE3055T NPN, TO-220 .65 each BUZ71A ST Micro. 50V, < 0.12 Ohms , 13 A. 2N3055 NPN, TO-3 $1.25 each .95 CAT# BUZ71A 75¢ each 2N3904 NPN, TO-92 5 for .75 .13 10 for 65¢ each • 100 for 53¢ each 2N3906 PNP, TO-92 5 for .75 .13 2N4124 NPN, TO-92 5 for .75 .13 2N4400 NPN, TO-92 5 for .50 .08 IRF734 1.2 Ohms (max.). -

Linear Voltage Regulators

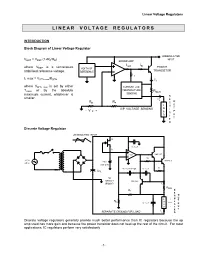

Linear Voltage Regulators LINEAR VOLTAGE REGULATORS INTRODUCTION Block Diagram of Linear Voltage Regulator UNREGULA TED V = V (1+R /R ) INPUT OUT REF F E ERROR AMP I I OA B POWER where VREF is a temterature VOLTAGE stabilised reference voltage. REFERENCE TRANSISTOR I T IL max = VSEN max/RSEN I L where VSEN max is set by either CURRENT and TEMPERA TURE TJmax or by the absolute RSEN SENSING maximum current, whichever is R smaller. I E L O RE RF G U L U T O/P VOLTAGE SENSING O L - V + P F A A U D T T E D Discrete Voltage Regulator UNREGULATED INPUT D 0,1 µF S LF351 2N5337 10k 110V 2N3055 7,5V 60Hz 500 mW 47 to 1000 pF 0,1 µF 1k CFIL TO CI RCUI T 2N2222 GR OU N D I L RSEN R RF E G O U L + U T RE O L 0,1 µF Vout A A P D - T U E T SEPA RA TE GROUND FOR LOA D I L D Discrete voltage regulators generally provide much better performance than IC regulators because the op amp used has more gain and because the power transistor does not heat up the rest of the circuit. For most applications, IC regulators perform very satisfactorily. -1- Linear Voltage Regulators EFFICIENCY OF LINEAR REGULATORS Linear regulators are easier to design and generally less expensive but waste more power because the power elements (transistors) operate in their active or linear mode. Switching regulators are more complex and more difficult to design but are more power efficient because their power elements (transistors) are switched ON and OFF alternately and consume very little power. -

National Semiconductor Voltage Regulator Handbook 1980

CD 09O VOLTAGE REGULATOR HANDBOOK NATIONAL SEMICONDUCTOR 37 Loverock Road Reading Berkshire RG3 1ED Telephone (0734) 585171 Telex 848370 Celdis Electronic Distributed Speddisto Art ive Components I>ivi*k>n HW VOLTAGE REGULATOR HANDBOOK NATIONAL SEMICONDUCTOR Contributors: Nello Sevastopoulos Jim Sherwin Dennis Bonn George Cleveland James E. Solomon 'National Semiconductor Corporation 2900 Semiconductor Drive, Santa Clara, CalHornla 96051 [4M| 737-5000(TWX (910) 339-92J0 dmertWd: Hatloijl aoafl not «Burri* iny [•itmnslbHlny lor uta at my circuitry »ny no elrsuM pit*nl lictnut *r* implied, «no Nit>snil reimnS the fin.ni. si Sitm wiihaul nolie* to Ch*rv|}t »«> clrcuilry. nw Table of Contents 1.0 Introduction ...... ,,,......,..,, 1-1 1.1 How to Use this Book ., , 1-1 1.2 Features of On-Card Regulation 1-1 1.3 Fixed Voltage 3-Terminal Regulator Description 1-4 1.4 Comparison, Fixed Voltage 3-Terminal vs Variable Voltage Regulators by Application 1-4 2.0 Data Sheet Summary 2*1 3.0 Product Selection Procedures . .3-1 4.0 Heat Flow & Thermal Resistance .4-1 5.0 Selection of Commercial Heat Sink 5-1 6.0 Custom Heat Sink Design ,6-1 7.0 Applications Circuits and Descriptive Information 7-1 7.1 Positive Regulators .7-1 7.2 Negative Regulators 7-5 7.3 Dual Tracking Regulators 7-6 7.4 Adjustable Voltage Regulators 7-20 7.5 Automotive Applications 7*32 8.0 Power Supply Design 8-1 8.1 Scope , ,. , 8-1 8.2 Capacitor Selection 8-4 8.3 Diode Selection 8-4 9.0 Appendix , . -

2N3055 Datasheet Pdf

2n3055 Datasheet Pdf 1 / 6 2n3055 Datasheet Pdf 2 / 6 3 / 6 Maximum Ratings[edit]The maximum collector-to-emitter voltage for the 2N3055, like other transistors, depends on the resistance path the external circuit provides between the base and emitter of the transistor; with 100 ohms a 70 volt breakdown rating, VCER, and the Collector-Emitter Sustaining voltage, VCEO(sus), is given by ON Semiconductor. 1. datasheet 2. datasheet view access 3. datasheet view 2N3055 SILICON NPN TRANSISTOR SGS-THOMSONPREFERRED SALESTYPE DESCRIPTION The 2N3055 is a silicon epitaxial-base NPN transistor in JedecTO-3 metalcase.. 1Specifications2HistorySpecifications[edit]The exact performance characteristics depend on the manufacturer and date; before the move to the epitaxial base version in the mid-1970s the fT could be as low as 0.. 5 MHzPackaged in a TO-3 case style, it is a 15 amp, 60 volt (or more, see below), 115 watt power transistor with a β (forward current gain) of 20 to 70 at a collector current of 4 A (this may be 100 to 200 when testing using a multimeter[6]).. INTERNAL SCHEMATIC DIAGRAM October1995 ABSOLUTE MAXIMUM RATINGS Symbol 21 rows 2N3055 Datasheet, 2N3055 PDF, 2N3055 Data sheet, 2N3055 manual, 2N3055 pdf, 2N3055. datasheet datasheet, datasheet or data sheet, datasheet bc548, datasheet atmega328p, datasheet arduino uno, datasheet 1n4007, datasheetcatalog, datasheet esp32, datasheet lm317, datasheet lm358, datasheet view, datasheet pdf, datasheet view access, datasheet meaning, datasheets for datasets, datasheet 360 3utools Latest Version Download For Windows 7 32 Bit [1] Its numbering follows the JEDEC standard [2] It is a transistor type of enduring popularity. -

IC Sockets & Transistors

IC Sockets & Transistors .050" (1.27mm) Pitch SIMM Sockets Transistors (Continued) DWeb Code: FEN • 72 positions • Left polarization Order in multiples of 10 Y h @ Ic) • Contact: phosphor bronze Part No. Mfr. Product No. Pkg. Desc. Vceo Min. ( FE 1 10 100 • PCB retention: press-fit plastic peg 669791 783498 FSC 2N4401TAR TO-92 NPN 40 20 @ .1mA ...... $.06 $.05 • Contact plating (plating thickness): gold (0.76µm; 30µ"); tin/lead (5µm; 200µ") 211490 ! 2N4923 TO-225 NPN — 80 @ 1A......... .45 .39 .35 669791: Right polarization; gold contact plating 2125608 MOT SPS4942(9568) TO-92 NPN 30 60 @ .5A ......... .05 .04 Part No. Mfr. Part No. Description 1 10 1201380 FSC PN4953 TO-92 NPN 30 150 @ .01A ....... .05 .04 Semiconductors 669791 15-82-0778R Vertical .......................................................... $1.95 $1.49 310666 ! 2N5038 TO-3 NPN 150 20 @ 12A .... 4.75 4.49 3.95 ! 670784 15-82-1538R Right angle ...................................................... 1.95 1.49 140373 2N5179 TO-72 NPN 12 25 @ .003A . 1.09 .99 .89 1945081 FSC 2N5306 TO-92 NPN 25 7000 @ .002A ..... .09 .07 Transistors DWeb Code: FEN 924300 ST 2N6284R TO-3/2 NPN 100 750 @ 10A .... 3.25 2.95 2.59 140353 ! 2N6488 TO-220AB NPN 80 20 @ 5A ........ .29 .25 .15 Order in multiples of 10 1945031 FSC MPS6515 TO-92 NPN 25 250 @ .002A ..... .05 .03 Y h @ Ic) Part No. Mfr. Product No. Pkg. Desc. Vceo Min. ( FE 1 10 100 194618 ! 2N6547 TO-3 NPN 400 12 @ 5A ...... 4.49 4.25 3.75 26462 ! MPSA06 TO-92 NPN 80 100k @ .01A ...... -

Bipolar Junction Transistors

Module www.learnabout-electronics.org 3 Bipolar Junction Transistors Module 3.1 Bipolar Junction Transistors What you’ll learn in Module 3 What are BJTs? Section 3.1 Bipolar Junction Transistors (BJTs). • BJT circuit symbols. • BJT output transistors. • Complementary pairs. • Small signal BJTs. • Common transistor packages. Section 3.2 Making Transistors. • Germanium Alloy Diffused Transistors. Fig. 3.1.1 Bipolar Junction Transistors • Silicon Planar Transistors. Bi-polar transistors are amongst the most widely used Section 3.3 How a BJT Works. devices for amplification of all types of electrical • Doping. signals in discrete circuits, i.e. circuits made from individual components rather than integrated circuits • Current Flow. (I/Cs). BJTs are also used in circuits together with I/Cs Section 3.4 BJT Animation. , since it is often more practical to use discrete output • Base bias transistors where a higher power output is needed than • Collector current the I/C can provide. For example an integrated circuit may carry out all of the processing of the signals in a • Junction potential system, but then pass the processed signal to a single Section 3.5 Current Gain. discrete transistor or a pair of matched transistors for • Bipolar Transistor Characteristics power amplification to drive a loudspeaker or other output device. It is also often more convenient to use a • Transfer. discrete transistor for an individual circuit within a • Input. larger system, for which I/Cs are not readily available. • Output. • Mutual. Section 3.6 Transistor Connections. • Common Emitter. • Common Collector. • Common Base. Section 3.7 Bipolar Transistor Quiz. • Check your understanding of Bipolar Transistors. -

Series for Design Engineers

Series for Design Engineers Brown Power Supply Cookbook, Second Edition Dostál Operational Amplifiers, Second Edition Dye Radio Frequency Transistors: Principles and Practical Applications, Second Edition Gates Energy Products Rechargeable Batteries Applications Handbook Hickman Electronic Circuits, Systems and Standards: The Best of EDN Marston Newnes Electronic Circuits Pocket Book Marston Integrated Circuit and Waveform Generator Handbook Marston Diode, Transistor and FET Circuits Manual Pease Troubleshooting Analog Circuits Sinclair Passive Components Williams Analog Circuit Design: Art, Science and Personalities Power Supply Cookbook Second Edition Marty Brown Boston Oxford Johannesburg Melbourne New Delhi Newnes is an imprint of Butterworth–Heinemann. Copyright © 2001 by Butterworth–Heinemann A member of the Reed Elsevier group All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Recognizing the importance of preserving what has been written, Butterworth–Heinemann prints its books on acid-free paper whenever possible. Butterworth–Heinemann supports the efforts of American Forests and the Global ReLeaf program in its campaign for the betterment of trees, forests, and our environment. Library of Congress Cataloging-in-Publication Data Brown, Marty. Power supply cookbook / Marty Brown.—2nd ed. p. cm. Includes bibliographical references and index. ISBN 0-7506-7329-X 1. Electric power supplies to apparatus—Design and construction. 2. Power electronics. 3. Electronic apparatus and appliances—power supply. I. Title. TK7868.P6 B76 2001 621.381¢044—dc21 00-050054 British Library Cataloguing-in-Publication Data A catalogue record for this book is available from the British Library. -

Orcad Pspice Library List

Release 9.2, 31 May 2000 Copyright © 1985-2000 Cadence Design Systems, Inc. The PSpice Library List What is the Library List? The PSpice Library List is an online listing of all of the parts contained in the libraries that are supplied with PSpice. Every part listed has a corresponding PSpice model. The listings are categorized into the following groups: Analog Digital Mixed Signal General devices General devices General devices Japanese devices TTL devices European devices The listings are divided into columns, like a spreadhseet, and show the following information about each device: Device Type Generic Name Part Name Part Library Mfg. Name Tech Type The type of device The generic or The name of the The name of the The name of the The technology type (transistor, diode, standard industry part in the PSpice PSpice library the manufacturer of the of the device (TTL, etc.). name of the device. library. part is stored in. device. ECL, etc.), where applicable. Each group is arranged alphabetically by Device Type. How do I use the Library List? Accessing a library To access a particular library list, simply click on the bookmark for the group and device type you are interested in. (Bookmarks are shown in the left-hand column of this Acrobat Reader page. If you do not see the left-hand column for the bookmarks in Acrobat Reader, choose Bookmarks and Page from the View menu.) Searching for a name To search for a specific part name, library name, or any other text, use Acrobat Reader's built-in Find function. -

Chapter 11 Alternating-Current Power the Text for the Theory Portion of This Chapter Was Written by Ken Stuart, W3VVN

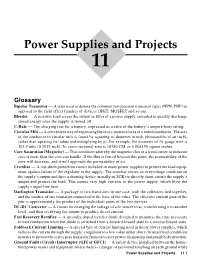

Power Supplies and Projects 11 Glossary Bipolar Transistor — A term used to denote the common two junction transistor types (NPN, PNP) as opposed to the field effect families of devices (JFET, MOSFET and so on). Bleeder — A resistive load across the output or filter of a power supply, intended to quickly discharge stored energy once the supply is turned off. C-Rate — The charging rate for a battery, expressed as a ratio of the battery’s ampere-hour rating. Circular Mils — A convenient way of expressing the cross-sectional area of a round conductor. The area of the conductor in circular mils is found by squaring its diameter in mils (thousandths of an inch), rather than squaring its radius and multiplying by pi. For example, the diameter of 10-gauge wire is 101.9 mils (0.1019 inch). Its cross-sectional area is 10380 CM, or 0.008155 square inches. Core Saturation (Magnetic) — That condition whereby the magnetic flux in a transformer or inductor core is more than the core can handle. If the flux is forced beyond this point, the permeability of the core will decrease, and it will approach the permeability of air. Crowbar — A last-ditch protection circuit included in many power supplies to protect the load equip- ment against failure of the regulator in the supply. The crowbar senses an overvoltage condition on the supply’s output and fires a shorting device (usually an SCR) to directly short-circuit the supply’s output and protect the load. This causes very high currents in the power supply, which blow the supply's input-line fuse. -

Products Catalog Index

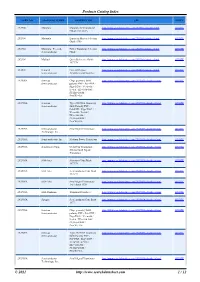

Products Catalog Index PART NO. MANUFACTURER DESCRIPTION URL PRICE 2N2904 Motorola Motorola Semiconductor http://www.searchdatasheet.com/2N2904-datasheet.html QUOTE Datasheet Library 2N2904 Motorola European Master Selection http://www.searchdatasheet.com/2N2904-datasheet.html QUOTE Guide 1986 2N2904 Motorola / Freescale Power Transistor Selection http://www.searchdatasheet.com/2N2904-datasheet.html QUOTE Semiconductor Guide 2N2904 Mullard Quick Reference Guide http://www.searchdatasheet.com/2N2904-datasheet.html QUOTE 1977/78 2N2904 National General Purpose http://www.searchdatasheet.com/2N2904-datasheet.html QUOTE Semiconductor Amplifiers and Switches 2N2905A Semicoa Chip: geometry 0600 http://www.searchdatasheet.com/2N2905A-datasheet.html QUOTE Semiconductor polarity PNP - Pol=PNP / Pkg=TO39 / Vceo=60 / Ic=0.6 / Hfe=100-300 / fT(Hz)=200M / Pwr(W)=0.6 2N2905A Semicoa Type 2N2905A Geometry http://www.searchdatasheet.com/2N2905A-datasheet.html QUOTE Semiconductor 0600 Polarity PNP - Pol=PNP / Pkg=TO39 / Vceo=60 / Ic=0.6 / Hfe=100-300 / fT(Hz)=200M / Pwr(W)=0.6 2N2905A Semiconductor Small Signal Transistors http://www.searchdatasheet.com/2N2905A-datasheet.html QUOTE Technology, Inc. 2N2905A Semiconductors, Inc. Medium Power Transistors http://www.searchdatasheet.com/2N2905A-datasheet.html QUOTE 2N2905A Semitronics Corp. Metal Can Transistors - http://www.searchdatasheet.com/2N2905A-datasheet.html QUOTE Silicon Small Signal Transistors 2N2905A SGS-Ates Shortform Data Book http://www.searchdatasheet.com/2N2905A-datasheet.html QUOTE 1977/78 -

Bipolar Junction Transistor Theory This Worksheet and All Related Files Are

Bipolar junction transistor theory This worksheet and all related files are licensed under the Creative Commons Attribution License, version 1.0. To view a copy of this license, visit http://creativecommons.org/licenses/by/1.0/, or send a letter to Creative Commons, 559 Nathan Abbott Way, Stanford, California 94305, USA. The terms and conditions of this license allow for free copying, distribution, and/or modification of all licensed works by the general public. Resources and methods for learning about these subjects (list a few here, in preparation for your research): 1 Question 1 Match the following bipolar transistor illustrations to their respective schematic symbols: NPN P N P file 00446 Answer 1 NPN P N P Follow-up question: identify the terminals on each transistor schematic symbol (base, emitter, and collector). Notes 1 Be sure to ask your students which of these transistor symbols represents the ”NPN” type and which represents the ”PNP” type. Although it will be obvious to most from the ”sandwich” illustrations showing layers of ”P” and ”N” type material, this fact may escape the notice of a few students. It might help to review diode symbols, if some students experience difficulty in matching the designations (PNP versus NPN) with the schematic symbols. 2 Question 2 If we were to compare the energy diagrams for three pieces of semiconducting material, two ”N” type and one ”P” type, side-by-side, we would see something like this: N PN Conduction band Ef Ef "Acceptor" holes "Donor" electrons "Donor" electrons Ef Valence band Increasing electron energy The presence of dopants in the semiconducting materials creates differences in the Fermi energy level (Ef ) within each piece.