LM3445 TRIAC Dimmable Offline LED Driver Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

UCC27531 35-V Gate Driver for Sic MOSFET Applications (Rev. A)

(1) Application Report SLUA770A–March 2016–Revised May 2018 UCC27531 35-V Gate Driver for SiC MOSFET Applications Richard Herring........................................................................................... High Power Driver Solutions ABSTRACT SiC MOSFETs are gaining popularity in many high-power applications due to their significant switching performance advantages. SiC MOSFETs are also available with attractive voltage ratings and current capabilities. However, the characteristics of SiC MOSFETs require consideration of the gate-driver circuit to optimize the switching performance of the SiC device. Although SiC MOSFETs are not difficult to drive properly, many typical MOSFET drivers may result in compromised switching speed performance. The UCC27531 gate driver includes features and has operating parameters that allow for driving SiC power MOSFETs within the recommended optimum drive configuration. This application note reviews the characteristics of SiC MOSFETs and how to drive them to achieve the performance improvement that SiC can bring at the system level. The features of UCC27531 to achieve optimal performance of SiC are explained and results from a demonstration circuit are provided. 1 Introduction In the past, the majority of applications such as uninterruptible power supplies (UPS), photovoltaic (PV) inverters, and motor drive have utilized IGBTs for the power devices due to the combination of high- voltage ratings exceeding 1 kV and high current capability. Usable switching frequency of IGBTs has typically been limited to 20–30 kHz, due to the high turnoff losses caused by the long turnoff current tail. Design comparisons have shown that SiC MOSFET designs can operate at considerably higher switching frequency and achieve the same or better efficiency. Although the device cost of the SiC MOSFETs are higher than the equivalent IGBTs, the significant savings in transformer, capacitor, and enclosure size results in a lower system cost. -

Egan® Ics for Low Voltage DC-DC Applications Egan® Ics for Low Voltage DC-DC Applications EFFICIENT POWER CONVERSION

APPLICATION NOTE: AN025 eGaN® ICs for Low Voltage DC-DC Applications eGaN® ICs for Low Voltage DC-DC Applications EFFICIENT POWER CONVERSION Michael de Rooij, Ph.D., Vice President of Applications Engineering , Yuanzhe Zhang, Ph.D., Director of Applications Engineering eGaN® FETs from EPC have repeatedly demonstrated higher performance over Monolithic integration of the gate driver to the MOSFET counterparts in many applications [1]. The lateral structure and material FET offers the lowest possible common source properties of eGaN FETs make it possible to monolithically integrate a number of FETs inductance (CSI) as it is moved to within the as demonstrated by products such as the EPC2107 [2]. The next phase in the eGaN IC structure. Furthermore the gate driver has been optimized for the FET being driven to offer FET and IC evolution includes gate driver integration. Integrating the gate driver with maximum performance under any operating the FET offers a number of additional advantages over discrete gate driver and FET condition. These benefits are on top of the well- solutions such as extremely low common source inductance, matched gate driver established low capacitance and inductance, and to FET, and ease of design. All the traditional eGaN FET benefits such as significantly zero reverse recovery charge (QRR) that enable lower capacitance and inductance with zero reverse recovery charge (QRR) in a smaller efficient operation at high switching frequencies even under hard switching conditions. The key footprint for a given on-resistance (RDS(on)) than comparable MOSFETs are retained. However, the combined effect of the new characteristics and benefits ensures an ever characteristics of the EPC2112 are given in table 1. -

Resonant Gate-Drive Circuits for High-Frequency Power Converters

Resonant Gate-Drive Circuits for High-Frequency Power Converters A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy By Hur Jedi B. S., University of Baghdad, Baghdad, Iraq, 2003 M. S., University Putra Malaysia, Selangor, Malaysia, 2010 2018 Wright State University WRIGHT STATE UNIVERSITY GRADUATE SCHOOL November 16, 2018 I HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER MY SUPERVISION BY Hur Jedi ENTITLED Resonant Gate-Drive Circuits for High-Frequency Power Converters BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy. Marian K. Kazimierczuk, Ph.D. Dissertation Director Arnab Shaw, Ph.D. Director, Electrical Engineering Ph.D. Program Barry Milligan, Ph.D. Interim Dean of the Graduate School Committee on Final Examination Marian K. Kazimierczuk, Ph.D. Ray Siferd, Ph.D. Henry Chen, Ph.D. Saiyu Ren, Ph.D. Yan Zhuang, Ph.D. Abstract Jedi, Hur. Ph.D., Electrical Engineering Ph.D. Program, Department of Electrical Engineering, Wright State University, 2018. Resonant Gate-Drive Circuits for High- Frequency Power Converters. The development trend of power converters motivates the pursuit with high den- sity, high efficiency, and low cost. Increasing the frequency can improve the power density and lead to small passive elements and a fast dynamic response. Each one of these power converters must be driven by a gate-drive circuit to operate efficiently. Conventional gate-drivers are used up to frequencies of about 5 MHz and suffer from switching losses. Therefore, the development of switch-mode power supplies (SMPS) operating at high frequencies requires high-speed gate drivers. -

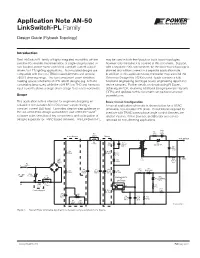

Application Note AN-50 Linkswitch-PL Family

Application Note AN-50 LinkSwitch-PL™ Family Design Guide (Flyback Topology) Introduction The LinkSwitch-PL family of highly integrated monolithic off-line may be used in both the flyback or buck-boost topologies switcher ICs enables implementation of single-stage isolated or however only the flyback is covered in this document. Support, non-isolated, power factor corrected, constant current output with a separate PIXls spreadsheet, for the buck-boost topology is drivers for LED lighting applications. Non-isolated designs are planned and will be covered in a separate application note. compatible with low cost TRIAC based dimmers and provide In addition to this application note, the reader may also find the >300:1 dimming range. The low component count simplifies Reference Design Kits (RDKs) useful. Each contains a fully meeting space constraints of LED retrofit designs (e.g. A19 and functional engineering prototype board, engineering report and candelabra lamp sizes) while the >0.9 PF, low THD and harmonic device samples. Further details on downloading PI Expert, input currents allows a single driver design to be used worldwide. obtaining an RDK, reviewing additional Design Example Reports (DERs) and updates to this document can be found at www. Scope powerint.com. This application note is intended for engineers designing an Basic Circuit Configuration isolated or non-isolated AC to DC power supply driving a A typical application schematic is shown below for a TRIAC constant current LED load. It provides step-by-step guidance on dimmable, non-isolated LED driver. Circuit blocks required for the use of the PIXls design spreadsheet, part of the PI Expert™ interface with TRIAC based phase angle control dimmers are software suite, selection of key components and optimization of labeled Passive, Active Damper, and Bleeder and can be designs especially for TRIAC based dimmers. -

Igbts (Insulated Gate Bipolar Transistor) Application Note

IGBTs (Insulated Gate Bipolar Transistor) Application Note IGBTs (Insulated Gate Bipolar Transistor) Description This document describes the basic structures, ratings, and electrical characteristics of IGBTs. It also provides usage considerations for IGBTs. © 2018 1 2018-09-01 Toshiba Electronic Devices & Storage Corporation IGBTs (Insulated Gate Bipolar Transistor) Application Note Table of Contents Description ............................................................................................................................................ 1 Table of Contents ................................................................................................................................. 2 1. Device structure and characteristics of IGBTs ............................................................................. 6 1.1. Basic structure of the IGBT ................................................................................................................ 6 1.2. Comparison of different types of transistors (bipolar transistors, MOSFETs, and IGBTs) ....... 8 2. Different types of IGBTs and their structures ............................................................................ 11 2.1. Gating structures ................................................................................................................................11 2.2. IGBT classification based on the vertical structure ...................................................................... 12 2.2.1. Punch-through (PT) IGBTs ................................................................................................................12 -

Designing LED Drivers for the Challenges of Phase Cut Dimmers

ON Semiconductor Is Now To learn more about onsemi™, please visit our website at www.onsemi.com onsemi and and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba “onsemi” or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided “as-is” and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. “Typical” parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. -

The Principles of Dimming Leading Edge Dimming – Triac and Thyristor

The Principles Of Dimming An artificial light source such as a lamp or one or more lamps in a fitting (luminaire) will be specified for a purpose. Often this purpose will need a lot of light but may be too much at other times. This is nothing new, candle lamps used mechanical screens and oil lamps adjustable wicks. Aesthetic, artistic, mood setting, visual comfort, or energy saving are all valid reasons for changing lighting levels, or in other words dimming the lamps. Dimming an electric lamp is achieved by reducing the current and thereby the power to the lamp. Early dimmers used series resistance but this generates a lot of heat and is inefficient. All modern dimmers use semiconductor technology and digital control with typical losses of less than 2% of full load. Mains “chopping” or Phase Control The most widely used form of dimming is phase control. Phase control dimming uses a switching device to “chop” the supply such that only part of each half cycle Normal line voltage, full power for the load of the AC mains supply is applied to the load. For the remaining part the switch is open and no power is applied to the load. The amount of power to the load is therefore determined by the phase angle of the AC supply at which the switching occurs and thereby altering the ratio of off to on time from always open, no power, to allows closed, full power. The switching is synchronised to each half cycle to minimise the visual impact of momentarily turning the lamp off. -

VCSEL Pulse Driver Designs for Tof Applications

Vixar Application Note VCSEL Pulse Driver Designs for ToF Applications 1 Introduction ............................................................................................................................. 2 2 Design Theory ......................................................................................................................... 2 2.1 Schematic Components .................................................................................................... 2 2.2 Design Inductance ............................................................................................................ 3 2.3 Rise and Fall Time ........................................................................................................... 5 2.4 Timing Delay.................................................................................................................... 5 3 Low Power Driver Design ...................................................................................................... 5 4 High Power Driver Design...................................................................................................... 7 4.1 GaN FETs ......................................................................................................................... 7 4.2 Gate Drivers ..................................................................................................................... 7 5 VCSEL Performance .............................................................................................................. 8 6 Conclusions -

Stage Lighting Technician Handbook

The Stage Lighting Technician’s Handbook A compilation of general knowledge and tricks of the lighting trade Compiled by Freelancers in the entertainment lighting industry The Stage Lighting Technician's Handbook Stage Terminology: Learning Objectives/Outcomes. Understanding directions given in context as to where a job or piece of equipment is to be located. Applying these terms in conjunction with other disciplines to perform the work as directed. Lighting Terms: Learning Objectives/Outcome Learning the descriptive terms used in the use and handling of different types of lighting equipment. Applying these terms, as to the location and types of equipment a stagehand is expected to handle. Electrical Safety: Learning Objectives/Outcomes. Learning about the hazards, when one works with electricity. Applying basic safety ideas, to mitigate ones exposure to them in the field. Electricity: Learning Objectives/Outcomes. Learning the basic concepts of what electricity is and its components. To facilitate ones ability to perform the mathematics to compute loads, wattages and the like in order to safely assemble, determine electrical needs and solve problems. Lighting Equipment Learning Objectives/Outcomes. Recognize the different types of lighting equipment, use’s and proper handling. Gain basic trouble shooting skills to successfully complete a task. Build a basic understanding of applying these skills in the different venues that we work in to competently complete assigned tasks. On-sight Lighting Techniques Learning Objectives/Outcomes. Combing the technical knowledge previously gained to execute lighting request while on site, whether in a ballroom or theatre. Approaches, to lighting a presentation to aspects of theatrical lighting to meet a client’s expectations. -

LM3445 Triac Dimmable Offline LED Driver

LM3445 Triac Dimmable Offline LED Driver February 19, 2010 LM3445 Triac Dimmable Offline LED Driver General Description Features The LM3445 is an adaptive constant off-time AC/DC buck ■ Triac dim decoder circuit for LED dimming (step-down) constant current controller designed to be com- ■ Application voltage range 80VAC – 277VAC patible with triac dimmers. The LM3445 provides a constant Capable of controlling LED currents greater than 1A current for illuminating high power LEDs and includes a triac ■ dim decoder. The dim decoder allows wide range LED dim- ■ Adjustable switching frequency ming using standard triac dimmers. The high frequency ca- ■ Low quiescent current pable architecture allows the use of small external passive ■ Adaptive programmable off-time allows for constant ripple components. The LM3445 includes a bleeder circuit to ensure current proper triac operation by allowing current flow while the line ■ Thermal shutdown voltage is low to enable proper firing of the triac. A passive No 120Hz flicker PFC circuit ensures good power factor by drawing current di- ■ rectly from the line for most of the cycle, and provides a ■ Low profile 10 pin MSOP Package or 14 pin SOIC constant positive voltage to the buck regulator. Additional ■ Patent pending drive architecture features include thermal shutdown, current limit and VCC un- der-voltage lockout. Applications ■ Retro Fit Triac Dimming ■ Solid State Lighting ■ Industrial and Commercial Lighting ■ Residential Lighting Typical LM3445 LED Driver Application Circuit 30060305 30060301 © 2010 National Semiconductor Corporation 300603 www.national.com Connection Diagrams LM3445 Top View Top View 30060303 10-Pin MSOP NS Package Number MUB10A 30060373 14-Pin SOIC NS Package Number M14A Ordering Information Order Number Spec. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Driving Egantm Transistors for Maximum Performance

Driving eGaNTM Transistors for Maximum Performance Johan Strydom: Director of Applications, Efficient Power Conversion Corporation Alex Lidow: CEO, Efficient Power Conversion Corporation The recent introduction of enhancement mode MOSFET development, silicon has approached GaN transistors (eGaN™) as power MOSFET/ its theoretical limits. In contrast, GaN is young in IGBT replacements in power management its life cycle, and will see significant improvement applications enables many new products that in the years to come. promise to add great system value. In general, an eGaN transistor behaves much like a power MOSFET with a quantum leap in performance, but to extract all of the newly-available eGaN transistor performance requires designers to understand the differences in drive requirements. eGaN Power Transistor Characteristics As with silicon power MOSFETs, applying a positive bias to the gate relative to the source of an eGaN power transistor causes a field effect, which attracts electrons that complete a Figure 1. Theoretical resistance times die area limits of GaN, silicon, and silicon carbide versus voltage. bidirectional channel between the drain and the source. When the bias is removed from the gate, the electrons under it are dispersed into the GaN, Figure of Merit (FOM) recreating the depletion region and, once again, giving it the capability to block voltage. The FOM is a useful method for comparing power devices and has been used by MOSFET To obtain a higher-voltage device, the distance manufactures to show both generational between the drain and gate is increased. Doing improvements and to compare their parts to so increases the on-resistance of the transistor.