IGBT Gate Driver Reference Design for Parallel Igbts with Short-Circuit Protection and External BJT Buffer

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

UCC27531 35-V Gate Driver for Sic MOSFET Applications (Rev. A)

(1) Application Report SLUA770A–March 2016–Revised May 2018 UCC27531 35-V Gate Driver for SiC MOSFET Applications Richard Herring........................................................................................... High Power Driver Solutions ABSTRACT SiC MOSFETs are gaining popularity in many high-power applications due to their significant switching performance advantages. SiC MOSFETs are also available with attractive voltage ratings and current capabilities. However, the characteristics of SiC MOSFETs require consideration of the gate-driver circuit to optimize the switching performance of the SiC device. Although SiC MOSFETs are not difficult to drive properly, many typical MOSFET drivers may result in compromised switching speed performance. The UCC27531 gate driver includes features and has operating parameters that allow for driving SiC power MOSFETs within the recommended optimum drive configuration. This application note reviews the characteristics of SiC MOSFETs and how to drive them to achieve the performance improvement that SiC can bring at the system level. The features of UCC27531 to achieve optimal performance of SiC are explained and results from a demonstration circuit are provided. 1 Introduction In the past, the majority of applications such as uninterruptible power supplies (UPS), photovoltaic (PV) inverters, and motor drive have utilized IGBTs for the power devices due to the combination of high- voltage ratings exceeding 1 kV and high current capability. Usable switching frequency of IGBTs has typically been limited to 20–30 kHz, due to the high turnoff losses caused by the long turnoff current tail. Design comparisons have shown that SiC MOSFET designs can operate at considerably higher switching frequency and achieve the same or better efficiency. Although the device cost of the SiC MOSFETs are higher than the equivalent IGBTs, the significant savings in transformer, capacitor, and enclosure size results in a lower system cost. -

Egan® Ics for Low Voltage DC-DC Applications Egan® Ics for Low Voltage DC-DC Applications EFFICIENT POWER CONVERSION

APPLICATION NOTE: AN025 eGaN® ICs for Low Voltage DC-DC Applications eGaN® ICs for Low Voltage DC-DC Applications EFFICIENT POWER CONVERSION Michael de Rooij, Ph.D., Vice President of Applications Engineering , Yuanzhe Zhang, Ph.D., Director of Applications Engineering eGaN® FETs from EPC have repeatedly demonstrated higher performance over Monolithic integration of the gate driver to the MOSFET counterparts in many applications [1]. The lateral structure and material FET offers the lowest possible common source properties of eGaN FETs make it possible to monolithically integrate a number of FETs inductance (CSI) as it is moved to within the as demonstrated by products such as the EPC2107 [2]. The next phase in the eGaN IC structure. Furthermore the gate driver has been optimized for the FET being driven to offer FET and IC evolution includes gate driver integration. Integrating the gate driver with maximum performance under any operating the FET offers a number of additional advantages over discrete gate driver and FET condition. These benefits are on top of the well- solutions such as extremely low common source inductance, matched gate driver established low capacitance and inductance, and to FET, and ease of design. All the traditional eGaN FET benefits such as significantly zero reverse recovery charge (QRR) that enable lower capacitance and inductance with zero reverse recovery charge (QRR) in a smaller efficient operation at high switching frequencies even under hard switching conditions. The key footprint for a given on-resistance (RDS(on)) than comparable MOSFETs are retained. However, the combined effect of the new characteristics and benefits ensures an ever characteristics of the EPC2112 are given in table 1. -

Resonant Gate-Drive Circuits for High-Frequency Power Converters

Resonant Gate-Drive Circuits for High-Frequency Power Converters A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy By Hur Jedi B. S., University of Baghdad, Baghdad, Iraq, 2003 M. S., University Putra Malaysia, Selangor, Malaysia, 2010 2018 Wright State University WRIGHT STATE UNIVERSITY GRADUATE SCHOOL November 16, 2018 I HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER MY SUPERVISION BY Hur Jedi ENTITLED Resonant Gate-Drive Circuits for High-Frequency Power Converters BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy. Marian K. Kazimierczuk, Ph.D. Dissertation Director Arnab Shaw, Ph.D. Director, Electrical Engineering Ph.D. Program Barry Milligan, Ph.D. Interim Dean of the Graduate School Committee on Final Examination Marian K. Kazimierczuk, Ph.D. Ray Siferd, Ph.D. Henry Chen, Ph.D. Saiyu Ren, Ph.D. Yan Zhuang, Ph.D. Abstract Jedi, Hur. Ph.D., Electrical Engineering Ph.D. Program, Department of Electrical Engineering, Wright State University, 2018. Resonant Gate-Drive Circuits for High- Frequency Power Converters. The development trend of power converters motivates the pursuit with high den- sity, high efficiency, and low cost. Increasing the frequency can improve the power density and lead to small passive elements and a fast dynamic response. Each one of these power converters must be driven by a gate-drive circuit to operate efficiently. Conventional gate-drivers are used up to frequencies of about 5 MHz and suffer from switching losses. Therefore, the development of switch-mode power supplies (SMPS) operating at high frequencies requires high-speed gate drivers. -

Igbts (Insulated Gate Bipolar Transistor) Application Note

IGBTs (Insulated Gate Bipolar Transistor) Application Note IGBTs (Insulated Gate Bipolar Transistor) Description This document describes the basic structures, ratings, and electrical characteristics of IGBTs. It also provides usage considerations for IGBTs. © 2018 1 2018-09-01 Toshiba Electronic Devices & Storage Corporation IGBTs (Insulated Gate Bipolar Transistor) Application Note Table of Contents Description ............................................................................................................................................ 1 Table of Contents ................................................................................................................................. 2 1. Device structure and characteristics of IGBTs ............................................................................. 6 1.1. Basic structure of the IGBT ................................................................................................................ 6 1.2. Comparison of different types of transistors (bipolar transistors, MOSFETs, and IGBTs) ....... 8 2. Different types of IGBTs and their structures ............................................................................ 11 2.1. Gating structures ................................................................................................................................11 2.2. IGBT classification based on the vertical structure ...................................................................... 12 2.2.1. Punch-through (PT) IGBTs ................................................................................................................12 -

VCSEL Pulse Driver Designs for Tof Applications

Vixar Application Note VCSEL Pulse Driver Designs for ToF Applications 1 Introduction ............................................................................................................................. 2 2 Design Theory ......................................................................................................................... 2 2.1 Schematic Components .................................................................................................... 2 2.2 Design Inductance ............................................................................................................ 3 2.3 Rise and Fall Time ........................................................................................................... 5 2.4 Timing Delay.................................................................................................................... 5 3 Low Power Driver Design ...................................................................................................... 5 4 High Power Driver Design...................................................................................................... 7 4.1 GaN FETs ......................................................................................................................... 7 4.2 Gate Drivers ..................................................................................................................... 7 5 VCSEL Performance .............................................................................................................. 8 6 Conclusions -

LM3445 Triac Dimmable Offline LED Driver

LM3445 Triac Dimmable Offline LED Driver February 19, 2010 LM3445 Triac Dimmable Offline LED Driver General Description Features The LM3445 is an adaptive constant off-time AC/DC buck ■ Triac dim decoder circuit for LED dimming (step-down) constant current controller designed to be com- ■ Application voltage range 80VAC – 277VAC patible with triac dimmers. The LM3445 provides a constant Capable of controlling LED currents greater than 1A current for illuminating high power LEDs and includes a triac ■ dim decoder. The dim decoder allows wide range LED dim- ■ Adjustable switching frequency ming using standard triac dimmers. The high frequency ca- ■ Low quiescent current pable architecture allows the use of small external passive ■ Adaptive programmable off-time allows for constant ripple components. The LM3445 includes a bleeder circuit to ensure current proper triac operation by allowing current flow while the line ■ Thermal shutdown voltage is low to enable proper firing of the triac. A passive No 120Hz flicker PFC circuit ensures good power factor by drawing current di- ■ rectly from the line for most of the cycle, and provides a ■ Low profile 10 pin MSOP Package or 14 pin SOIC constant positive voltage to the buck regulator. Additional ■ Patent pending drive architecture features include thermal shutdown, current limit and VCC un- der-voltage lockout. Applications ■ Retro Fit Triac Dimming ■ Solid State Lighting ■ Industrial and Commercial Lighting ■ Residential Lighting Typical LM3445 LED Driver Application Circuit 30060305 30060301 © 2010 National Semiconductor Corporation 300603 www.national.com Connection Diagrams LM3445 Top View Top View 30060303 10-Pin MSOP NS Package Number MUB10A 30060373 14-Pin SOIC NS Package Number M14A Ordering Information Order Number Spec. -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Driving Egantm Transistors for Maximum Performance

Driving eGaNTM Transistors for Maximum Performance Johan Strydom: Director of Applications, Efficient Power Conversion Corporation Alex Lidow: CEO, Efficient Power Conversion Corporation The recent introduction of enhancement mode MOSFET development, silicon has approached GaN transistors (eGaN™) as power MOSFET/ its theoretical limits. In contrast, GaN is young in IGBT replacements in power management its life cycle, and will see significant improvement applications enables many new products that in the years to come. promise to add great system value. In general, an eGaN transistor behaves much like a power MOSFET with a quantum leap in performance, but to extract all of the newly-available eGaN transistor performance requires designers to understand the differences in drive requirements. eGaN Power Transistor Characteristics As with silicon power MOSFETs, applying a positive bias to the gate relative to the source of an eGaN power transistor causes a field effect, which attracts electrons that complete a Figure 1. Theoretical resistance times die area limits of GaN, silicon, and silicon carbide versus voltage. bidirectional channel between the drain and the source. When the bias is removed from the gate, the electrons under it are dispersed into the GaN, Figure of Merit (FOM) recreating the depletion region and, once again, giving it the capability to block voltage. The FOM is a useful method for comparing power devices and has been used by MOSFET To obtain a higher-voltage device, the distance manufactures to show both generational between the drain and gate is increased. Doing improvements and to compare their parts to so increases the on-resistance of the transistor. -

Gate Driver Selection Tutorial

Version 1.1 Gate Drivers Presenter: Bipolar Business Unit Date: November 2018 This presentation contains Diodes proprietary and confidential information Selection and/or Design-in Criteria How many inputs/outputs required from the Gate Driver ? Required Voltage rating Drive current rating Special functions Key external component selection This presentation contains Diodes proprietary and confidential information < Filename > 2 Selection and/or Design-in Criteria How many inputs/output are provided for/by the Gate driver? For the inputs, It depends on the choice of the micro controller and the control algorithm chosen by the designer For 2 inputs, the choice is high-side / low-side gate driver For 1 input, the choice is a half-bridge driver Number of outputs depend on the number of half bridges that require driving How to select the voltage rating? A conservative rule is to pick a voltage rating 3 times the operating voltage, with 1.5 times being a recommended minimum. However, this depends purely on the system requirements and usually set by the designer Gate drivers always work with MOSFET/IGBT, best practise is to match the voltage rating of the chosen MOSFET/IGBT This presentation contains Diodes proprietary and confidential information < Filename > 3 Selection and/or design in criteria How much drive current is required? Information about the required gate charge to raise the gate voltage to the desired level is essential Gate charge information is provided by the MOSFET manufacturer in their datasheet, usually for a gate voltage of 10V Now that we know the required gate charge, we choose the drive current rating depending on the rise and fall times we are targeting. -

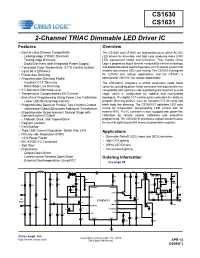

CS1630 CS1631 2-Channel TRIAC Dimmable LED Driver IC

CS1630 CS1631 2-Channel TRIAC Dimmable LED Driver IC Features Overview • Best-in-class Dimmer Compatibility The CS1630 and CS1631 are high-performance offline AC/DC - Leading-edge (TRIAC) Dimmers LED drivers for dimmable and high color rendering index (CRI) - Trailing-edge Dimmers LED replacement lamps and luminaires. They feature Cirrus - Digital Dimmers (with Integrated Power Supply) Logic’s proprietary digital dimmer compatibility control technology • Correlated Color Temperature (CCT) Control System and digital correlated color temperature (CCT) control system that • Up to 85% Efficiency enables two-channel LED color mixing. The CS1630 is designed • Flicker-free Dimming for 120VAC line voltage applications, and the CS1631 is • Programmable Dimming Profile optimized for 230VAC line voltage applications. - Constant CCT Dimming The CS1630/31 integrates a critical conduction mode boost - Black Body Line Dimming converter, providing power factor correction and superior dimmer • 0% Minimum Dimming Level compatibility with a primary-side regulated quasi-resonant second • Temperature Compensated LED Current stage, which is configurable for isolated and non-isolated • End-of-line Programming Using Power Line Calibration topologies. The digital CCT control system provides the ability to - Lower LED Binning Requirement program dimming profiles, such as constant CCT dimming and • Programmable Series or Parallel Two-Channel Output black body line dimming. The CS1630/31 optimizes LED color - Interleaved Output Eliminates Additional Transformer mixing by temperature compensating LED current with an • Programmable Quasi-resonant Second Stage with external NTC. The IC controller is also equipped with power line Constant-current Output calibration for remote system calibration and end-of-line - Flyback, Buck, and Tapped Buck programming. -

Thyristors and Triacs Control Gate Trigger Circuits

1 Lab no. 3 THYRISTORS AND TRIACS CONTROL GATE TRIGGER CIRCUITS 1. Introduction The thyristor is a power semiconductor device with the control terminal called grid or gate (G). The device name comes from the similarity of operation with the gas triode: thiratron transistor. Because the thyristors are mainly used in the controlled rectifier structures, the technical literature calls them as SCR (Semiconductor Controlled Rectifiers) devices. After the series manufacture start in 1957 until the ‘80s of the twentieth century the thyristor was the leader of power semiconductor devices with control electrode. Despite the fact that the thyristor is a half controlled device (through the gate terminal can be only turned on) this switch remains favourite in a wide range of applications because it is robust, can be easily controlled and can operates in high power structures at high voltages and currents with low power conduction losses. To operate, every thyristor require a drive (trigger, control) circuit that provides gate current pulses to induce the on-state. These pulses must have a certain amplitude and duration. The device remains latched in on-state until it is reverse biased. Thus, in forward biased conditions, after the turn-on process, the gate current can be interrupted. Thyristors can be found in various applications such as phase-controlled rectifiers, AC voltage variators, starters, static breakers, cycloconverters, etc. Depending on the requirements, are available on the market several types of thyristors: common thyristors (used in phase-controlled converters at low switching frequency, high voltages and currents), fast thyristors (with a small blocking time), optical thyristors (light-activated through optical fibers), etc. -

Universita' Degli Studi Di Catania

UNIVERSITA’ DEGLI STUDI DI CATANIA DIPARTIMENTO DI INGEGNERIA ELETTRICA, ELETTRONICA ED INFORMATICA Concetta Signorello REDUCTION OF SWITCHING LOSSES IN IGBT POWER MODULES Tesi di Dottorato di Ricerca Internazionale in Energetica XXVII Ciclo Coordinatore: Chiar.mo Prof. Ing. Luigi Marletta Tutor: Chiar.mo Prof. Ing. Mario Cacciato Anno 2014 INDICE INTRODUCTION ................................................................................................ 4 FIRST PART - THEORETICAL ASPECTS CHAPTER 1 - IGBT .............................................................................................. 7 1.1. Controllable Switches ............................................................................. 7 1.2. Architectural and Physical characteristics ........................................... 9 1.2.1. Basic structure ................................................................................. 11 1.2.2. IGBT characteristics ........................................................................ 14 1.2.3. Comparison with Power MOSFET ............................................... 16 1.3. Operating mode ..................................................................................... 17 1.3.1. Block mode operation (OFF state) ................................................ 18 1.3.2. Conduction mode operation (ON state) ...................................... 19 1.4. Operating faults: the Latch-up............................................................. 20 1.5. Switching characteristics .....................................................................