Photobit TECHNOLOGY

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

CMOS Sensors Enable Phone Cameras, HD Video

CMOS Sensors Enable Phone Cameras, HD Video NASA Technology to come of age by the late 1980s. These image sensors already used in CCDs. Using this technique, he measured comprise an array of photodetecting pixels that collect a pixel’s voltage both before and after an exposure. “It’s eople told me, ‘You’re an idiot to work on charges when exposed to light and transfer those charges, like when you go to the deli counter, and they weigh the this,’” Eric Fossum recalls of his early experi- pixel to pixel, to the corner of the array, where they are container, then weigh it again with the food,” he explains. ments with what was at the time an alternate “P amplified and measured. The sampling corrected for the slight thermal charges and form of digital image sensor at NASA’s Jet Propulsion While CCD sensors are capable of producing scientific- transistor fluctuations that are latent in photodetector Laboratory (JPL). grade images, though, they require a lot of power and readout, and it resulted in a clearer image. His invention of the complementary metal oxide extremely high charge-transfer efficiency. These difficulties Because CMOS pixels are signal amplifiers themselves, semiconductor (CMOS) image sensor would go on to are compounded when the number of pixels is increased for they can each read out their own signals, rather than trans- become the Space Agency’s single most ubiquitous spinoff higher resolution or when video frame rates are sped up. ferring all the charges to a single amplifier. This lowered technology, dominating the digital imaging industries and Fossum was an expert in CCD technology—it was why voltage requirements and eliminated charge transfer- enabling cell phone cameras, high-definition video, and JPL hired him in 1990—but he believed he could make efficiency issues. -

Modeling for Ultra Low Noise CMOS Image Sensors

Thèse n° 7661 Modeling for Ultra Low Noise CMOS Image Sensors Présentée le 10 septembre 2020 à la Faculté des sciences et techniques de l’ingénieur Laboratoire de circuits intégrés Programme doctoral en microsystèmes et microélectronique pour l’obtention du grade de Docteur ès Sciences par Raffaele CAPOCCIA Acceptée sur proposition du jury Prof. E. Charbon, président du jury Prof. C. Enz, directeur de thèse Prof. A. Theuwissen, rapporteur Prof. E. Fossum, rapporteur Dr J.-M. Sallese, rapporteur 2020 Ma Nino non aver paura di sbagliare un calcio di rigore, non è mica da questi particolari che si giudica un giocatore, un giocatore lo vedi dal coraggio, dall’altruismo e dalla fantasia. — Francesco De Gregori To my family. Acknowledgements I would like to express my deep gratitude to my thesis advisor, Prof. Christian Enz. His guid- ance and support over the past few years helped me to expand my knowledge in the area of device modeling and sensor design. I am genuinely grateful for having taught me how important is to be methodical and to insist on the detail. My grateful thanks are also extended to Dr. Assim Boukhayma for his contribution and for having introduced me to the fascinating world of image sensors. His help and encouragement over the entire time of my Ph.D. studies daily motivated me to improve the quality of the research. I wish to thank Dr. Farzan Jazaeri for everything he taught me during my Ph.D. His passion for physics and device modeling has been a source of inspiration for the research. I would also like to express my deepest gratitude to Prof. -

CMOS Active Pixel Image Sensors for Highly Integrated Imaging Systems

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 2, FEBRUARY 1997 187 CMOS Active Pixel Image Sensors for Highly Integrated Imaging Systems Sunetra K. Mendis, Member, IEEE, Sabrina E. Kemeny, Member, IEEE, Russell C. Gee, Member, IEEE, Bedabrata Pain, Member, IEEE, Craig O. Staller, Quiesup Kim, Member, IEEE, and Eric R. Fossum, Senior Member, IEEE Abstract—A family of CMOS-based active pixel image sensors Charge-coupled devices (CCD’s) are currently the dominant (APS’s) that are inherently compatible with the integration of on- technology for image sensors. CCD arrays with high fill-factor, chip signal processing circuitry is reported. The image sensors small pixel sizes, and large formats have been achieved and were fabricated using commercially available 2-"m CMOS pro- cesses and both p-well and n-well implementations were explored. some signal processing operations have been demonstrated The arrays feature random access, 5-V operation and transistor- with charge-domain circuits [1]–[3]. However, CCD’s cannot transistor logic (TTL) compatible control signals. Methods of be easily integrated with CMOS circuits due to additional on-chip suppression of fixed pattern noise to less than 0.1% fabrication complexity and increased cost. Also, CCD’s are saturation are demonstrated. The baseline design achieved a pixel high capacitance devices so that on-chip CMOS drive electron- size of 40 "m 40 "m with 26% fill-factor. Array sizes of 28 28 elements and 128 128 elements have been fabricated and ics would dissipate prohibitively high power levels for large characterized. Typical output conversion gain is 3.7 "V/e for the area arrays (2–3 W). -

Print Special Issue Flyer

IMPACT FACTOR 3.576 an Open Access Journal by MDPI Photon-Counting Image Sensors Guest Editors: Message from the Guest Editors Prof. Dr. Eric Fossum Dear Colleagues, [email protected] The field of photon-counting image sensors is advancing Prof. Dr. Nobukazu Teranishi rapidly with the development of various solid-state image [email protected] sensor technologies including single photon avalanche Prof. Dr. Albert Theuwissen detectors (SPADs) and deep-sub-electron read noise CMOS [email protected] image sensor pixels. This foundational platform technology will enable opportunities for new imaging modalities and Dr. David Stoppa instrumentation for science and industry, as well as new [email protected] consumer applications. Papers discussing various photon- Prof. Dr. Edoardo Charbon counting image sensor technologies and selected new [email protected] applications are presented in this all-invited Special Issue. Prof. Dr. Eric R. Fossum Prof. Dr. Edoardo Charbon Deadline for manuscript Dr. David Stoppa submissions: closed (12 February 2016) Prof. Dr. Nobukazu Teranishi Prof. Dr. Albert Theuwissen Guest Editors mdpi.com/si/6076 SpeciaIslsue IMPACT FACTOR 3.576 an Open Access Journal by MDPI Editor-in-Chief Message from the Editor-in-Chief Prof. Dr. Vittorio M.N. Passaro Sensors is a leading journal devoted to fast publication of Dipartimento di Ingegneria the latest achievements of technological developments Elettrica e dell'Informazione and scientific research in the huge area of physical, (Department of Electrical and Information Engineering), chemical and biochemical sensors, including remote Politecnico di Bari, Via Edoardo sensing and sensor networks. Both experimental and Orabona n. -

NASA Technologies Benefit Society

National Aeronautics and Space Administration NASA TECH N OLOGIE S BE N EFI T SOCIE T Y 2010 spinoff SPINOFF Office of the Chief Technologist On the cover: During the STS-128 space shuttle mission, a space-walking astronaut took this photograph of a portion of the International Space Station (ISS) flying high above Earth’s glowing horizon. This year marks the 10th 2010 anniversary of the ISS, and is also a year of beneficial spinoff technologies, as highlighted by the smaller images lined up against the backdrop of space. Spinoff Program Office NASA Center for AeroSpace Information Daniel Lockney, Editor Bo Schwerin, Senior Writer Lisa Rademakers, Writer John Jones, Graphic Designer Deborah Drumheller, Publications Specialist Table of Contents 7 Foreword 9 Introduction 10 International Space Station Spinoffs 20 Executive Summary 30 NASA Technologies Enhance Our Lives on Earth 32 NASA Partnerships Across the Nation 34 NASA Technologies Benefiting Society Health and Medicine Burnishing Techniques Strengthen Hip Implants ...............................................................38 Signal Processing Methods Monitor Cranial Pressure ..........................................................40 Ultraviolet-Blocking Lenses Protect, Enhance Vision ..........................................................42 Hyperspectral Systems Increase Imaging Capabilities ..........................................................44 Transportation Programs Model the Future of Air Traffic Management ......................................................48 -

CMOS Active Pixel Sensor for Digital Cameras: Current State-Of- The-Art

CMOS ACTIVE PIXEL SENSORS FOR DIGITAL CAMERAS: CURRENT STATE-OF-THE-ART Atmaram Palakodety Thesis Prepared for the Degree of MASTER OF SCIENCE UNIVERSITY OF NORTH TEXAS May 2007 APPROVED: Saraju P. Mohanty, Major Professor Elias Kougianos, Co-Major Professor Armin R. Mikler, Committee Member and Graduate Coordinator Krishna Kavi, Chair of the Department of Computer Science and Engineering Oscar Garcia, Dean of College of Engineering Sandra L. Terrell, Dean of the Robert B. Toulouse School of Graduate Studies Palakodety, Atmaram. CMOS Active Pixel Sensor for Digital Cameras: Current State-of- the-Art. Master of Science (Computer Engineering), May 2007, 62 pp., 11 tables, 22 figures, references, 79 titles. Image sensors play a vital role in many image sensing and capture applications. Among the various types of image sensors, complementary metal oxide semiconductor (CMOS) based active pixel sensors (APS), which are characterized by reduced pixel size, give fast readouts and reduced noise. APS are used in many applications such as mobile cameras, digital cameras, Webcams, and many consumer, commercial and scientific applications. With these developments and applications, CMOS APS designs are challenging the old and mature technology of charged couple device (CCD) sensors. With the continuous improvements of APS architecture, pixel designs, along with the development of nanometer CMOS fabrications technologies, APS are optimized for optical sensing. In addition, APS offers very low-power and low-voltage operations and is suitable for monolithic integration, thus allowing manufacturers to integrate more functionality on the array and building low-cost camera-on-a-chip. In this thesis, I explore the current state-of-the-art of CMOS APS by examining various types of APS. -

Engineering Professor Wins Technology and Engineering Emmy | the Dartmouth

2/19/2021 Engineering professor wins Technology and Engineering Emmy | The Dartmouth Support independent student journalism. SUPPORT THE DARTMOUTH $5 Engineering professor wins Technology and Engineering Emmy by Charlie Palsho (https://www.thedartmouth.com/sta/charlie-palsho) | 2/19/21 2:05am (http://www.facebook.com/sharer.php? u=https://www.thedartmouth.com/article/2021/02/engineering-professor-wins- technology-and-engineering-emmy) (http://twitter.com/intent/tweet? url=https://www.thedartmouth.com/article/2021/02/engineering-professor- wins-technology-and-engineering-emmy&text=Engineering professor wins Technology and Engineering Emmy) https://www.thedartmouth.com/article/2021/02/engineering-professor-wins-technology-and-engineering-emmy 1/4 2/19/2021 Engineering professor wins Technology and Engineering Emmy | The Dartmouth Engineering professor Eric Fossum won a Technology and Engineering Emmy for his invention of an image sensor used in cameras, like the one used to take this photo. Source: Courtesy of Eric Fossum Engineering professor Eric Fossum will receive an award at the 72nd Annual Technology and Engineering Emmys for his invention of a sensor now widely used in phone cameras and webcams that even aided in the Mars 2020 rover mission. Fossum’s complementary metal oxide semiconductor active pixel image sensor, or CMOS, converts light signals into digital information while using little battery power and tting easily into a smartphone.The sensor is also less costly than earlier technology. The Technology and Engineering Emmy Awards, which honor innovations in production, recording, transmission or reception of television, will be held virtually in October. Fossum initially created the CMOS while working for NASA at the Jet Propulsion Laboratory in California in the 1990s. -

The Quanta Image Sensor: Every Photon Counts

sensors Review The Quanta Image Sensor: Every Photon Counts Eric R. Fossum *, Jiaju Ma, Saleh Masoodian, Leo Anzagira and Rachel Zizza Thayer School of Engineering at Dartmouth, Dartmouth College, Hanover, NH 03755, USA; [email protected] (J.M.); [email protected] (S.M.); [email protected] (L.A.); [email protected] (R.Z.) * Correspondence: [email protected]; Tel.: +1-603-646-3486 Academic Editor: Nobukazu Teranishi Received: 24 April 2016; Accepted: 2 August 2016; Published: 10 August 2016 Abstract: The Quanta Image Sensor (QIS) was conceived when contemplating shrinking pixel sizes and storage capacities, and the steady increase in digital processing power. In the single-bit QIS, the output of each field is a binary bit plane, where each bit represents the presence or absence of at least one photoelectron in a photodetector. A series of bit planes is generated through high-speed readout, and a kernel or “cubicle” of bits (x, y, t) is used to create a single output image pixel. The size of the cubicle can be adjusted post-acquisition to optimize image quality. The specialized sub-diffraction-limit photodetectors in the QIS are referred to as “jots” and a QIS may have a gigajot or more, read out at 1000 fps, for a data rate exceeding 1 Tb/s. Basically, we are trying to count photons as they arrive at the sensor. This paper reviews the QIS concept and its imaging characteristics. Recent progress towards realizing the QIS for commercial and scientific purposes is discussed. This includes implementation of a pump-gate jot device in a 65 nm CIS BSI process yielding read noise as low as 0.22 e´ r.m.s. -

The Quanta Image Sensor: Every Photon Counts

Dartmouth College Dartmouth Digital Commons Dartmouth Scholarship Faculty Work 8-10-2016 The Quanta Image Sensor: Every Photon Counts Eric Fossum Dartmouth College Jiaju Ma Dartmouth College Saleh Masoodian Dartmouth College Leo Anzagira Dartmouth College Rachel Zizza Dartmouth College Follow this and additional works at: https://digitalcommons.dartmouth.edu/facoa Part of the Engineering Commons Dartmouth Digital Commons Citation Fossum, Eric; Ma, Jiaju; Masoodian, Saleh; Anzagira, Leo; and Zizza, Rachel, "The Quanta Image Sensor: Every Photon Counts" (2016). Dartmouth Scholarship. 3443. https://digitalcommons.dartmouth.edu/facoa/3443 This Article is brought to you for free and open access by the Faculty Work at Dartmouth Digital Commons. It has been accepted for inclusion in Dartmouth Scholarship by an authorized administrator of Dartmouth Digital Commons. For more information, please contact [email protected]. sensors Review The Quanta Image Sensor: Every Photon Counts Eric R. Fossum *, Jiaju Ma, Saleh Masoodian, Leo Anzagira and Rachel Zizza Thayer School of Engineering at Dartmouth, Dartmouth College, Hanover, NH 03755, USA; [email protected] (J.M.); [email protected] (S.M.); [email protected] (L.A.); [email protected] (R.Z.) * Correspondence: [email protected]; Tel.: +1-603-646-3486 Academic Editor: Nobukazu Teranishi Received: 24 April 2016; Accepted: 2 August 2016; Published: 10 August 2016 Abstract: The Quanta Image Sensor (QIS) was conceived when contemplating shrinking pixel sizes and storage capacities, and the steady increase in digital processing power. In the single-bit QIS, the output of each field is a binary bit plane, where each bit represents the presence or absence of at least one photoelectron in a photodetector. -

Pixels? -- a Proposal for a Gigapixel Digital Film Sensor (DFS)* Eric R

What To Do With Sub-Diffraction-Limit (SDL) Pixels? -- A Proposal for a Gigapixel Digital Film Sensor (DFS)* Eric R. Fossum† Abstract This paper proposes the use of sub-diffraction-limit (SDL) pixels in a new solid-state imaging paradigm – the emulation of the silver halide emulsion film process. The SDL pixels can be used in a binary mode to create a gigapixel digital film sensor (DFS). It is hoped that this paper may inspire revealing research into the potential of this paradigm shift. The relentless drive to reduce feature size in microelectronics has continued now for several decades and feature sizes have shrunk in accordance to the prediction of Gordon Moore in 1975. While the “repeal” of Moore’s Law has also been anticipated for some time, we can still confidently predict that feature sizes will continue to shrink in the near future. Using the shrinking-feature-size argument, it became clear in the early 1990’s that the opportunity to put more than 3 or 4 CCD electrodes in a single pixel would soon be upon us and from that the CMOS “active pixel” sensor concept was born. Personally, I was expecting the emergence of the “hyperactive pixel” with in-pixel signal conditioning and ADC. In fact, the effective transistor count in most CMOS image sensors has hovered in the 3-4 transistor range, and if anything, is being reduced as pixel size is shrunk by shared readout techniques. The underlying reason for pixel shrinkage is to keep sensor and optics costs as low as possible as pixel resolution grows. -

Department Lecture Series

Department Lecture Series The Photon-Counting Quanta Image Sensor John H. Krehbiel Sr. Professor Dr. Eric Fossum for Emerging Technologies, Associate Provost, Office of Entrepreneurship & Technology Transfer Dartmouth University Thursday, November 1st 4:30 pm Scott Hall 6142 Abstract: ECE Seminar Committee The talk will begin with a discussion on the CMOS image sensor – its invention, underlying principles, and commercialization. The Quanta Image Sensor (QIS) is a Aswin Sankaranarayanan possible 3rd generation solid-state image sensor technology that is based on photon- [email protected] counting. Primarily focused on scientific and defense applications, it may also be useful for consumer applications. The specialized QIS pixel device and its deep Maysam Chamanzar subelectron read noise will be discussed. The specialized pixel uses ultra-low capacitance rather than avalanche multiplication to achieve single photoelectron [email protected] detection capability. The high frame rate, low power readout will also be described. Recent results on a 1Mpixel QIS with 1.1um pixel pitch, deep sub-electron read noise Swarun Kumar (<0.3e- rms), 1000fps readout at <25mW total power dissipation at room temperature [email protected] will be reported. The device was implemented in a backside-illuminated stacked CMOS image sensor process with room temperature dark current less than 1e-/sec. Giulia Fanti The QIS opens new possibilities for computational imaging by computer scientists [email protected] and others. Bio: Dr. Eric R. Fossum is best known for the invention of the CMOS image sensor “camera-on-a-chip” used in billions of cameras, from smart phones to web cameras to pill cameras and many other applications. -

Fall 2015 the Big Picture: CMOS Image Sensors from Zero to Billions and Beyond Eric Fossum PICTURE Professor of Engineering, Director, Ph.D

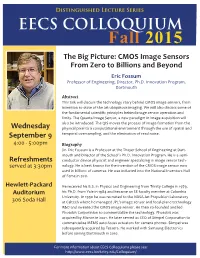

Distinguished Lecture Series EECS COLLOQUIUM Fall 2015 The Big Picture: CMOS Image Sensors From Zero to Billions and Beyond Eric Fossum PICTURE Professor of Engineering, Director, Ph.D. Innovation Program, Dartmouth Abstract This talk will discuss the technology story behind CMOS image sensors, from invention to state of the art ubiquitous imaging. We will also discuss some of the fundamental scientific principles behind image sensor operation and limits. The Quanta Image Sensor, a new paradigm in image acquisition will also be introduced. The QIS moves the process of image formation from the Wednesday physical pixel to a computational environment through the use of spatial and September 9 temporal oversampling, and the elimination of read noise. 4:00 - 5:00pm Biography Dr. Eric Fossum is a Professor at the Thayer School of Engineering at Dart- mouth and Director of the School’s Ph.D. Innovation Program. He is a semi- Refreshments conductor device physicist and engineer specializing in image sensor tech- served at 3:30pm nology. He is best known for the invention of the CMOS image sensor now used in billions of cameras. He was inducted into the National Inventors Hall of Fame in 2011. Hewlett-Packard He received his B.S. in Physics and Engineering from Trinity College in 1979, Auditorium his Ph.D. from Yale in 1984 and became an EE faculty member at Columbia University. In 1990 he was recruited to the NASA Jet Propulsion Laboratory 306 Soda Hall at Caltech where he managed JPL’s image sensor and focal-plane technology R&D and invented the CMOS image sensor.