Intel® Celeron® Dual-Core Processor T1x00 Series

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Dual-Core Intel® Xeon® Processor 3100 Series Specification Update

Dual-Core Intel® Xeon® Processor 3100 Series Specification Update — on 45 nm Process in the 775-land LGA Package December 2010 Notice: Dual-Core Intel® Xeon® Processor 3100 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update. Document Number: 319006-009 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability and a supporting operating system. -

Microcode Revision Guidance August 31, 2019 MCU Recommendations

microcode revision guidance August 31, 2019 MCU Recommendations Section 1 – Planned microcode updates • Provides details on Intel microcode updates currently planned or available and corresponding to Intel-SA-00233 published June 18, 2019. • Changes from prior revision(s) will be highlighted in yellow. Section 2 – No planned microcode updates • Products for which Intel does not plan to release microcode updates. This includes products previously identified as such. LEGEND: Production Status: • Planned – Intel is planning on releasing a MCU at a future date. • Beta – Intel has released this production signed MCU under NDA for all customers to validate. • Production – Intel has completed all validation and is authorizing customers to use this MCU in a production environment. -

Single Board Computer

Single Board Computer SBC with the Intel® 8th generation Core™/Xeon® (formerly Coffee Lake H) SBC-C66 and 9th generation Core™ / Xeon® / Pentium® / Celeron® (formerly Coffee Lake Refresh) CPUs High-performing, flexible solution for intelligence at the edge HIGHLIGHTS CONNECTIVITY CPU 2x USB 3.1; 4x USB 2.0; NVMe SSD Slot; PCI-e x8 Intel® 8th gen. Core™ / Xeon® and 9th gen. Core™ / port (PCI-e x16 mechanical slot); VPU High Speed Xeon® / Pentium® / Celeron® CPUs Connector with 4xUSB3.1 + 2x PCI-ex4 GRAPHICS MEMORY Intel® UHD Graphics 630/P630 architecture, up to 128GB DDR4 memory on 4x SO-DIMM Slots supports up to 3 independent displays (ECC supported) Available in Industrial Temperature Range MAIN FIELDS OF APPLICATION Biomedical/ Gaming Industrial Industrial Surveillance Medical devices Automation and Internet of Control Things FEATURES ® ™ ® Intel 8th generation Core /Xeon (formerly Coffee Lake H) CPUs: Max Cores 6 • Intel® Core™ i7-8850H, Six Core @ 2.6GHz (4.3GHz Max 1 Core Turbo), 9MB Cache, 45W TDP (35W cTDP), with Max Thread 12 HyperThreading • Intel® Core™ i5-8400H, Quad Core @ 2.5GHz (4.2GHz Intel® QM370, HM370 or CM246 Platform Controller Hub Chipset Max 1 Core Turbo), 8MB Cache, 45W TDP (35W cTDP), (PCH) with HyperThreading • Intel® Core™ i3-8100H, Quad Core @ 3.0GHz, 6MB 2x DDR4-2666 or 4x DDR4-2444 ECC SODIMM Slots, up to 128GB total (only with 4 SODIMM modules). Cache, 45W TDP (35W cTDP) Memory ® ™ ® ® ECC DDR4 memory modules supported only with Xeon Core Information subject to change. Please visit www.seco.com to find the latest version of this datasheet Information subject to change. -

"PCOM-B216VG-ECC.Pdf" (581 Kib)

Intel® Arrandale processor based Type II COM Express module support ECC DDR3 SDRAM PCOM-B216VG-ECC with Gigabit Ethernet 204pin ECC DDR3 SODIMM socket ® Intel QM57 ® Intel Arrandale processor FEATURES GENERAL CPU & Package: Intel® 45nm Arrandale Core i7/i5/i3 or Celeron P4505 ® Processor The Intel Arrandale and QM57 platform processor up to 2.66 GHz with 4MB Cache in FC-BGA package with turbo boost technology to maximize DMI x4 Link: 4.8GT/s (Full-Duplex) CPU & Graphic performance Chipset/Core Logic Intel® QM57 ® Intel Arrandale platform support variously System Memory Up to 8GB ECC DDR3 800/1066 SDRAM on two SODIMM sockets powerful processor from ultra low power AMI BIOS to mainstream performance type BIOS Storage Devices SATA: Support four SATA 300 and one IDE Supports Intel® intelligent power sharing Expansion Interface VGA and LVDS technology to reduce TDP (Thermal Six PCI Express x1 Design Power) LPC & SPI Interface High definition audio interface ® ® Enhance Intel vPro efficiency by Intel PCI 82577LM GbE PHY and AMT6.0 Hardware Monitoring CPU Voltage and Temperature technology Power Requirement TBA Support two ECC DDR3 800/1066 SDRAM on Dimension Dimension: 125(L) x 95(W) mm two SODIMM sockets, up to 8GB memory size Environment Operation Temperature: 0~60 °C Storage Temperature: -20~80 °C Operation Humidity: 5~90% I/O ORDERING GUIDE MIO N/A IrDA N/A PCOM-B216VG-ECC ® Standard Ethernet One Intel 82577LM Gigabit Ethernet PHY Intel® Arrandale processor based Type II COM Express module with ECC DDR3 SDRAM and Audio N/A Gigabit Ethernet USB Eight USB ports Keyboard & Mouse N/A CPU Intel® Core i7-610E SV (4M Cache, 2.53 GHz) Support List Intel® Core i7-620LE LV (4M Cache, 2.00 GHz) Intel® Core i7-620UE ULV (4M Cache, 1.06 GHz) Intel® Core i5-520E SV (3M Cache, 2.40 GHz) Intel® Celeron P4505 SV (2M Cache, 1.86 GHz) DISPLAY Graphic Controller Intel® Arrandale integrated Graphics Media Accelerator (Gen 5.75 with 12 execution units) * Specifications are subject to change without notice. -

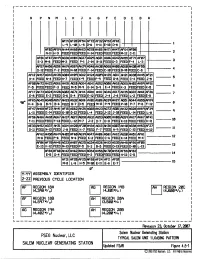

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

HP 250 Notebook PC

HP 250 Notebook PC Our value-priced notebook PC with powerful essentials ideal for everyday computing on the go. HP recommends Windows. Built for mobile use Designed for productivity For professionals on the move, the HP 250 features a Connect with colleagues online and email from the durable chassis that helps protect against the rigors of office or from your favorite hotspots with Wi-Fi the day. CERTIFIED™ WLAN.5 Carry the HP 250 from meeting to meeting. Enjoy great From trainings to sales presentations, view high-quality views on the 15.6-inch diagonal HD2 display, without multimedia and audio right from your notebook with sacrificing portability. preinstalled software and the built-in Altec Lansing speaker. Powered for business Tackle projects with the power of the Intel® third Make an impact with presentations when you connect 2 6 7 generation Core™ i3 or i5 dual-core processors.3 to larger HD displays through the HDMI port. Develop stunning visuals without slowing down your notebook, thanks to Intel’s integrated graphics. 4 HP, a world leader in PCs brings you Windows 8 Pro designed to fit the needs of business. HP 250 Notebook PC HP recommends Windows. SPECIFICATIONS Operating system Preinstalled: Windows 8 644 Windows 8 Pro 644 Ubuntu Linux FreeDOS Processor 3rd Generation Intel® Core™ i5 & i33; 2nd Generation Intel® Core™ i33; Intel® Pentium® 3; Intel® Celeron® 3 Chipset Mobile Intel® HM70 Express (Intel® Pentium® and Celeron® processors) Mobile Intel® HM75 Express (Intel® Core™ i3 and i5 processor) Memory DDR3 SDRAM (1600 MHz) -

Discover, Develop, Deliver with the New Intel® Celeron® Processor

Product Brief The New Intel® Celeron® Processor THE NEW INTEL® CELERON® PROCESSOR DISCOVER DEVELOP DELIVER The new Intel® Celeron® processor built around Intel’s latest microarchitecture and manufactured on Intel’s state-of-the-art 14nm process technology delivers Intel level performance that lets you enjoy entertainment and get your work done. Get performance and value you can count on with an Intel Celeron processor. When paired with the latest Intel® H110 Chipset, Intel Celeron processor-based PCs are an ideal choice for editing photos one minute and watching movies the next, and going from spreadsheets to gaming in a flash. That’s serious processing. Only with Intel Inside®. Product Brief The New Intel® Pentium® MAKES VIDEO CREATION AND TECHNOLOGY The new 14nm Intel Celeron processor brings support for the latest CONVERSION technologies such as DDR4 RAM memory that enables PCs to have a high memory data transfer speed at a lower power as compared to FAST AND EASY DDR3. Intel HD graphics 510 delivers some great graphics with support up to 4K resolution and 3 independent displays. Intel Quick Sync Video technology delivers amazing hardware acceleration that makes video conversion and creation fast and easy. 2 INTEL ® CELERON® PROCESSOR FEATT URES A A GLANCE INTEL ® CELERON® G39XX FEATURES BENEFITS Socket LGA 1151 Dual-Core Runs two independent processor cores in Manufacturing 14nm Processing one physical package at the same frequency. Process Intel® Smart The shared cache is dynamically allocated Processor Base Up to 2.9 GHz Cache to each processor core, based on workload. Frequency on G39XX Efficient last-level cache data usage and instant communication between the core Intel® Smart Cache 2 MB L3 shared and memory. -

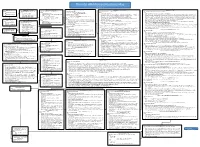

The Intel X86 Microarchitectures Map Version 2.0

The Intel x86 Microarchitectures Map Version 2.0 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • Variant: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128 -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

Demystifying Intel® Ivy Bridge Microarchitecture

Presented at the Research Congress 2013 De La Salle University Manila March 7-9, 2013 DEMYSTIFYING INTEL® IVY BRIDGE MICROARCHITECTURE Roger Luis Uy College of Computer Studies, De La Salle University Abstract: Tick-Tock is a model introduced by Intel ® Corporation in 2006 to show the improvement of its chip development. Every “tick” is the die-shrink of the current microarchitecture, while every “tock” is the new microarchitecture. During the 2nd quarter of 2012, Ivy Bridge Microarchitecture was introduced as the 22-nm die shrink (the “tick”) of the Sandy Bridge microarchitecture (the “tock”). Ivy Bridge-based microprocessors are multi- core processor which place emphasis on minimizing thermal dissipation of processor and providing architecture innovation rather than raw processor speed. Ivy Based-processor comes in three variations – for desktop, for mobile and for server usage. Difference among them lies in the number of core in a processor, the clock frequency, the Thermal Design Power (TDP), the cache memory size and architectural innovations. This research paper will survey the Ivy Based-processor and classify them accordingly. Survey will be based from the Intel’s official website (ark.intel.com). At the same time, independent website (www.cpu-world.com) will be used to counter- check the specifications and to obtain additional information. A freeware software, called CPU-Z (www.cpuid.com) is used to gather information of the processor and provide information such as the name and number of the processor, internal and external clock rate, clock multiplier, supported instructions and cache information. Once the survey and classification is done, we can gain information on which type of applications can be used on which type of microprocessor. -

Ideacentre AIO 520 (22") Intel F0D500C9PB

ideacentre AIO 520 (22") Intel F0D500C9PB Region Microphone www.lenovo.com EET Dual Array This publication was developed for products and Country HDMI services offered in the United States and E.M.E.A Poland HDMI-in countries. Lenovo may not offer the products, services or features discussed in this document in Machine Type WLAN + Bluetooth other countries. Lenovo may withdraw an offering at F0D5 11ac, 1x1 + BT4.0 any time. Information is subject to change without notice. Consult your local representative for information on offerings available in your area. Processor Keyboard / Mouse Lenovo reserves the right to change specifcations or Core i5-8250U (4C, 1.6 / 3.4GHz, 6MB) 2.4G Silver / 2.4G Silver other product information without notice. Lenovo is not responsible for photographic or typographical Graphics Power Supply errors. Lenovo provides this publication “as is” Integrated Intel UHD Graphics 620 90W Adapter without warranty of any kind, either express or implied, including the implied warranties of Chipset Operating System merchantability or ftness for a particular purpose. Intel SoC Platform Windows 10 Home 64 Memory Warranty 8GBx1 2-year, Depot http://psref.lenovo.com Visit psref website for the latest version of Storage Ann Date (mm/yy) Product Specifcations Reference. 1TB 7200rpm 02/18 © Lenovo, 2018. All rights reserved. Optical DVD±RW Media Reader 3-in-1 Note: Country Code "US" is for United States, "++" is for EMEA Display countries (e.g. AD - Saudi, Arabia, AT - Austria, BM - Bulgaria, 21.5" FHD (1920x1080) IPS etc.), "xx" is for EAST countries (e.g. BM - Bulgaria, CX - Hungary, CY - Cyprus, etc.), and "**" is for MEA countries (e.g. -

The Intel X86 Microarchitectures Map Version 2.2

The Intel x86 Microarchitectures Map Version 2.2 P6 (1995, 0.50 to 0.35 μm) 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P5 (1993, 0.80 to 0.35 μm) NetBurst (2000 , 180 to 130 nm) Skylake (2015, 14 nm) Alternative Names: i686 Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: Pentium, 80586, 586, i586 Alternative Names: Pentium 4, Pentium IV, P4 Alternative Names: SKL (Desktop and Mobile), SKX (Server) Series: Pentium Pro (used in desktops and servers) • 16-bit data bus: 8086 (iAPX Series: Series: Series: Series: • Variant: Klamath (1997, 0.35 μm) 86) • Desktop/Server: i386DX Desktop/Server: P5, P54C • Desktop: Willamette (180 nm) • Desktop: Desktop 6th Generation Core i5 (Skylake-S and Skylake-H) • Alternative Names: Pentium II, PII • 8-bit data bus: 8088 (iAPX • Desktop lower-performance: i386SX Desktop/Server higher-performance: P54CQS, P54CS • Desktop higher-performance: Northwood Pentium 4 (130 nm), Northwood B Pentium 4 HT (130 nm), • Desktop higher-performance: Desktop 6th Generation Core i7 (Skylake-S and Skylake-H), Desktop 7th Generation Core i7 X (Skylake-X), • Series: Klamath (used in desktops) 88) • Mobile: i386SL, 80376, i386EX, Mobile: P54C, P54LM Northwood C Pentium 4 HT (130 nm), Gallatin (Pentium 4 Extreme Edition 130 nm) Desktop 7th Generation Core i9 X (Skylake-X), Desktop 9th Generation Core i7 X (Skylake-X), Desktop 9th Generation Core i9 X (Skylake-X) • New instructions: Deschutes (1998, 0.25 to 0.18 μm) i386CXSA, i386SXSA, i386CXSB Compatibility: Pentium OverDrive • Desktop lower-performance: Willamette-128