Freescale Powerpoint Template

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Nile Magazine Article on the Exhibition

The concept of the‘‘ show is bringing together science and art—and where these two disciplines cross. XPLORATIONS: an artist.” She writes that “touring Egypt in the Art of Susan Egypt in 1979 gave me a taste for Osgood is your excuse for a foreign culture rich with layers Ea field trip to Germany! of history and art. In 1985, I This exhibition celebrates and began working as an archaeo- joins the two worlds of Susan logical artist for the Oriental In- Osgood: Art and Archaeology. stitute, and have spent my winters It is showing at the Agyptisches drawing the ancient monuments Museum - Georg Steindorff - and artifacts there ever since—an in the University of Leipzig experience that continues to fuel through until August 27, 2017. and inspire.” Explorations features Susan Many thanks to Rogério Sousa Osgood’s incredibly detailed from the University of Porto in drawings of temple reliefs as an Portugal for his kind permission archaeological illustrator for the to reproduce portions of the Ex- University of Chicago’s Oriental plorations catalogue. Italicised Institute Epigraphic Survey in portions come directly from the Luxor, as well as her colourful catalogue (thank you to Rogério travel sketchbooks and evocative Sousa, W. Raymond Johnson and contemporary fine art. Susan also Susan Osgood), while other text documented a number of the is by the editor to include extra coffins found in KV 63—the first Susan Osgood in Luxor Temple, 2005 information. new tomb to be discovered in the Photo: Mark Chickering Valley of the Kings since German Egyptologist Eberhard Tutankhamun’s in 1922—and Dziobek first met Susan Osgood Explorations showcases the “Copying the exact curve in Egypt while working for the incredible artistry of both Susan that an artist carved German Archaeological Institute. -

Needle Roller and Cage Assemblies B-003〜022

*保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 1 Needle roller and cage assemblies B-003〜022 Needle roller and cage assemblies for connecting rod bearings B-023〜030 Drawn cup needle roller bearings B-031〜054 Machined-ring needle roller bearings B-055〜102 Needle Roller Bearings Machined-ring needle roller bearings, B-103〜120 BEARING TABLES separable Self-aligning needle roller bearings B-121〜126 Inner rings B-127〜144 Clearance-adjustable needle roller bearings B-145〜150 Complex bearings B-151〜172 Cam followers B-173〜217 Roller followers B-218〜240 Thrust roller bearings B-241〜260 Components Needle rollers / Snap rings / Seals B-261〜274 Linear bearings B-275〜294 One-way clutches B-295〜299 Bottom roller bearings for textile machinery Tension pulleys for textile machinery B-300〜308 *保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 2 B-2 *保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 3 Needle Roller and Cage Assemblies *保持器付針状/B001-005_*保持器付針状/B001-005 11/05/24 20:31 ページ 4 Needle roller and cage assemblies NTN Needle Roller and Cage Assemblies This needle roller and cage assembly is one of the or a housing as the direct raceway surface, without using basic components for the needle roller bearing of a inner ring and outer ring. construction wherein the needle rollers are fitted with a The needle rollers are guided by the cage more cage so as not to separate from each other. The use of precisely than the full complement roller type, hence this roller and cage assembly enables to design a enabling high speed running of bearing. -

ARCE Board Bios

BOARD BIOGRAPHIES ARCE 2021 General Member’s Meeting April 24, 2021 CURRENT SLATE DAVID A. ANDERSON David A. Anderson (Nominated Elected Officer) is an associate professor of archaeology at the University of Wisconsin-La Crosse. He received his Ph.D. in anthropology from the University of Pittsburgh in 2006. Since 1996 he has been the director of the El-Mahâsna Archaeological Project. His research focuses on the origins of Egyptian civilization, in particular the organization of Predynastic society and the role of ideology in the formation of the ancient Egyptian centralized state and the origins of Egyptian divine kingship. Dr. Anderson specializes in the integration of computers and archaeology, utilizing 3D technologies to facilitate collection, analysis, and dissemination of field results. NICOLA ARAVECCHIA Nicola Aravecchia (Nominated Elected Governor) holds a BA in Classical Studies from the University of Bologna, an MA in Ancient and Medieval Art & Archaeology and a Ph.D. in Art History both from the University of Minnesota. He is the Archaeological Field Director of the excavations at ʿAin el-Gedida, a fourth-century settlement in the Dakhla Oasis of Upper Egypt, and the Deputy Field Director at Amheida/Trimithis, a Graeco-Roman city in Dakhla Oasis. Nicola is also a Research Affiliate of the Institute for the Study of the Ancient World at New York University. In the Spring of 2016, he was the invited Chair of Coptic Studies at The American University in Cairo. Nicola’s research interests encompass the art and archaeology of Graeco-Roman and late antique Egypt. In particular, they focus on the origins and development of Early Christian architecture in the Western Desert of Upper Egypt. -

Connect Series Accessories

Connect Series Accessories Our energy working for y ou.™ www.cumminspower.com 2013 Cummins Power Generation Inc. All rights reserved. Specifications are subject to change without notice. Cummins Power Generation and Cummins are registered trademarks of Cummins Inc. “Our energy working for you.” is a trademark of Cummins Power Generation. Other company, product, or service names may be trademarks or service marks of others. NAACSB-6026-EN (03/15) CONNECT SERIES ACCESSORIES Table of Contents DISPLAYS .................................................................................................................................................................. 1 HMI 211 Remote Unit (0541-1394) .................................................................................................... 1 RS In-Home Display (A046K103)....................................................................................................... 2 HMI 220 Remote Unit (A041J582) ................................................................................................... 3 ANNUNCIATORS (HMI 113 UNIT) ........................................................................................................................... 4 Annunciator – RS485 Panel Mount (A045J199) ................................................................................. 4 Annunciator – RS485 Panel Mount w/ Enclosure (A045J201) ............................................................ 4 AUXILIARY ............................................................................................................................................................... -

DSFRA IKEN Report Template

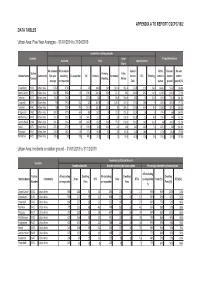

APPENDIX A TO REPORT CSCPC/19/2 DATA TABLES Urban Area: Five-Year Averages – 01/04/2014 to 31/04/2019 Incidents on station grounds Location False Pump Attendances Overview Fires Special Service Alarm All incidents All incidents Special All by On own On own Station Primary: False Station Name Community five-year excluding Co-responder All Primary Secondary Service RTC Flooding station's station station Number Dwelling Alarms average co-responder Calls pumps ground ground (%) Greenbank KV50 Urban Area 878.6 878.6 0 245 104.6 56.6 140.4 361.4 271.8 21.6 24.6 1424.8 974.2 68.4% Danes Castle KV32 Urban Area 832.6 830.8 1.8 198.8 126.4 56.6 72.4 385 248.4 29.2 14.8 1090.6 849.4 77.9% Torquay KV17 Urban Area 744.8 744.8 0 207.8 111 59 96.8 306.8 230 36 15.8 919.8 776.4 84.4% Crownhill KV49 Urban Area 742 741.8 0.2 227 100.6 43 126.4 337.4 177.4 28.6 9 878.4 680.6 77.5% Taunton KV61 Urban Area 734 733.4 0.6 227.8 132.8 56.6 95 284.6 221.6 65.4 8.4 1038.8 901.8 86.8% Bridgwater KV62 Urban Area 584.2 577.6 6.6 160 88.2 38 71.8 231.8 192.4 56 8 774.4 666 86.0% Middlemoor KV59 Urban Area 537.6 535.8 1.8 144.2 91.2 33 53 239.6 153.8 51 8.8 724.4 444 61.3% Camels Head KV48 Urban Area 491.6 491.2 0.4 162.8 85.2 50.4 77.6 178.6 150.2 16.6 11.8 638 390.2 61.2% Yeovil KV73 Urban Area 471.6 471.6 0 139.6 78.6 34.8 61 191 141 46.8 7.4 674.2 569 84.4% Plympton KV47 Urban Area 218.4 204.4 14 57.8 34.8 12 23 87.8 72.4 18.6 3 170.6 135.8 79.6% Plymstock KV51 Urban Area 185.8 185 0.8 48.4 27.4 12 21 76.8 60.6 12.6 2.6 165.4 123.8 74.8% Urban Area: Incidents on -

Expanding the Toolkit for Metabolic Engineering

Expanding the Toolkit for Metabolic Engineering Yao Zong (Andy) Ng Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences COLUMBIA UNIVERSITY 2016 © 2016 Yao Zong (Andy) Ng All rights reserved ABSTRACT Expanding the Toolkit for Metabolic Engineering Yao Zong (Andy) Ng The essence of metabolic engineering is the modification of microbes for the overproduction of useful compounds. These cellular factories are increasingly recognized as an environmentally-friendly and cost-effective way to convert inexpensive and renewable feedstocks into products, compared to traditional chemical synthesis from petrochemicals. The products span the spectrum of specialty, fine or bulk chemicals, with uses such as pharmaceuticals, nutraceuticals, flavors and fragrances, agrochemicals, biofuels and building blocks for other compounds. However, the process of metabolic engineering can be long and expensive, primarily due to technological hurdles, our incomplete understanding of biology, as well as redundancies and limitations built into the natural program of living cells. Combinatorial or directed evolution approaches can enable us to make progress even without a full understanding of the cell, and can also lead to the discovery of new knowledge. This thesis is focused on addressing the technological bottlenecks in the directed evolution cycle, specifically de novo DNA assembly to generate strain libraries and small molecule product screens and selections. In Chapter 1, we begin by examining the origins of the field of metabolic engineering. We review the classic “design–build–test–analyze” (DBTA) metabolic engineering cycle and the different strategies that have been employed to engineer cell metabolism, namely constructive and inverse metabolic engineering. -

Risk Assessment of Flash Floods in the Valley of the Kings, Egypt

京都大学防災研究所年報 第 60 号 B 平成 29 年 DPRI Annuals, No. 60 B, 2017 Risk Assessment of Flash Floods in the Valley of the Kings, Egypt Yusuke OGISO(1), Tetsuya SUMI, Sameh KANTOUSH, Mohammed SABER and Mohammed ABDEL-FATTAH(1) (1) Graduate School of Engineering, Kyoto University Synopsis Flash floods unavoidably affect various archaeological sites in Egypt, through increased frequency and severity of extreme events. The Valley of the Kings (KV) is a UNESCO World Heritage site with more than thirty opened tombs. Recently, most of these tombs have been damaged and inundated after 1994 flood. Therefore, KV mitigation strategy has been proposed and implemented with low protection wall surrounding tombs. The present study focuses on the evaluation and risk assessment of the current mitigation measures especially under extreme flood events. Two dimensional hydrodynamic model combined with rainfall runoff modeling by using TELEMAC-2D to simulate the present situation without protection wall and determine the risk of 1994 flood. The results revealed that the current mitigation measures are not efficient. Based on the simulation scenarios, risk of flash floods is assessed, and the more efficient mitigation measurements are proposed. Keywords: Flash floods, The Valley of the Kings, TELEMAC-2D, Mitigation measures 1. Introduction Recently, most of these tombs have been damaged and inundated after 1994 flood. In response to this Egypt is one of arid and semiarid Arabian flood event, the American Research Center in Egypt countries that faces flash floods in the coastal and (ARCE) hired an interdisciplinary team of Nile wadi systems. Wadi is a dry riverbed that can consultants to prepare a flood-protection plan. -

2019: Alexandria, Virginia

THE 70TH ANNUAL MEETING OF THE AMERICAN RESEARCH CENTER IN EGYPT April 12-14, 2019 Washington, D.C. ANNUAL MEETING OF THE AMERICAN RESEARCH CENTER IN EGYPT April 12-14, 2019 Washington, D.C. U.S. Headquarters 909 North Washington Street, Suite 320 Alexandria, Virginia, 22314 703.721.3479 Cairo Center 2 Midan Simón Bolívar Garden City, Cairo, 11461 20.2.2794.8239 [email protected] 2 3 *Dr. Ahmed Abu-Zayed, Head of Libraries and Archives TABLE CONTENTS Janie Abdul Aziz, Grant Administrator of *Djodi Deutsch, Academic Programs Manager Itinerary 12 Zakaria Yacoub, IT Manager Session Schedule 14 *Sally El Sabbahy, Communications & Outreach Associate *Samira El Adawy, Programs Coordinator Presentation Abstracts 18 Andreas Kostopoulos, Project Archives Specialist Student Poster Abstracts 99 Noha Atef Halim, Assistant Finance Manager Yasser Tharwat, Project Financial & Reporting Manager ARCE STAFF Doaa Adel, Accountant U.S. Staff Salah Metwally, Associate for Governmental Affairs Osama Abdel Fatah Mohamed , Supervising Librarian *Dr. Fatma Ismail, Interim US Operations Director Amira Gamal, Cataloguing Librarian *Michael Wiles, Chief Financial Officier Reda Anwar, Administrative Assistant to Office Manager *Laura Rheintgen, Director of Development Salah Rawash, Security & Reception Coordinator *Dr. Heba Abdel Salam, US Programs Advisor Abdrabou Ali Hassan, Maintenance Assistant & Director’s Driver *Claire Haymes, Board Relations Manager Ahmed Hassan, Senior Traffic Department Officer & Driver *Megan Allday, Annual Meeting Coordinator (Consultant) Ramadan Khalil Abdou, ARCE Representative Ellen Flanagan, US Human Resources Coordinator (Consultant) Mohamed Hassan Mohamed, Transportation Assistant & Messenger *Rebecca Cook, Membership & Development Manager Eid Fawzy, Technical Clerk & Messenger Freddy Feliz, IT Manager Nour Ibrahim, Messenger *Beth Wang, Development & Research Assistant ARCE STAFF ARCE STAFF Cairo Staff Luxor Staff *Dr. -

ABSTRACT Carl Nicholas Reeves STUDIES in the ARCHAEOLOGY

ABSTRACT Carl Nicholas Reeves STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies This study considers the physical evidence for tomb robbery on the Theban west bank, and its resultant effects, during the New Kingdom and Third Intermediate Period. Each tomb and deposit known from the Valley of the Kings is examined in detail, with the aims of establishing the archaeological context of each find and, wherever possible, isolating and comparing the evidence for post-interment activity. The archaeological and documentary evidence pertaining to the royal caches from Deir el-Bahri, the tomb of Amenophis II and elsewhere is drawn together, and from an analysis of this material it is possible to suggest the routes by which the mummies arrived at their final destinations. Large-scale tomb robbery is shown to have been a relatively uncommon phenomenon, confined to periods of political and economic instability. The caching of the royal mummies may be seen as a direct consequence of the tomb robberies of the late New Kingdom and the subsequent abandonment of the necropolis by Ramesses XI. Associated with the evacuation of the Valley tombs may be discerned an official dismantling of the burials and a re-absorption into the economy of the precious commodities there interred. STUDIES IN THE ARCHAEOLOGY OF THE VALLEY OF THE KINGS, with particular reference to tomb robbery and the caching of the royal mummies (Volumes I—II) Volume I: Text by Carl Nicholas Reeves Thesis submitted for the degree of Doctor of Philosophy School of Oriental Studies University of Durham 1984 The copyright of this thesis rests with the author. -

The Ancient Egyptians for Dummies‰ 01 065440 Ffirs.Qxp 5/31/07 9:19 AM Page Ii 01 065440 Ffirs.Qxp 5/31/07 9:19 AM Page Iii

01_065440 ffirs.qxp 5/31/07 9:19 AM Page i The Ancient Egyptians FOR DUMmIES‰ 01_065440 ffirs.qxp 5/31/07 9:19 AM Page ii 01_065440 ffirs.qxp 5/31/07 9:19 AM Page iii The Ancient Egyptians FOR DUMmIES‰ by Charlotte Booth 01_065440 ffirs.qxp 5/31/07 9:19 AM Page iv The Ancient Egyptians For Dummies® Published by John Wiley & Sons, Ltd The Atrium Southern Gate Chichester West Sussex PO19 8SQ England E-mail (for orders and customer service enquires): [email protected] Visit our Home Page on www.wiley.com Copyright © 2007 John Wiley & Sons, Ltd, Chichester, West Sussex, England Published by John Wiley & Sons, Ltd, Chichester, West Sussex All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or trans- mitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or other- wise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, W1T 4LP, UK, without the permission in writing of the Publisher. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, England, or emailed to [email protected], or faxed to (44) 1243 770620. Trademarks: Wiley, the Wiley Publishing logo, For Dummies, the Dummies Man logo, A Reference for the Rest of Us!, The Dummies Way, Dummies Daily, The Fun and Easy Way, Dummies.com and related trade dress are trademarks or registered trademarks of John Wiley & Sons, Inc. -

The Cartouche Names of the New Kingdom

The cartouche names of the New Kingdom by Sjef Willockx With a complete kinglist of the 18th, 19th and 20th dynasty The cartouche names of the New Kingdom © Sjef Willockx, 2008 . Bibliography ..................................................................................................................3 Preface..........................................................................................................................4 1. Introduction ...............................................................................................................5 1.1. Developments in the royal titulary....................................................................5 1.2. The throne names ...........................................................................................5 1.3. The birth names ..............................................................................................7 1.4. The epithets to throne and birth names ...........................................................8 1.5. The names of gods in throne and birth names...............................................11 1.6. Peculiarities in spelling and orthography........................................................12 1.7. The kinglists ..................................................................................................14 1.8. The timeframe ...............................................................................................14 2. The epithets in the cartouche names of the New Kingdom ......................................17 2.1. Epithets, -

Mysterious Tomb 63.Pdf

Eberhard Dziobek, Michael Höveler-Müller und Christian E. Loeben (Herausgeber / Editors) Das geheimnisvolle Grab 63 * * * The Mysterious Tomb 63 Grab_63.indb 1 10.11.2009 17:06:09 Grab_63.indb 2 10.11.2009 17:06:10 Das geheimnisvolle Grab 63 Die neueste Entdeckung im Tal der Könige Archäologie und Kunst von Susan Osgood * * * The Mysterious Tomb 63 The Latest Discovery in the Valley of the Kings Art and Archaeology of Susan Osgood herausgegeben von / edited by Eberhard Dziobek Michael Höveler-Müller Christian E. Loeben Mit Beiträgen von / With contributions by Marianne Eaton-Krauss, Michael Höveler-Müller, W. Raymond Johnson, Christian E. Loeben, Susan Osgood, Otto Schaden und Maria Weigel Verlag Marie Leidorf GmbH · Rahden/Westf. 2009 Grab_63.indb 3 10.11.2009 17:06:10 240 Seiten mit ??? Abbildungen Bibliografi sche Information der Deutschen Nationalbibliothek Dziobek, Eberhard ; Höveler-Müller, Michael ; Loeben, Christian E. (Hrsg.): Das geheimnisvolle Grab 63 ; von Eberhard Dziobek ... Rahden/Westf. : Leidorf, 2009 ISBN 978-3-86757-453-2 Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografi e. Detaillierte bibliografi sche Daten sind im Internet über http://dnb.ddb.de abrufbar. Alle Rechte vorbehalten © 2009 Verlag Marie Leidorf GmbH Geschäftsführer: Dr. Bert Wiegel Stellerloh 65, D-32369 Rahden/Westf. Tel.: +49/(0)5771/ 9510-74, Fax: +49/(0)5771/ 9510-75 E-Mail: [email protected], Internet: www.vml.de ISBN 978-3-86757-453-2 Ägyptisches Museum der Rheinischen Friedrich-Wilhelms-Universität Bonn Regina-Pacis-Weg 7, D-53113 Bonn Tel. +49/(0)228/ 73 97 10, Fax +49/(0)228/ 73 73 60 [email protected], www.aegyptisches-museum.uni-bonn.de Museum August Kestner Trammplatz 3, D-30159 Hannover Tel.