Master Service Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

65C102 Co-Processor User Guide

Within this publication the term 'BBC' is used as an abbreviation for. British Broadcasting Corporation'. © Copyright ACORN Computers Limited 1985 Neither the whole or any part of the information contained in, or the product described in, this manual may be adapted or reproduced in any material form except with the prior written approval of ACORN Computers Limited (ACORN Computers). The product described in this manual and products for use with it, are subject to continuous development and improvement. All information of a technical nature and particulars of the product and its use ( including the information and particulars in this manual) are given by ACORN Computers in good faith. However, it is acknowledged that there may be errors or omissions in this manual. A list of details of any amendments or revisions to this manual can be obtained upon request from ACORN Computers Technical Enquiries. ACORN Computers welcome comments and suggestions relating to the product and this manual. All correspondence should be addressed to:- Technical Enquiries ACORN Computers Limited Newmarket Road Cambridge CB5 8PD All maintenance and service on the product must be carried out by ACORN Computers' authorised dealers. ACORN Computers can accept no liability whatsoever for any loss or damage caused by service or maintenance by unauthorised personnel. This manual is intended only to assist the reader in the use of this product, and therefore ACORN Computers shall not be liable for any loss or damage whatsoever arising from the use of any information or particulars in, or any error or omission in, this manual, or any incorrect use of the product. -

Retro Magazine World 0

Més que un Magazine TABLE OF CONTENTS ◊ The Karnak MFP810 Calculator Pag. 3 "Més que un club" (more than a club) is the slogan proudly ◊ SEGA SATURN - a fantastic but Pag. 4 displayed by Barcelona FC in the stands of its football stadium. misunderstood platform! With equal pride we can say that RetroMagazine World is more ◊ Commodore 264 Series Pag. 6 than just a magazine reserved for a group of enthusiasts. ◊ OLIVETTI, when Italy was Silicon Valley Pag. 10 ◊ Olivetti PC128S Pag. 15 With all our initiatives (the site, "Press Play Again", etc.) and the ◊ RetroLiPS project presence on the most frequented social networks, it proves to be Pag. 19 a community full of life. ◊ Nobility of a humble flowchart Pag. 20 ◊ Introduction to Commodore C128 Pag. 26 The Editorial Board has recently seen an increase in the number graphics - part 2 of collaborators, starting with Mike "The biker" Novarina, ◊ Turbo Rascal SE - A complete cross- Pag. 30 Alessandro Albano and continuing with Francesco Coppola, platform framework for 8/16-bit Beppe Rinella, Christian Miglio (humbly apologizing if we have development forgotten someone else worthy of being remembered). ◊ ATARI - The origin of the myth Pag. 34 In particular, the young Francesco Coppola will take care of the ◊ Another World: a scary and magnificent Pag. 36 journey Atari world, while Beppe Rinella will enrich the articles of games by leaving the patterns of the usual review. ◊ Road Hunter - TI99/4A Pag. 40 ◊ Wizard of Wor - Commodore 64 Pag. 42 RetroMagazine World is appreciated because it is made by ◊ F-1 Spirit: the way to Formula-1 (MSX) Pag. -

Acorn ABC 210/Cambridge Workstation

ACORN COMPUTERS LTD. ACW 443 SERVICE MANUAL 0420,001 Issue 1 January 1987 ACW SERVICE MANUAL Title: ACW SERVICE MANUAL Reference: 0420,001 Issue: 1 Replaces: 0.56 Applicability: Product Support Distribution: Authorised Service Agents Status: for publication Author: C.Watters, J.Wilkins and Others Date: 7 January 1987 Published by: Acorn Computers Ltd, Fulbourn Road, Cherry Hinton, Cambridge, CB1 4JN, England Within this publication the term 'BBC' is used as an abbreviation for 'British Broadcasting Corporation'. Copyright ACORN Computers Limited 1985 Neither the whole or any part of the information contained in, or the product described in, this manual may be adapted or reproduced in any material form except with the prior written approval of ACORN Computers Limited ( ACORN Computers). The product described in this manual and products for use with it, are subject to continuous development and improvement. All information of a technical nature and particulars of the product and its use (including the information and particulars in this manual) are given by ACORN Computers in good faith. However, it is acknowledged that there may be errors or omissions in this manual. A list of details of any amendments or revisions to this manual can be obtained upon request from ACORN Computers Technical Enquiries. ACORN Computers welcome comments and suggestions relating to the product and this manual. All correspondence should be addressed to:- Technical Enquiries ACORN Computers Limited Newmarket Road Cambridge CB5 8PD All maintenance and service on the product must be carried out by ACORN Computers' authorised service agents. ACORN Computers can accept no liability whatsoever for any loss or damage caused by service or maintenance by unauthorised personnel. -

The Master Series

N 1981 a good-looking newcomer This means that an enormous range of arrived on the microcomputer scene. add-ons and peripheral devices, plus a Its impressive pedigree and range of vast software library with many thousands BRITISH I BROADCASTING connections aroused interest. Its of titles, are available for use with the CORPORATION performance caused a sensation. Master Series — now. MASTER SERIES That newcomer was the British The Master 512, through its DOS+ MICROCOMPUTER Broadcasting Corporation Microcomputer, operating system, can be compatible with one of the great success stories of the software written for MS-DOS, CP/M-86 computer industry. A key feature of the or GEM, the most popular operating BBC's Computer Literacy Project, it was systems for the business environment. chosen for seven out of every ten micros bought for UK schools and five out of ten The Reliability of Experience used for medical applications. In homes The Master Series incorporates the and factories, offices and laboratories, the experience gained by Acorn Computers BBC Micro's user friendliness and ability on more than 700,000 microcomputers to solve problems has won it countless over five years of operation. Acorn's friends and admirers. design skills and production expertise Now, the concepts that were the key ensure that the Master Series maintains to that success have been incorporated in the BBC Micro's tradition of high a new range of advanced microcomputers them to share data and resources, the Master Scientific. engineering standards and its reputation — the BBC Master Series. highly regarded BBC BASIC The Master Scientific brings the power for reliability. -

Home Computing Weekly Magazine Issue

siw A'L^JSfmoneP'°?!T' use SimP'e to GAMES Garner|M SoftwareOUIIWUIfctOIULJU-'OSRJDIOS Designer ^^J Bv John Ham Invaders format Asteroids format Defender format & Beserh format BGREATGAMES INCLUDED: TurboSp/aerTanks 3 lot-Halloween- .mil Attach ofthe MutantHamburgers] Cyborg-Reflectron- | SplotandQBix Marketed exclusively by Ouicksilva Name Games Designer £14.95 Address Time Gale (48K Spectrum) Aquaplane (4BK Sped rum) Meteor Storm (1 6K Spectrum} Cheques payable to Quicksil lenclosecrieaue'P.Ofor - . Send to Software Studio, S* Ouicksilva Mall Order, P.O. Box 6, X^$s» Wlmbome, Dorset BH21 71 Telephone: (0202) 85 \WM***** December 6-12, 1981 No. 40 24 PACES OF BUY THIS SPACK SPECTRUM BEST uratnairJ . 5,6.12 m Hews, One Man's view, U.S. Scene Three new games for the Colour Genie are out from ihc Ipswich VIC-20 program IS Software Factory. Costing £8 Don't look if you hate spiders . each, they are A-IO Bomber, Geniepede and Martian Rescue. Software reviews IT Arcade games for BBC, Dragon, Texas IPSY SO/IY, Three IK zxsi programs 18 Software reviews 21 Games for Commodore 64, Spectrum, Texas I . 22 around for quite a while. Lniiilci Metro Blii/, Cosmic Split. Mobi Dick. Krvstals of Zong ant Neoclvps, thev cost £7.95 each. Dragon software reviews 24 Letters 27 Software reviews 28 Games for BBC. Commodore 64, Spectrum, Texas Computer Buyers' Guide 29-60 All ilie tact, in a kaiuii pnli-orii upplemeni Spectr There's a vic-20 program Come to the cabaret . and gel in a spin v available for Ihc software reviews e: £6.50. -

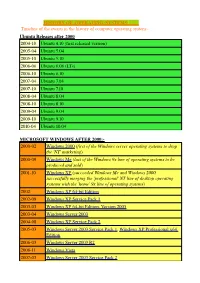

HISTORY of OPERATING SYSTEMS Timeline of The

HISTORY OF OPERATING SYSTEMS Timeline of the events in the history of computer operating system:- Ubuntu Releases after 2000 2004-10 Ubuntu 4.10 (first released version) 2005-04 Ubuntu 5.04 2005-10 Ubuntu 5.10 2006-06 Ubuntu 6.06 (LTs) 2006-10 Ubuntu 6.10 2007-04 Ubuntu 7.04 2007-10 Ubuntu 7.10 2008-04 Ubuntu 8.04 2008-10 Ubuntu 8.10 2009-04 Ubuntu 9.04 2009-10 Ubuntu 9.10 2010-04 Ubuntu 10.04 MICROSOFT WINDOWS AFTER 2000:- 2000-02 Windows 2000 (first of the Windows server operating systems to drop the ©NT© marketing) 2000-09 Windows Me (last of the Windows 9x line of operating systems to be produced and sold) 2001-10 Windows XP (succeeded Windows Me and Windows 2000, successfully merging the ©professional© NT line of desktop operating systems with the ©home© 9x line of operating systems) 2002 Windows XP 64-bit Edition 2002-09 Windows XP Service Pack 1 2003-03 Windows XP 64-bit Edition, Version 2003 2003-04 Windows Server 2003 2004-08 Windows XP Service Pack 2 2005-03 Windows Server 2003 Service Pack 1, Windows XP Professional x64 Edition 2006-03 Windows Server 2003 R2 2006-11 Windows Vista 2007-03 Windows Server 2003 Service Pack 2 2007-11 Windows Home Server 2008-02 Windows Vista Service Pack 1, Windows Server 2008 2008-04 Windows XP Service Pack 3 2009-05 Windows Vista Service Pack 2 2009-10 Windows 7(22 occtober 2009), Windows Server 2008 R2 EVENT IN HISTORY OF OS SINCE 1954:- 1950s 1954 MIT©s operating system made for UNIVAC 1103 1955 General Motors Operating System made for IBM 701 1956 GM-NAA I/O for IBM 704, based on General Motors -

Frobnicate Magazine, Issue 27

Look what I photographed in our back field... Conclusive proof! Summer 2006 Issue 27 =C0 123> Contains sustained moderate geekery. Index: [ #27, 2006/06/21 20:01 CET ] Page 2 . Index (Summer Solstice) Page 3 . Making bread... Page 5 . HeyRick software Page 6 . Embedded systems Page 8 . Go figure Page 13 . Virus 101 Page 18 . Bread Revisited Page 19 . Ewen’s multi-satellite setup by Ewen Cathcart Page 22r. The Frobnicate Quiz Page 23 . Mom’s page by Stephanie-Jane Murray Page 24 . The Wrap Party Credits: Designed, written, and created by Richard Murray. “Ewen’s multi-satellite setup” written by Ewen Cathcart. “Mom’s Page” written by Stephanie-Jane Murray. Images that are not my own have attribution. a. You may print this document provided it is unaltered. b. This document may be freely distributed in an unaltered form. (if you wish to convert this document to a different format, please contact me first) c. You may not charge any fee for passing on copies of this document (in electronic or printed form) except for “reasonable” media/printing/postage fees (which total no more than 5 euro; approximately £3.15 sterling or $5.60 US dollars). Please note that nobody is ‘authorised’ to provide printed versions of Frobnicate, so obviously we are unable to control the quality of any such prints made. Frobnicate incorporates colour images/logos. Don’t settle for black & white unless it’s very cheap! d. The contents of this document are Copyright © 2006 Rick Murray, unless otherwise noted. e. All reasonable care is taken in the production of this document, but we will not be legally liable for errors, or any loss arising from those errors. -

Master Compact Service Manual

British Broadcasting Corporation Master Series Compact Microcomputer Service Manual Part No. 0458,002 Issue 1 October 1986 Master Series Compact Microcomputer Service Manual BRITISH BROADCASTING CORPORATION MASTER SERIES COMPACT COMPUTER SERVICE MANUAL SECTION 1 KEYBOARD and PROCESSOR PAGE 1 SECTION 2 MONITOR STAND PAGE 46 Issue 2 Master Series Compact Microcomputer Service Manual SECTION 1 BRITISH BROADCASTING CORPORATION MASTER SERIES COMPACT MICROCOMPUTER SERVICE MANUAL KEYBOARD and PROCESSOR 1 Issue 1 Master Series Compact Microcomputer Service Manual Within this publication the term BBC is used as an abbreviation for ' British Broadcasting Corporation. Copyright Acorn Computers Limited 1986 Neither the whole or any part of the information contained in, or the product described in, this manual may be adapted or reproduced in any material form except with the prior written approval of Acorn Computers Limited (Acorn Computers). The product described in this manual and products for use with it, are subject to continuous development and improvement. All information of a technical nature and particulars of the product and its use (including the information and particulars in this manual) are given by Acorn Computers in good faith. However, it is acknowledged that there may be errors or omissions in this manual. A list of details of any amendments or revisions to this manual can be obtained upon request from Acorn Computers Technical Enquiries. Acorn Computers welcome comments and suggestions relating to the product and this manual. All correspondence should be addressed to:- Technical Enquiries Acorn Computers Limited Newmarket Road Cambridge CB5 8PD All maintenance and service on the product must be carried out by Acorn Computers authorised dealers. -

Acorn BBC Master Compact

BBC Master Compact SERVICE MANUAL © 1986 Acorn British Broadcasting Corporation Master Series Compact Microcomputer Service Manual Part No. 0458,002 Issue 1 October 1986 Master Series Compact Microcomputer Service Manual BRITISH BROADCASTING CORPORATION MASTER SERIES COMPACT COMPUTER SERVICE MANUAL SECTION 1 KEYBOARD and PROCESSOR PAGE 1 SECTION 2 MONITOR STAND PAGE 46 Issue 2 Master Series Compact Microcomputer Service Manual SECTION 1 BRITISH BROADCASTING CORPORATION MASTER SERIES COMPACT MICROCOMPUTER SERVICE MANUAL KEYBOARD and PROCESSOR 1 Issue 1 Master Series Compact Microcomputer Service Manual Within this publication the term BBC is used as an abbreviation for ' British Broadcasting Corporation. Copyright Acorn Computers Limited 1986 Neither the whole or any part of the information contained in, or the product described in, this manual may be adapted or reproduced in any material form except with the prior written approval of Acorn Computers Limited (Acorn Computers). The product described in this manual and products for use with it, are subject to continuous development and improvement. All information of a technical nature and particulars of the product and its use (including the information and particulars in this manual) are given by Acorn Computers in good faith. However, it is acknowledged that there may be errors or omissions in this manual. A list of details of any amendments or revisions to this manual can be obtained upon request from Acorn Computers Technical Enquiries. Acorn Computers welcome comments and suggestions relating to the product and this manual. All correspondence should be addressed to:- Technical Enquiries Acorn Computers Limited Newmarket Road Cambridge CB5 8PD All maintenance and service on the product must be carried out by Acorn Computers authorised dealers. -

Retrocade Magazine Vol 1 Issue 2 Spring 2012

Retro Ad Retro Ad Volume 1, Issue 2 Spring 2012 Insert Coin Editor-In-Chief 6 Rob Maerz Letters 8 Copy Editor Reset 9 Franka C. Maerz Retrocharts 12 Contributors Michael Allard Retroboards 13 Mark Alpiger Scoreboards 29 Jasper Alto Kevin Armstrong Event Coverage: MAGFest X 32 Eric Bailey Daniel Castaneda #GameChanger2012 36 Matt Daws British Backtrack with Mike James 39 Catherine DeSpira Forrest Hodges Spega 42 Mike James Mike Kennedy My View (of Classic Arcade Gaming…the Hobby) 47 Christian Matozzo 48 Elena García Méndez Emulation Nation Robert T Mruczek 50 Will Nicholes Strategy Session: Pepper II (Arcade) Patrick Scott Patterson 53 Strategy Session: Super Cobra (Arcade) Scott Schreiber Jeff Spega Cleaning Junior VectrexMad! 61 Michael Allard takes you through cleaning that dirty old 2600 Junior Brett Weiss Indy 500 Tournament 70 Cover Illustration Troy Stanwyck Invite your friends and fire up those consoles for some Indy 500 action! Batari Basic 72 Atari VCS programming tips from Forrest Hodges Cover Story: Attack of the Homebrews! A homebrew tsunami hit the classic gaming community in the fourth quarter of 2011. We have some of the Retrocade Magazine hottest titles reviewed and ISSN 2165-0330 we announce the first 74 Braumeister Award winner © 2011 RetrocadeMagazine.com. All rights reserved for homebrew of the year! A Conversation with Carla Meninsky 121 Will Nicholes interviews former Atari programmer Carla Meninsky Jay Smith: An Engineer’s Engineer 127 A transcription of Retrogaming Roundup’s interview with the man behind the Microvision Mark Alpiger 130 The gloved one talks about tournaments, the King of Kong, high scores and vegetables Interview with Ted Dabney A transcription of Retrogaming Roundup’s conversation with one of Atari’s founding 136 fathers Reinvestigating Polybius Catherine DeSpira investigates the Urban Legend of Polybius. -

ACORN USER BBC MICRO • ELECTRON • ATOM NOVEMBER 1984 £1 GREAT CONTEST! Win a £66 Computer Desk

ACORN USER BBC MICRO • ELECTRON • ATOM NOVEMBER 1984 £1 GREAT CONTEST! Win a £66 computer desk QUIZ FOR SCHOOLS: 10 software packs to be won from BBC Radio EDUCATION: Getting children to write with confidence CLASHING ROMS: The software solution SIX OF THE BEST REVIEWS: Two digitisers to trace pictures MICRO LIVE ON TV: Behind the scenes with the Producer DOUBLE MEASURE... , wice as much storage capacity on your present or proposed discs. The LVL true double density printed circuit board offers an amazing 1 ,474,560 Bytes of on-hne storage, on a twin 80 track double density drive. Removed is the 8271; (it is not capable ot supporting double density). In it's place, a small printed circuit board with a new disc controller and support circuitry provides a much improved data retrieval. This drastically reduces read errors by using a phased locked loop data separator, which is superior to the standard window circuit. Your BBC micro will now recognise the media density in the drive, and inform you if it is correct. You may define what density you require, 40 or 80 track, and which sides of the disc to use. Tlie device gives complete flexibibty and comes with an Eprom containing firmware; manual, and a 40/80 track utilities disc. On a dual drive it is simplicity itself to copy existing software from single density to double density. • Double Density • 40 or 80 track • Automatically • Own PCB with checks for correct seperate 8Mhz density clock • No 8271 (RareS • Simple to fit expensive) • User definable • Utilities provided density • Defaults to single • Phase lock loop density on power data separator up QLcircuit. -

Ebook - Informations About Operating Systems Version: September 3, 2016 | Download

eBook - Informations about Operating Systems Version: September 3, 2016 | Download: www.operating-system.org AIX Operating System (Unix) Internet: AIX Operating System (Unix) AmigaOS Operating System Internet: AmigaOS Operating System Android operating system Internet: Android operating system Aperios Operating System Internet: Aperios Operating System AtheOS Operating System Internet: AtheOS Operating System BeIA Operating System Internet: BeIA Operating System BeOS Operating System Internet: BeOS Operating System BSD/OS Operating System Internet: BSD/OS Operating System CP/M, DR-DOS Operating System Internet: CP/M, DR-DOS Operating System Darwin Operating System Internet: Darwin Operating System Debian Linux Operating System Internet: Debian Linux Operating System eComStation Operating System Internet: eComStation Operating System Symbian (EPOC) Operating System Internet: Symbian (EPOC) Operating System FreeBSD Operating System (BSD) Internet: FreeBSD Operating System (BSD) Gentoo Linux Operating System Internet: Gentoo Linux Operating System Haiku Operating System Internet: Haiku Operating System HP-UX Operating System (Unix) Internet: HP-UX Operating System (Unix) GNU/Hurd Operating System Internet: GNU/Hurd Operating System Inferno Operating System Internet: Inferno Operating System IRIX Operating System (Unix) Internet: IRIX Operating System (Unix) JavaOS Operating System Internet: JavaOS Operating System LFS Operating System (Linux) Internet: LFS Operating System (Linux) Linspire Operating System (Linux) Internet: Linspire Operating