GS3470 3G, HD, SD SDI Receiver

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Understanding HD and 3G-SDI Video Poster

Understanding HD & 3G-SDI Video EYE DIGITAL SIGNAL TIMING EYE DIAGRAM The eye diagram is constructed by overlaying portions of the sampled data stream until enough data amplitude is important because of its relation to noise, and because the Y', R'-Y', B'-Y', COMMONLY USED FOR ANALOG COMPONENT ANALOG VIDEO transitions produce the familiar display. A unit interval (UI) is defined as the time between two adjacent signal receiver estimates the required high-frequency compensation (equalization) based on the Format 1125/60/2:1 750/60/1:1 525/59.94/2:1, 625/50/2:1, 1250/50/2:1 transitions, which is the reciprocal of clock frequency. UI is 3.7 ns for digital component 525 / 625 (SMPTE remaining half-clock-frequency energy as the signal arrives. Incorrect amplitude at the Y’ 0.2126 R' + 0.7152 G' + 0.0722 B' 0.299 R' + 0.587 G' + 0.114 B' 259M), 673.4 ps for digital high-definition (SMPTE 292) and 336.7ps for 3G-SDI serial digital (SMPTE 424M) sending end could result in an incorrect equalization applied at the receiving end, thus causing Digital video synchronization is provided by End of Active Video (EAV) and Start of Active Video (SAV) sequences which start with a R'-Y' 0.7874 R' - 0.7152 G' - 0.0722 B' 0.701 R' - 0.587 G' - 0.114 B' as shown in Table 1. A serial receiver determines if the signal is “high” or “low” in the center of each eye, and signal distortions. Overshoot of the rising and falling edge should not exceed 10% of the waveform HORIZONTAL LINE TIMING unique three word pattern: 3FFh (all bits in the word set to 1), 000h (all 0’s), 000h (all 0’s), followed by a fourth “XYZ” word whose B'-Y' -0.2126 R' - 0.7152 G' + 0.9278 B' -0.299 R' - 0.587 G' + 0.886 B' detects the serial data. -

Multi-Rate Serial Digital Interface (SDI) Physical Layer IP Core Is an Ipexpress User-Configurable Core and Can Be Used to Generate Any Allowable Configuration

ispLever TM CORECORE Multi-Rate Serial Digital Interface Physical Layer IP Core User’s Guide January 2012 ipug70_01.2 Multi-Rate Serial Data Interface Physical Layer Lattice Semiconductor IP Core User’s Guide Introduction Serial Digital Interface (SDI) is the most popular raw video link standard used in television broadcast studios and video production facilities. Field Programmable Gate Arrays (FPGAs) with SDI interface capability can be used for acquisition, mixing, storage, editing, processing and format conversion applications. Simpler applications use FPGAs to acquire SDI data from one or more standard definition (SD) or high definition (HD) sources, perform sim- ple processing and retransmit the video data in SDI format. Such applications require an SDI physical layer (PHY) interface and some basic processing blocks such as a color space converter and frame buffer. In more complex applications, the acquired video receives additional processing, such as video format conversion, filtering, scaling, graphics mixing and picture-in-picture display. FPGA devices can also be used as a bridge between SDI video sources and backplane protocols such as PCI Express or Ethernet, with or without any additional video processing. In an FPGA-based SDI solution, the physical interface portion is often the most challenging part of the solution. This is because the PHY layer includes several device-dependent components such as high speed I/Os (inputs/outputs), serializer/deserializer (SERDES), clock/data recovery, word alignment and timing signal detection logic. Video processing, on the other hand, is algorithmic and is usually achieved using proprietary algorithms developed by in-house teams. The Lattice Multi-Rate SDI PHY Intellectual Property (IP) Core is a complete SDI PHY interface that connects to the high-speed SDI serial data on one side and the formatted parallel data on the other side. -

HD-STAR® Handheld HD-SDI and SD-SDI Generator and Monitor

HD-STAR® Handheld HD-SDI and SD-SDI Generator and Monitor FEATURES • Multiple functionality – Color monitor – Vectorscope – Waveform monitor VIDEO TEST – Test signal generator – Embedded audio monitor // – Serial data analyzer T N • Multiformats – HD-SDI – SD-SDI EME • Portable, handheld – PDA-sized SUR – Weighs under one pound with battery • Integrated 320x240 color LCD display EA • Touchscreen operation ND M A PRODUCT DETAILS T With a powerful array of features and functions that include a video test signal gen- S erator, color monitor, waveform monitor, vectorscope, serial data analyzer and an au- E T dio analyzer/monitor, the lightweight HD-STAR is ideal for monitoring field production camera setup, equipment installation, or troubleshooting signal path issues related to high-definition and standard-definition digital formats. The Videotek® HD-STAR® is a portable, battery-powered HD-SDI and SD-SDI This PDA-sized test monitor was designed to offer the convenience of portability without video generator and monitor. Also possessing embedded audio generator and sacrificing function and performance. To enhance the user’s experience, the HD-STAR monitor capabilities, the HD-STAR provides a level of multiformat functionality and features an integrated 320x240 color LCD display, utilizing touchscreen technology to control and configure each operation. Maintaining power in versatility that sets it apart from other handheld test and measurement products the field won’t be a problem — the HD-STAR runs on a Li-Ion battery pack. on the market. The HD-STAR includes one looping video input for monitoring HD-SDI and SD-SDI sig- nals formatted in SMPTE 292 M or SMPTE 259 M-C with embedded audio. -

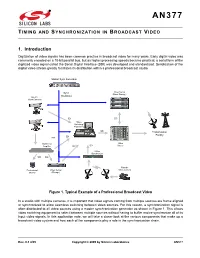

1. Introduction

AN377 TIMING AND SYNCHRONIZATION IN BROADCAST VIDEO 1. Introduction Digitization of video signals has been common practice in broadcast video for many years. Early digital video was commonly encoded on a 10-bit parallel bus, but as higher processing speeds became practical, a serial form of the digitized video signal called the Serial Digital Interface (SDI) was developed and standardized. Serialization of the digital video stream greatly facilitates its distribution within a professional broadcast studio. Master Sync Generator Sync Video Server (Mass Storage) (Genlock) On-site Video Cameras SDI SDI Video Switching/ Processing SDI Transmission Facility SDI SDI Distribution Video Amplifier SDI SDI Router Frame Synchronizer SDI SDI Remote Professional Video Server Video Camera Monitor (Storage) Figure 1. Typical Example of a Professional Broadcast Video In a studio with multiple cameras, it is important that video signals coming from multiple sources are frame aligned or synchronized to allow seamless switching between video sources. For this reason, a synchronization signal is often distributed to all video sources using a master synchronization generator as shown in Figure 1. This allows video switching equipment to select between multiple sources without having to buffer and re-synchronize all of its input video signals. In this application note, we will take a closer look at the various components that make up a broadcast video system and how each of the components play a role in the synchronization chain. Rev. 0.1 8/09 Copyright © 2009 by Silicon Laboratories AN377 AN377 2. Digitizing the Video Signal A video camera uses sensors to capture and convert light to electrical signals that represent the three primary colors– red, green, and blue (RGB). -

22.2 Multichannel Audio Format Standardization Activity

22.2 Multichannel Audio Format Standardization Activity The audio format for Super Hi-Vision, which is 2. The 22.2 Multichannel Audio Format under research and development for high-presence 2.1 Requirements for a High-Presence Audio Format broadcasting in the future, is 22.2 multichannel audio. The requirements for a high-presence audio format for The 22.2 multichannel format is a 3D sound play-back use with Super Hi-Vision are as follows: format that is able to reproduce sound impressions that are much closer to natural sound than the 5.1 (1) Must be able to localize an audio image anywhere multichannel audio format used in current digital on the screen. broadcasts. Here, we present an overview of the 22.2 In viewing environments with a wide field of view multichannel audio format and describe current and large screen, it is important to be able to match the activities toward international standardization. positions of the video and audio images*2. Thus, a format that is able to localize the sound image anywhere on the screen is required. 1. Introduction At NHK STRL, we are developing Super Hi-Vision1) (2) Must be able to reproduce sound coming from all and conducting research toward the realization of high- directions surrounding the viewing position. presence broadcasting. Super Hi-Vision is an ultra-high- Sound arrives from all directions in the actual acoustic resolution video system with 4000 scaning lines and a field. Accordingly, to reproduce a high sense of presence, viewing angle*1 of 100°. The standard viewing distance the audio format must be able to reproduce sound for a video system is set such that the pixels are just coming from all directions. -

Aspen 3232HD-3G 32X32 3G HD−SDI Router

Aspen 3232HD-3G 32x32 3G HD−SDI Router The Aspen series routers are high−performance matrix switcher for 3G HD−SDI and HD−SDI dual link video signals. These units can switch any or all inputs to any or all outputs. Aspen 3232HD-3G HD-SDI Video Features Guaranteed 3G Bandwidth - Fully Loaded. Max Data Rate - 2.97Gbps. Multi-Standard Operation - SDI (SMPTE 259M & SMPTE 344M), HD−SDI (SMPTE 292M), 3G HD−SDI (SMPTE 424M) and dual link HD−SDI (SMPTE 372M). Advanced Equalization - Allows recovery of signals at over 155 meters at 3Gb/s, over 200 meters at 1.5Gb/s Reclocking & EQ Control - Reclockers and Equalizers can be turned on or off on a per port basis to allow non- SMPTE data such as MPEG-2 to pass through. - Input Equalization - Per input. - Re-Clocking - 5 modes: auto, bypass, 3G HD-SDI, HD-SDI & SD per input. Sync Features Looping Sync Input - Composite or Tri-sync. Control Features Front Panel XY Control (1616/3232HD-3G) - Multi-color I/O & function buttons. Built-in Web Control Interface - - Configuration and Set up - including Names, Salvos, Layers, Output Reclockers, Input Equalizers and more. - Touch and Click compatible for control via tablets or smartphones RS-232, RS-422 & Ethernet. Optional Remote Control Panels - Via RJ-45 (Ethernet). Supports TCP/IP Protocol - Rear Panel RJ-45 connector. Other Features 7 Year warranty - Parts and Labor Take - The Take button executes a selected function when pressed (switch, salvo recall, IP address change, etc.). Salvos - Memory locations of switching lists that are saved in the router and recalled by a single command. -

AJA KONA Series Datasheet (Pdf)

Full-service, independent repair center -~ ARTISAN® with experienced engineers and technicians on staff. TECHNOLOGY GROUP ~I We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins. Custom engineering Your definitive source so your equipment works exactly as you specify. for quality pre-owned • Critical and expedited services • Leasing / Rentals/ Demos equipment. • In stock/ Ready-to-ship • !TAR-certified secure asset solutions Expert team I Trust guarantee I 100% satisfaction Artisan Technology Group (217) 352-9330 | [email protected] | artisantg.com All trademarks, brand names, and brands appearing herein are the property o f their respective owners. Find the AJA XENA-LHe at our website: Click HERE KONA Products KONA3 KONALHe KONALSe THE DIFFERENCE BETWEEN WORK AND WORK OF ART. Award-winning functionality. Solid performance. Unparalleled reliability. That sums up the power of AJA Video’s KONA™ line of desktop video products for Mac OS X™. Built by video pros for video pros, these superior capture cards deliver top-of-the-line-quality for every type of video workflow. Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com Meet KONA THE VERY FINEST CAPTURE CARDS FOR SD, HD, DUAL LINK HD AND 2K ON MAC OS X. KONA cards are the finest uncompressed QuickTime input/output cards available anywhere. AJA KONA cards were the first capture cards available for Final Cut Pro™ on Mac OS X - and that innovation and quality continue today. A powerful Apple computer, whether a PCI-X or PCIe system, along with Apple’s Final Cut Studio™ and a KONA card bring you the highest level of quality and functionality for non-linear editing, motion graphics creation, and more. -

3G SDI Time Division Multiplexer/De-Multiplexer

datasheet FLASHLINK SDI-TD-3GMX-5 / SDI-TD-3GDX-5 3G SDI time division multiplexer/de-multiplexer This Flashlink 3G-SDI time division Key features multiplexer offers transport of • 4 x SD-SDI + 1 x HD-SDI or 2 x HD into 3G-SDI synchronous or asynchronous SD-/HD-SDI • Transport of 8 x SD-SDI over 3G-SDI when combined signals over an 3G-SDI infrastructure. with HD-TDM The 3G-SDI TDM signal is a fully compliant SMPTE 1080p • Fully SMPTE compliant 3G-SDI TDM link level B signal stream. The card can be configured to • On-board optical transmitter and receiver multiplex two HD-SDI signals into one 3G-SDI, or four SD- SDI and one HD-SDI signals into 3G-SDI. Transport eight SD-SDI signals over one 3G-SDI link by combining these new modules with the existing SDI-TD-MUX/SDI-TD- DMUX. On board optional optics for different transport schemes are available. R1514 nevion.com Equalizer Equalizer HD-SDI/SD-SDI Reclocker Reclocker HD-SDI/SD-SDI Optical 3G-SDI Output Optical 3G-SDI Input Equalizer Equalizer Optical Transmitter Optical Receiver HD-SDI/SD-SDI Reclocker Reclocker HD-SDI/SD-SDI Equalizer Equalizer 2x1 SD-SDI Reclocker TDM-MUX 3G-SDI3G-SDI Change- TDM-DMUX Reclocker SD-SDI InInfrfrasastructurtructuree over Equalizer Equalizer SD-SDI Reclocker Reclocker SD-SDI Electrical 3G-SDI Output Electrical 3G-SDI Input Equalizer Equalizer SD-SDI Reclocker Reclocker SD-SDI Microcontroller Remote Remote Control Microcontroller Control SDI-TD-3GMX-5 SDI-TD-3GDX-5 Common specifications General Power MUX +5V / 5.0W +15V / 1.5W Power DMUX +5 V / 3.9W +15 V / -

A DVR Technology Company Specifications

STANDARD FEATURES • Lowest price per HD channel • Records JPEG2000.mov files in HD or SD • Auto detect video standard • Data rate 100 Mbit/s • 4:2:2 sampling • 10 bit resolution Specifically designed for the TV Broadcaster, the Micron HD delivers all the advantages of HD • RS-422 machine control which allows easy access recording and playback in a powerful, compact unit when controlling multiple units with the lowest price per channel available! • 8 embedded audio channels for HD With a high definition broadcast quality Digital Video • 4 embedded audio channels for SD Recorder like the Micron HD you won’t have to • Up to 4 channels AES or 2 channels analog audio per compromise on image quality or rack space. The video channel Micron HD offers the highest quality images available by utilizing the JPEG 2000 codec in a powerful, • NTSC & PAL compact unit that takes up only 1RU. • Conforms to industry digital specification SMPTE 259M-C and SMPTE 292(HD-SDI) Exceptional Image Quality - Utilizes the visually lossless JPEG 2000 compression for SD/HD-SDI • Genlock input recording • SMPTE/EBU Longitudinal time code Affordable – Lowest price per channel in the • Chase lock broadcast industry • Discrete access to every frame • 2.5” SATA HDD or SSD drives w/USB on the Compact – 1 RU saves on rack space drive enclosure Readily Available Media – Uses industry standard • Loop record feature removable 2.5” drives and incorporates a • Instant cueing and clip recall USB located on the drive enclosure. • Dynamic tracking Easy to Control - Use the front panel or control • 1RU multiple units through the RS-422 with any controller • Up to 5 hours record time that supports Sony or Odetics protocol. -

3232HD HD−SDI and SDI Video

3232HD HD−SDI and SDI video. HD−SDI and SDI video. 3232HD HD-SDI Video Features Max. Data Rate - 1.485Gbps single link, 3Gbps dual link. Backwards Compatible With SDI Signals. Standards - SMPTE 372, SMPTE 310, SMPTE 292, SMPTE 259, DVB-ASI. Jitter - < 0.2UI. SDI Video Features Max. Data Rate - 360Mbps. Standards - SMPTE 310M, SMPTE 259M, DVB-ASI & ITU-R BT.601 Jitter - < 0.2UI. Stereo Audio Features Audio Type - Balanced or un-balanced on terminal blocks. Input (Level) Adjustment Capability (-8dB to +20.5dB) - Each input via RS-232, front panel, or TyLinx Pro™ software. Output (Volume) Adjustment Capability (Mute, -59.5dB to +15dB) - Each input via RS-232, front panel, or TyLinx Pro™ Software. No Zipper Effect - Lassen routing switchers use zero-crossover chip technology that eliminates the annoying “zipper sound effect” associated with digital volume controls. Audio Mute Capability. Crosstalk - 80dB @1kHz & 70dB @20kHz. S/N (20 - 20kHz) - > 90dB. Digital Audio Features Standards - AES-3 & AES-3id. Jitter - 0.25UI p-p. Control Features Local Front Panel Control With 80 Character LCD Readout. RS-232/422. RS-485 - For optional control panels. Supports TCP/IP Protocol - Rear Panel RJ-45 connector. WEB Browser Control. TyLinx Pro Router Control Software and TyLinx Pro Net™ Net work-Enabled Router Control Software. Other Features Downloadable Firmware Updates. Optional Control Panels. - Programmable, single bus and XY. Redundant Power Supplies - Optional on 32 x 32 & 32 x 16 models. UL & CE Approvals. Composite Video Features High Bandwidth - 100MHz (-3dB) fully loaded. Very Low Crosstalk - -80dB @ 1MHz -47dB @ 100MHz. Qwik Adjust Knob™ Rotary Control interface - This user intuitive knob along with the 80 character LCD display provides quick and convenient setup, adjustment and signal switching. -

Sdixtreme 3G+ On-The-Go Datasheet

SDI EXTENSION - Xtreme 3G Series SDI Xtreme 3G+ On The Go SDI Xtreme 3G+ On The Go Four SDI components combined in one 3G SDI Fiber Optic Extension - Portable Unit portable unit Each module provides RS-422 port for device control - Ideal for remote camera operations requiring pan, tilt and zoom functions Each module extends SDI signals over a single "ber - Supporting two SD/HD signals or one 3G signal - Providing a total support of up to eight SD/HD or four 3G/Dual-Link SDI signals Portable unit is comprised of four modules. Any combination of transmitter/receiver is possible. SMPTE 424M, 292M, 259M, 372M, 425 level A and B compliant Auto detects input video format and displays on LEDs Thinklogcal TRANSplex module available for CWDM use Auxillary power connector for camera use 2 Ruggedized Neutrik Connectors The Logical Solution - Portable Serial Digital Interface Extension The SDI Xtreme 3G+ product series is a compact, broadcast quality, SDI over "ber extension system. The On The Go system is a portable carrying case which houses four separate SDI modules, each of which supports two SD/HD signals or one 3G signal (as well as dual-link SDI). This enables users to transmit up to eight SD/HD or four 3G SDI signals with or without embedded audio and data. Depending on the infrastructure, the SDI Xtreme 3G+ can distribute uncompressed broadcast quality signals over single mode "ber up to 40 km. (24 miles) and up to 1000 meters over multi-mode "ber. In addition, this "ber based transport system gives users the assurance that each signal is immune to video pathological signals over the entire length of the "ber interconnect, while supporting all pathological patterns at all rates. -

High Definition (HD) Image Formats for Television Production

EBU – TECH 3299 High Definition (HD) Image Formats for Television Production Geneva December 2004 1 High Definition (HD) Image Formats for Television Production Tech 3299 - E High Definition (HD) Image Formats for Television Production Contents 1. Introduction.......................................................................................................................3 2. Normative references .......................................................................................................3 3. Informative References.....................................................................................................4 4. Nomenclatures and Image Sampling Systems .................................................................4 5. System compliance...........................................................................................................4 6. System colorimetry and opto-electrical conversion for system S1 to S4...........................4 7. Signal Formats for System 1 to 4 .....................................................................................5 8. Raster structure, digital picture representation and timing reference................................5 9. Digital Signal Formats for System 1 to 4...........................................................................6 10. Digital Interfaces...............................................................................................................6 2 Tech 3299 – E High Definition (HD) Image Formats for Television Production 1. Introduction This