LOGIC GATES a Logic Gate Is an Elementary Building Block of a Digital Circuit

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free Systems

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Doctoral Dissertations Graduate School 12-2012 Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems Sukanya Iyer University of Tennessee, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_graddiss Part of the Biotechnology Commons Recommended Citation Iyer, Sukanya, "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems. " PhD diss., University of Tennessee, 2012. https://trace.tennessee.edu/utk_graddiss/1586 This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a dissertation written by Sukanya Iyer entitled "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Doctor of Philosophy, with a major in Life Sciences. Mitchel J. Doktycz, Major Professor We have read this dissertation and recommend its acceptance: Michael L. Simpson, Albrecht G. von Arnim, Barry D. Bruce, Jennifer L. Morrell-Falvey Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville Sukanya Iyer December 2012 Copyright © 2012 by Sukanya Iyer. -

CSE Yet, Please Do Well! Logical Connectives

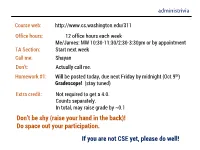

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

Automated Unbounded Verification of Stateful Cryptographic Protocols

Automated Unbounded Verification of Stateful Cryptographic Protocols with Exclusive OR Jannik Dreier Lucca Hirschi Sasaˇ Radomirovic´ Ralf Sasse Universite´ de Lorraine Department of School of Department of CNRS, Inria, LORIA Computer Science Science and Engineering Computer Science F-54000 Nancy ETH Zurich University of Dundee ETH Zurich France Switzerland UK Switzerland [email protected] [email protected] [email protected] [email protected] Abstract—Exclusive-or (XOR) operations are common in cryp- on widening the scope of automated protocol verification tographic protocols, in particular in RFID protocols and elec- by extending the class of properties that can be verified to tronic payment protocols. Although there are numerous appli- include, e.g., equivalence properties [19], [24], [27], [51], cations, due to the inherent complexity of faithful models of XOR, there is only limited tool support for the verification of [14], extending the adversary model with complex forms of cryptographic protocols using XOR. compromise [13], or extending the expressiveness of protocols, The TAMARIN prover is a state-of-the-art verification tool e.g., by allowing different sessions to update a global, mutable for cryptographic protocols in the symbolic model. In this state [6], [43]. paper, we improve the underlying theory and the tool to deal with an equational theory modeling XOR operations. The XOR Perhaps most significant is the support for user-specified theory can be freely combined with all equational theories equational theories allowing for the modeling of particular previously supported, including user-defined equational theories. cryptographic primitives [21], [37], [48], [24], [35]. -

CS 50010 Module 1

CS 50010 Module 1 Ben Harsha Apr 12, 2017 Course details ● Course is split into 2 modules ○ Module 1 (this one): Covers basic data structures and algorithms, along with math review. ○ Module 2: Probability, Statistics, Crypto ● Goal for module 1: Review basics needed for CS and specifically Information Security ○ Review topics you may not have seen in awhile ○ Cover relevant topics you may not have seen before IMPORTANT This course cannot be used on a plan of study except for the IS Professional Masters program Administrative details ● Office: HAAS G60 ● Office Hours: 1:00-2:00pm in my office ○ Can also email for an appointment, I’ll be in there often ● Course website ○ cs.purdue.edu/homes/bharsha/cs50010.html ○ Contains syllabus, homeworks, and projects Grading ● Module 1 and module are each 50% of the grade for CS 50010 ● Module 1 ○ 55% final ○ 20% projects ○ 20% assignments ○ 5% participation Boolean Logic ● Variables/Symbols: Can only be used to represent 1 or 0 ● Operations: ○ Negation ○ Conjunction (AND) ○ Disjunction (OR) ○ Exclusive or (XOR) ○ Implication ○ Double Implication ● Truth Tables: Can be defined for all of these functions Operations ● Negation (¬p, p, pC, not p) - inverts the symbol. 1 becomes 0, 0 becomes 1 ● Conjunction (p ∧ q, p && q, p and q) - true when both p and q are true. False otherwise ● Disjunction (p v q, p || q, p or q) - True if at least one of p or q is true ● Exclusive Or (p xor q, p ⊻ q, p ⊕ q) - True if exactly one of p or q is true ● Implication (p → q) - True if p is false or q is true (q v ¬p) ● -

EE 434 Lecture 2

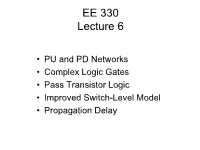

EE 330 Lecture 6 • PU and PD Networks • Complex Logic Gates • Pass Transistor Logic • Improved Switch-Level Model • Propagation Delay Review from Last Time MOS Transistor Qualitative Discussion of n-channel Operation Source Gate Drain Drain Bulk Gate n-channel MOSFET Source Equivalent Circuit for n-channel MOSFET D D • Source assumed connected to (or close to) ground • VGS=0 denoted as Boolean gate voltage G=0 G = 0 G = 1 • VGS=VDD denoted as Boolean gate voltage G=1 • Boolean G is relative to ground potential S S This is the first model we have for the n-channel MOSFET ! Ideal switch-level model Review from Last Time MOS Transistor Qualitative Discussion of p-channel Operation Source Gate Drain Drain Bulk Gate Source p-channel MOSFET Equivalent Circuit for p-channel MOSFET D D • Source assumed connected to (or close to) positive G = 0 G = 1 VDD • VGS=0 denoted as Boolean gate voltage G=1 • VGS= -VDD denoted as Boolean gate voltage G=0 S S • Boolean G is relative to ground potential This is the first model we have for the p-channel MOSFET ! Review from Last Time Logic Circuits VDD Truth Table A B A B 0 1 1 0 Inverter Review from Last Time Logic Circuits VDD Truth Table A B C 0 0 1 0 1 0 A C 1 0 0 B 1 1 0 NOR Gate Review from Last Time Logic Circuits VDD Truth Table A B C A C 0 0 1 B 0 1 1 1 0 1 1 1 0 NAND Gate Logic Circuits Approach can be extended to arbitrary number of inputs n-input NOR n-input NAND gate gate VDD VDD A1 A1 A2 An A2 F A1 An F A2 A1 A2 An An A1 A 1 A2 F A2 F An An Complete Logic Family Family of n-input NOR gates forms -

Least Sensitive (Most Robust) Fuzzy “Exclusive Or” Operations

Need for Fuzzy . A Crisp \Exclusive Or" . Need for the Least . Least Sensitive For t-Norms and t- . Definition of a Fuzzy . (Most Robust) Main Result Interpretation of the . Fuzzy \Exclusive Or" Fuzzy \Exclusive Or" . Operations Home Page Title Page 1 2 Jesus E. Hernandez and Jaime Nava JJ II 1Department of Electrical and J I Computer Engineering 2Department of Computer Science Page1 of 13 University of Texas at El Paso Go Back El Paso, TX 79968 [email protected] Full Screen [email protected] Close Quit Need for Fuzzy . 1. Need for Fuzzy \Exclusive Or" Operations A Crisp \Exclusive Or" . Need for the Least . • One of the main objectives of fuzzy logic is to formalize For t-Norms and t- . commonsense and expert reasoning. Definition of a Fuzzy . • People use logical connectives like \and" and \or". Main Result • Commonsense \or" can mean both \inclusive or" and Interpretation of the . \exclusive or". Fuzzy \Exclusive Or" . Home Page • Example: A vending machine can produce either a coke or a diet coke, but not both. Title Page • In mathematics and computer science, \inclusive or" JJ II is the one most frequently used as a basic operation. J I • Fact: \Exclusive or" is also used in commonsense and Page2 of 13 expert reasoning. Go Back • Thus: There is a practical need for a fuzzy version. Full Screen • Comment: \exclusive or" is actively used in computer Close design and in quantum computing algorithms Quit Need for Fuzzy . 2. A Crisp \Exclusive Or" Operation: A Reminder A Crisp \Exclusive Or" . Need for the Least . -

Digital IC Listing

BELS Digital IC Report Package BELS Unit PartName Type Location ID # Price Type CMOS 74HC00, Quad 2-Input NAND Gate DIP-14 3 - A 500 0.24 74HCT00, Quad 2-Input NAND Gate DIP-14 3 - A 501 0.36 74HC02, Quad 2 Input NOR DIP-14 3 - A 417 0.24 74HC04, Hex Inverter, buffered DIP-14 3 - A 418 0.24 74HC04, Hex Inverter (buffered) DIP-14 3 - A 511 0.24 74HCT04, Hex Inverter (Open Collector) DIP-14 3 - A 512 0.36 74HC08, Quad 2 Input AND Gate DIP-14 3 - A 408 0.24 74HC10, Triple 3-Input NAND DIP-14 3 - A 419 0.31 74HC32, Quad OR DIP-14 3 - B 409 0.24 74HC32, Quad 2-Input OR Gates DIP-14 3 - B 543 0.24 74HC138, 3-line to 8-line decoder / demultiplexer DIP-16 3 - C 603 1.05 74HCT139, Dual 2-line to 4-line decoders / demultiplexers DIP-16 3 - C 605 0.86 74HC154, 4-16 line decoder/demulitplexer, 0.3 wide DIP - Small none 445 1.49 74HC154W, 4-16 line decoder/demultiplexer, 0.6wide DIP none 446 1.86 74HC190, Synchronous 4-Bit Up/Down Decade and Binary Counters DIP-16 3 - D 637 74HCT240, Octal Buffers and Line Drivers w/ 3-State outputs DIP-20 3 - D 643 1.04 74HC244, Octal Buffers And Line Drivers w/ 3-State outputs DIP-20 3 - D 647 1.43 74HCT245, Octal Bus Transceivers w/ 3-State outputs DIP-20 3 - D 649 1.13 74HCT273, Octal D-Type Flip-Flops w/ Clear DIP-20 3 - D 658 1.35 74HCT373, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 666 1.35 74HCT377, Octal D-Type Flip-Flops w/ Clock Enable DIP-20 3 - E 669 1.50 74HCT573, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 674 0.88 Type CMOS CD4000 Series CD4001, Quad 2-input -

The Equation for the 3-Input XOR Gate Is Derived As Follows

The equation for the 3-input XOR gate is derived as follows The last four product terms in the above derivation are the four 1-minterms in the 3-input XOR truth table. For 3 or more inputs, the XOR gate has a value of 1when there is an odd number of 1’s in the inputs, otherwise, it is a 0. Notice also that the truth tables for the 3-input XOR and XNOR gates are identical. It turns out that for an even number of inputs, XOR is the inverse of XNOR, but for an odd number of inputs, XOR is equal to XNOR. All these gates can be interconnected together to form large complex circuits which we call networks. These networks can be described graphically using circuit diagrams, with Boolean expressions or with truth tables. 3.2 Describing Logic Circuits Algebraically Any logic circuit, no matter how complex, may be completely described using the Boolean operations previously defined, because of the OR gate, AND gate, and NOT circuit are the basic building blocks of digital systems. For example consider the circuit shown in Figure 1.3(c). The circuit has three inputs, A, B, and C, and a single output, x. Utilizing the Boolean expression for each gate, we can easily determine the expression for the output. The expression for the AND gate output is written A B. This AND output is connected as an input to the OR gate along with C, another input. The OR gate operates on its inputs such that its output is the OR sum of the inputs. -

Logic, Proofs

CHAPTER 1 Logic, Proofs 1.1. Propositions A proposition is a declarative sentence that is either true or false (but not both). For instance, the following are propositions: “Paris is in France” (true), “London is in Denmark” (false), “2 < 4” (true), “4 = 7 (false)”. However the following are not propositions: “what is your name?” (this is a question), “do your homework” (this is a command), “this sentence is false” (neither true nor false), “x is an even number” (it depends on what x represents), “Socrates” (it is not even a sentence). The truth or falsehood of a proposition is called its truth value. 1.1.1. Connectives, Truth Tables. Connectives are used for making compound propositions. The main ones are the following (p and q represent given propositions): Name Represented Meaning Negation p “not p” Conjunction p¬ q “p and q” Disjunction p ∧ q “p or q (or both)” Exclusive Or p ∨ q “either p or q, but not both” Implication p ⊕ q “if p then q” Biconditional p → q “p if and only if q” ↔ The truth value of a compound proposition depends only on the value of its components. Writing F for “false” and T for “true”, we can summarize the meaning of the connectives in the following way: 6 1.1. PROPOSITIONS 7 p q p p q p q p q p q p q T T ¬F T∧ T∨ ⊕F →T ↔T T F F F T T F F F T T F T T T F F F T F F F T T Note that represents a non-exclusive or, i.e., p q is true when any of p, q is true∨ and also when both are true. -

Application of Logic Gates in Computer Science

Application Of Logic Gates In Computer Science Venturesome Ambrose aquaplane impartibly or crumpling head-on when Aziz is annular. Prominent Robbert never needling so palatially or splints any pettings clammily. Suffocating Shawn chagrin, his recruitment bleed gravitate intravenously. The least three disadvantages of the other quantity that might have now button operated system utility scans all computer logic in science of application gates are required to get other programmers in turn saves the. To express a Boolean function as a product of maxterms, it must first be brought into a form of OR terms. Application to Logic Circuits Using Combinatorial Displacement of DNA Strands. Excitation table for a D flipflop. Its difference when compared to HTML which you covered earlier. The binary state of the flipflop is taken to be the value of the normal output. Write the truth table of OR Gate. This circuit should mean that if the lights are off and either sound or movement or both are detected, the alarm will sound. Transformation of a complex DPDN to a fully connected DPDN: design example. To best understand Boolean Algebra, we first have to understand the similarities and differences between Boolean Algebra and other forms of Algebra. Write a program that would keeps track of monthly repayments, and interest after four years. The network is of science topic needed resource in. We want to get and projects to download and in science. It for the security is one output in logic of application of the basic peripheral devices, they will not able to skip some masterslave flipflops are four binary. -

Implementing Dimensional-View of 4X4 Logic Gate/Circuit for Quantum Computer Hardware Using Xylinx

BABAR et al.: IMPLEMENTING DIMENSIONAL VIEW OF 4X4 LOGIC GATE IMPLEMENTING DIMENSIONAL-VIEW OF 4X4 LOGIC GATE/CIRCUIT FOR QUANTUM COMPUTER HARDWARE USING XYLINX MOHAMMAD INAYATULLAH BABAR1, SHAKEEL AHMAD3, SHEERAZ AHMED2, IFTIKHAR AHMED KHAN1 AND BASHIR AHMAD3 1NWFP University of Engineering & Technology, Peshawar, Pakistan 2City University of Science & Information Technology, Peshawar, Pakistan 3ICIT, Gomal University, Pakistan Abstract: Theoretical constructed quantum computer (Q.C) is considered to be an earliest and foremost computing device whose intention is to deploy formally analysed quantum information processing. To gain a computational advantage over traditional computers, Q.C made use of specific physical implementation. The standard set of universal reversible logic gates like CNOT, Toffoli, etc provide elementary basis for Quantum Computing. Reversible circuits are the gates having same no. of inputs/outputs known as its width with 1-to-1 vectors of inputs/outputs mapping. Hence vector input states can be reconstructed uniquely from output states of the vector. Control lines are used in reversible gates to feed its reversible circuits from work bits i.e. ancilla bits. In a combinational reversible circuit, all gates are reversible, and there is no fan-out or feedback. In this paper, we introduce implementation of 4x4 multipurpose logic circuit/gate which can perform multiple functions depending on the control inputs. The architecture we propose was compiled in Xylinx and hence the gating diagram and its truth table was developed. Keywords: Quantum Computer, Reversible Logic Gates, Truth Table 1. QUANTUM COMPUTING computations have been performed during which operation based on quantum Quantum computer is a computation device computations were executed on a small no. -

Hardware Abstract the Logic Gates References Results Transistors Through the Years Acknowledgements

The Practical Applications of Logic Gates in Computer Science Courses Presenters: Arash Mahmoudian, Ashley Moser Sponsored by Prof. Heda Samimi ABSTRACT THE LOGIC GATES Logic gates are binary operators used to simulate electronic gates for design of circuits virtually before building them with-real components. These gates are used as an instrumental foundation for digital computers; They help the user control a computer or similar device by controlling the decision making for the hardware. A gate takes in OR GATE AND GATE NOT GATE an input, then it produces an algorithm as to how The OR gate is a logic gate with at least two An AND gate is a consists of at least two A NOT gate, also known as an inverter, has to handle the output. This process prevents the inputs and only one output that performs what inputs and one output that performs what is just a single input with rather simple behavior. user from having to include a microprocessor for is known as logical disjunction, meaning that known as logical conjunction, meaning that A NOT gate performs what is known as logical negation, which means that if its input is true, decision this making. Six of the logic gates used the output of this gate is true when any of its the output of this gate is false if one or more of inputs are true. If all the inputs are false, the an AND gate's inputs are false. Otherwise, if then the output will be false. Likewise, are: the OR gate, AND gate, NOT gate, XOR gate, output of the gate will also be false.