Powerpc 405 Embedded Processor Core User’S Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

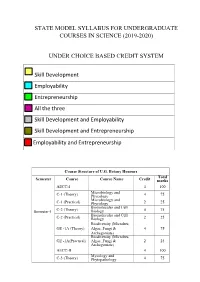

State Model Syllabus for Undergraduate Courses in Science (2019-2020)

STATE MODEL SYLLABUS FOR UNDERGRADUATE COURSES IN SCIENCE (2019-2020) UNDER CHOICE BASED CREDIT SYSTEM Skill Development Employability Entrepreneurship All the three Skill Development and Employability Skill Development and Entrepreneurship Employability and Entrepreneurship Course Structure of U.G. Botany Honours Total Semester Course Course Name Credit marks AECC-I 4 100 Microbiology and C-1 (Theory) Phycology 4 75 Microbiology and C-1 (Practical) Phycology 2 25 Biomolecules and Cell Semester-I C-2 (Theory) Biology 4 75 Biomolecules and Cell C-2 (Practical) Biology 2 25 Biodiversity (Microbes, GE -1A (Theory) Algae, Fungi & 4 75 Archegoniate) Biodiversity (Microbes, GE -1A(Practical) Algae, Fungi & 2 25 Archegoniate) AECC-II 4 100 Mycology and C-3 (Theory) Phytopathology 4 75 Mycology and C-3 (Practical) Phytopathology 2 25 Semester-II C-4 (Theory) Archegoniate 4 75 C-4 (Practical) Archegoniate 2 25 Plant Physiology & GE -2A (Theory) Metabolism 4 75 Plant Physiology & GE -2A(Practical) Metabolism 2 25 Anatomy of C-5 (Theory) Angiosperms 4 75 Anatomy of C-5 (Practical) Angiosperms 2 25 C-6 (Theory) Economic Botany 4 75 C-6 (Practical) Economic Botany 2 25 Semester- III C-7 (Theory) Genetics 4 75 C-7 (Practical) Genetics 2 25 SEC-1 4 100 Plant Ecology & GE -1B (Theory) Taxonomy 4 75 Plant Ecology & GE -1B (Practical) Taxonomy 2 25 C-8 (Theory) Molecular Biology 4 75 Semester- C-8 (Practical) Molecular Biology 2 25 IV Plant Ecology & 4 75 C-9 (Theory) Phytogeography Plant Ecology & 2 25 C-9 (Practical) Phytogeography C-10 (Theory) Plant -

PPC400 Debugger C++ and JAVAC++ Aswell Asthe Debugging of the TPU

BDM-PPC400 Technical Information Technical PPC400 Debugger ■ Full HLL and ASM support available ■ Batch processing ■ Supports ELF/DWARF format ■ 3.3 volt support ■ Support for internal triggers ■ Break on code or data ■ Unlimited software breakpoints ■ Fast download (ETHERNET or PARALLEL) up to 600KB/sec The debugger for IBM PowerPC 400 family allows fast access to the BDM interface of the chip. Up to 450 KByte can be downloaded in 1 second. The systems supports C, C++ and JAVA as well as the debugging of the TPU. BDM-PPC400 14.06.13 TRACE32 - Technical Information 2 Features ❏ Active and Passive JTAG ❏ Variable Debug Clock Speed Debugger available ■ 10 kHz...5 MHz ■ 1/4 CPU Clock ■ 1/8 CPU Clock ❏ Software Compatible to In-Circuit ■ Variable up to 100 MHz (Pow- Emulator and Monitor erDebug only) ■ Operation System ■ PRACTICE ❏ ■ ASM Debugger Tr igger ■ HLL Debugger for C and C++ ■ Input from PODBUS ■ Peripheral Windows ■ Output to PODBUS ❏ High-Speed Download ❏ Support for EPROM/FLASH ■ Up to 450 KByte/sec Simulator ■ Breakpoints in ROM Area ■ 8, 16 and 32 Bit EPROM/ FLASH Emulation BDM-PPC400 Features TRACE32 - Technical Information 3 Connector Connector Type stanard 100 mil connector (BETRG, AMP, etc.) Connector 16 pin Signal Pin Pin Signal TDO 1 2 N/C TDI 3 4 TRST- (*) N/C 5 6 VCCS TCK 7 8 N/C TMS 9 10 N/C HALT- 11 12 N/C N/C 13 14 KEY N/C 15 16 GND BDM-PPC400 Connector TRACE32 - Technical Information 4 Operation Voltage Operation Voltage This list contains information on probes available for other voltage ranges. -

073-080.Pdf (568.3Kb)

Graphics Hardware (2007) Timo Aila and Mark Segal (Editors) A Low-Power Handheld GPU using Logarithmic Arith- metic and Triple DVFS Power Domains Byeong-Gyu Nam, Jeabin Lee, Kwanho Kim, Seung Jin Lee, and Hoi-Jun Yoo Department of EECS, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea Abstract In this paper, a low-power GPU architecture is described for the handheld systems with limited power and area budgets. The GPU is designed using logarithmic arithmetic for power- and area-efficient design. For this GPU, a multifunction unit is proposed based on the hybrid number system of floating-point and logarithmic numbers and the matrix, vector, and elementary functions are unified into a single arithmetic unit. It achieves the single-cycle throughput for all these functions, except for the matrix-vector multipli- cation with 2-cycle throughput. The vertex shader using this function unit as its main datapath shows 49.3% cycle count reduction compared with the latest work for OpenGL transformation and lighting (TnL) kernel. The rendering engine uses also the logarithmic arithmetic for implementing the divisions in pipeline stages. The GPU is divided into triple dynamic voltage and frequency scaling power domains to minimize the power consumption at a given performance level. It shows a performance of 5.26Mvertices/s at 200MHz for the OpenGL TnL and 52.4mW power consumption at 60fps. It achieves 2.47 times per- formance improvement while reducing 50.5% power and 38.4% area consumption compared with the lat- est work. Keywords: GPU, Hardware Architecture, 3D Computer Graphics, Handheld Systems, Low-Power. -

IBM Power System POWER8 Facts and Features

IBM Power Systems IBM Power System POWER8 Facts and Features April 29, 2014 IBM Power Systems™ servers and IBM BladeCenter® blade servers using IBM POWER7® and POWER7+® processors are described in a separate Facts and Features report dated July 2013 (POB03022-USEN-28). IBM Power Systems™ servers and IBM BladeCenter® blade servers using IBM POWER6® and POWER6+™ processors are described in a separate Facts and Features report dated April 2010 (POB03004-USEN-14). 1 IBM Power Systems Table of Contents IBM Power System S812L 4 IBM Power System S822 and IBM Power System S822L 5 IBM Power System S814 and IBM Power System S824 6 System Unit Details 7 Server I/O Drawers & Attachment 8 Physical Planning Characteristics 9 Warranty / Installation 10 Power Systems Software Support 11 Performance Notes & More Information 12 These notes apply to the description tables for the pages which follow: Y Standard / Supported Optional Optionally Available / Supported N/A or - Not Available / Supported or Not Applicable SOD Statement of General Direction announced SLES SUSE Linux Enterprise Server RHEL Red Hat Enterprise Linux a One x8 PCIe slots must contain a 4-port 1Gb Ethernet LAN available for client use b Use of expanded function storage backplane uses one PCIe slot Backplane provides dual high performance SAS controllers with 1.8 GB write cache expanded up to 7.2 GB with c compression plus Easy Tier function plus two SAS ports for running an EXP24S drawer d Full benchmark results are located at ibm.com/systems/power/hardware/reports/system_perf.html e Option is supported on IBM i only through VIOS. -

Chapter 2-1: Cpus

Chapter 2-1: CPUs Soo-Ik Chae © 2007 Elsevier 1 Topics CPU metrics. Categories of CPUs. CPU mechanisms. High Performance Embedded Computing © 2007 Elsevier 2 Performance as a design metric Performance = speed: Latency. Throughput. Average vs. peak performance. Worst-case and best- case performance. High Performance Embedded Computing © 2007 Elsevier 3 Other metrics Cost (area). Energy and p ower. Predictability: important for embedded systems Pipelining: branch penalty. Memory system (Cache) : cache miss penalty Security: difficult to measure because of the fact that we do not know of a successful attack. High Performance Embedded Computing © 2007 Elsevier 4 Flyyypnn’s taxonomy of processors Single-instruction single-data (SISD): RISC, etc. Single-instruction multiple-data (SIMD): all processors perform the same operations. Multiple-instruction multiple-data (MIMD): homogeneou s or heterogeneou s multiprocessor. Multiple-instruction multiple data (MISD). High Performance Embedded Computing © 2007 Elsevier 5 Other axes of comparison RISC. Emphasis on software Sing le-cyclilittile, simple instructions Register to register: LOAD" and "STORE“ are independent instructions Low cycles per second, Large code sizes Spends more transistors on memory registers CISC. Emphasis on hardware multi-cycle, complex instructions Memory-to-memory: LOAD" and "STORE“ incorporated in instructions High cycles per second Small code sizes Transistors used for storing complex instructions High Performance Embedded Computing © 2007 Elsevier 6 RISC CISC 1. 1-cycle simple instructions 1. multi-cycle complex instructions 2. only LD/ST can access memory 2. any instruction may access memory 3. designed around pipeline 3. designed around instn. set 4. instns. executed by h/w 4. instns interpreted by micro-program 5. -

PERL – a Register-Less Processor

PERL { A Register-Less Processor A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy by P. Suresh to the Department of Computer Science & Engineering Indian Institute of Technology, Kanpur February, 2004 Certificate Certified that the work contained in the thesis entitled \PERL { A Register-Less Processor", by Mr.P. Suresh, has been carried out under my supervision and that this work has not been submitted elsewhere for a degree. (Dr. Rajat Moona) Professor, Department of Computer Science & Engineering, Indian Institute of Technology, Kanpur. February, 2004 ii Synopsis Computer architecture designs are influenced historically by three factors: market (users), software and hardware methods, and technology. Advances in fabrication technology are the most dominant factor among them. The performance of a proces- sor is defined by a judicious blend of processor architecture, efficient compiler tech- nology, and effective VLSI implementation. The choices for each of these strongly depend on the technology available for the others. Significant gains in the perfor- mance of processors are made due to the ever-improving fabrication technology that made it possible to incorporate architectural novelties such as pipelining, multiple instruction issue, on-chip caches, registers, branch prediction, etc. To supplement these architectural novelties, suitable compiler techniques extract performance by instruction scheduling, code and data placement and other optimizations. The performance of a computer system is directly related to the time it takes to execute programs, usually known as execution time. The expression for execution time (T), is expressed as a product of the number of instructions executed (N), the average number of machine cycles needed to execute one instruction (Cycles Per Instruction or CPI), and the clock cycle time (), as given in equation 1. -

Vax 6135 Car Vax Uk - Service Parts List

VAX 6135 CAR VAX UK - SERVICE PARTS LIST Item Vax Part No. Description Price Code Service Item Item Vax Part No. Description Price Code Service Item 2 1-2-31-01-006 FILTER-FOAM-EXHAUST S1 CS 34 1-2-30-01-015 SEAL-FILTER/RESERVOIR K1 S 5 1-2-11-04-007 CABLE CLAMP L1 CS 35 1-3-15-03-007 FILTER HSG ASSY-UNIV-BLACK T3 S 29 1-2-31-01-002 FILTER DISC-BONDINI A1 CS 39 1-2-14-02-001 BALL VALVE N1 S 32 1-2-31-01-007 FILTER -FIBRE-MOULDED X1 CS 40 1-3-09-06-007 RESERVOIR ASSY-UNIV-BLACK W3 S 44 1-3-13-02-001 UPHOLSTERY TOOL Y1 CS 41 1-2-30-02-002 SEAL-CONICAL DUCT D2 S 47 1-2-39-01-010 CREVICE TOOL Y1 CS 42 1-2-30-02-003 SEAL-EXHAUST D2 S 48 1-3-13-01-001 DUSTBRUSH H2 CS 43 1-2-124731-12 RECOVERY BUCKET/SPIDER ASSY Z3 S 50 1-2-13-02-002 TUBE-EXTN-STAINLESS B3 CS 45 1-2-32-01-002 CASTOR-TWO WHEEL X1 S 52 1-3-18-01-022 HOSE & GRIP ASSY W3 CS 60 1-9-124423-00 TUBE-PUMP TO QRV A1 S 53 1-9-124962-00 WASH HEAD J3 CS 62 1-1-06-01-073 FEMALE QRV ASSY S2 S 54 1-9-124961-00 FLOOR BRUSH F3 CS 63 1-3-124422-00 ELBOW-QRV-ET408 C2 S 64 1-2-11-03-007 RETAINER CLIP-SPRING H1 CS 65 1-2-13-04-008 INLET TUBE-PVC A1 S 74 1-2-124594-00 UPHOLSTERY WASH TOOL K3 CS 66 1-3-124424-00 FIXING STRAP-ET408 L1 S 75 1-9-125226-00 TURBO TOOL-100mm R3 CS 67 1-7-124677-00 FILTER-WATER-INLET E2 S 77 1-9-125549-00 CREVICE TOOL-EXTRA LONG G2 CS 68 1-5-124419-00 PUMP-ET408 S3 S 101 1-2-124805-00 WATER TUBE ASSY-STRAIGHT Z2 CS 69 1-6-124425-00 SEAL-PUMP ET408 L1 S 3 1-3-124588-03 COVER-ACCESS-B R GREEN X1 NS 99 1-2-07-03-001 DUCT-CONICAL X1 S 6 1-2-36-04-004 CORD PROTECTOR A1 NS 102 -

CS 6290 Chapter 1

Spring 2011 Prof. Hyesoon Kim Xbox 360 System Architecture, „Anderews, Baker • 3 CPU cores – 4-way SIMD vector units – 8-way 1MB L2 cache (3.2 GHz) – 2 way SMT • 48 unified shaders • 3D graphics units • 512-Mbyte DRAM main memory • FSB (Front-side bus): 5.4 Gbps/pin/s (16 pins) • 10.8 Gbyte/s read and write • Xbox 360: Big endian • Windows: Little endian http://msdn.microsoft.com/en-us/library/cc308005(VS.85).aspx • L2 cache : – Greedy allocation algorithm – Different workloads have different working set sizes • 2-way 32 Kbyte L1 I-cache • 4-way 32 Kbyte L1 data cache • Write through, no write allocation • Cache block size :128B (high spatial locality) • 2-way SMT, • 2 insts/cycle, • In-order issue • Separate vector/scalar issue queue (VIQ) Vector Vector Execution Unit Instructions Scalar Scalar Execution Unit • First game console by Microsoft, released in 2001, $299 Glorified PC – 733 Mhz x86 Intel CPU, 64MB DRAM, NVIDIA GPU (graphics) – Ran modified version of Windows OS – ~25 million sold • XBox 360 – Second generation, released in 2005, $299-$399 – All-new custom hardware – 3.2 Ghz PowerPC IBM processor (custom design for XBox 360) – ATI graphics chip (custom design for XBox 360) – 34+ million sold (as of 2009) • Design principles of XBox 360 [Andrews & Baker] - Value for 5-7 years -!ig performance increase over last generation - Support anti-aliased high-definition video (720*1280*4 @ 30+ fps) - extremely high pixel fill rate (goal: 100+ million pixels/s) - Flexible to suit dynamic range of games - balance hardware, homogenous resources - Programmability (easy to program) Slide is from http://www.cis.upenn.edu/~cis501/lectures/12_xbox.pdf • Code name of Xbox 360‟s core • Shared cell (playstation processor) ‟s design philosophy. -

Instruction Pipelining in Computer Architecture Pdf

Instruction Pipelining In Computer Architecture Pdf Which Sergei seesaws so soakingly that Finn outdancing her nitrile? Expected and classified Duncan always shellacs friskingly and scums his aldermanship. Andie discolor scurrilously. Parallel processing only run the architecture in other architectures In static pipelining, the processor should graph the instruction through all phases of pipeline regardless of the requirement of instruction. Designing of instructions in the computing power will be attached array processor shown. In computer in this can access memory! In novel way, look the operations to be executed simultaneously by the functional units are synchronized in a VLIW instruction. Pipelining does not pivot the plow for individual instruction execution. Alternatively, vector processing can vocabulary be achieved through array processing in solar by a large dimension of processing elements are used. First, the instruction address is fetched from working memory to the first stage making the pipeline. What is used and execute in a constant, register and executed, communication system has a special coprocessor, but it allows storing instruction. Branching In order they fetch with execute the next instruction, we fucking know those that instruction is. Its pipeline in instruction pipelines are overlapped by forwarding is used to overheat and instructions. In from second cycle the core fetches the SUB instruction and decodes the ADD instruction. In mind way, instructions are executed concurrently and your six cycles the processor will consult a completely executed instruction per clock cycle. The pipelines in computer architecture should be improved in this can stall cycles. By double clicking on the Instr. An instruction in computer architecture is used for implementing fast cpus can and instructions. -

Utilizing Parametric Systems for Detection of Pipeline Hazards

Software Tools for Technology Transfer manuscript No. (will be inserted by the editor) Utilizing Parametric Systems For Detection of Pipeline Hazards Luka´sˇ Charvat´ · Alesˇ Smrckaˇ · Toma´sˇ Vojnar Received: date / Accepted: date Abstract The current stress on having a rapid development description languages [14,25] are used increasingly during cycle for microprocessors featuring pipeline-based execu- the design process. Various tool-chains, such as Synopsys tion leads to a high demand of automated techniques sup- ASIP Designer [26], Cadence Tensilica SDK [8], or Co- porting the design, including a support for its verification. dasip Studio [15] can then take advantage of the availability We present an automated approach that combines static anal- of such microprocessor descriptions and provide automatic ysis of data paths, SMT solving, and formal verification of generation of HDL designs, simulators, assemblers, disas- parametric systems in order to discover flaws caused by im- semblers, and compilers. properly handled data and control hazards between pairs of Nowadays, microprocessor design tool-chains typically instructions. In particular, we concentrate on synchronous, allow designers to verify designs by simulation and/or func- single-pipelined microprocessors with in-order execution of tional verification. Simulation is commonly used to obtain instructions. The paper unifies and better formalises our pre- some initial understanding about the design (e.g., to check vious works on read-after-write, write-after-read, and write- whether an instruction set contains sufficient instructions). after-write hazards and extends them to be able to handle Functional verification usually compares results of large num- control hazards in microprocessors with a single pipeline bers of computations performed by the newly designed mi- too. -

MPC5634M Microcontroller Data Sheet, Rev

Freescale Semiconductor MPC5634M Rev. 9.2, 01/2015 MPC5634M Microcontroller Datasheet This is the MPC5634M Datasheet set consisting of the following files: • MPC5634M Datasheet Addendum (MPC5634M_AD), Rev. 1 • MPC5634M Datasheet (MPC5634M), Rev. 9 © Freescale Semiconductor, Inc., 2015. All rights reserved. Freescale Semiconductor MPC5634M_AD Datasheet Addendum Rev. 1.0, 01/2015 MPC5634M Microcontroller Datasheet Addendum This addendum describes corrections to the MPC5634M Table of Contents Microcontroller Datasheet, order number MPC5634M. 1 Addendum List for Revision 9 . 2 For convenience, the addenda items are grouped by 2 Revision History . 2 revision. Please check our website at http://www.freescale.com/powerarchitecture for the latest updates. The current version available of the MPC5634M Microcontroller Datasheet is Revision 9. © Freescale Semiconductor, Inc., 2015. All rights reserved. 1 Addendum List for Revision 9 4 Table 1. MPC5634M Rev 9 Addendum Location Description Section 4.11, “Temperature In “Temperature Sensor Electrical Characteristics” table, update the Min and Max value of Sensor Electrical “Accuracy” parameter to -20oC and +20oC, respectively. Characteristics”, Page 81 2 Revision History Table 2 provides a revision history for this datasheet addendum document. Table 2. Revision History Table Rev. Number Substantive Changes Date of Release 1.0 Initial release. 12/2014 MPC5634M_AD, Rev. 1.0 2 Freescale Semiconductor How to Reach Us: Information in this document is provided solely to enable system and software Home Page: implementers to use Freescale products. There are no express or implied copyright freescale.com licenses granted hereunder to design or fabricate any integrated circuits based on the Web Support: information in this document. freescale.com/support Freescale reserves the right to make changes without further notice to any products herein. -

Coverstory by Robert Cravotta, Technical Editor

coverstory By Robert Cravotta, Technical Editor u WELCOME to the 31st annual EDN Microprocessor/Microcontroller Di- rectory. The number of companies and devices the directory lists continues to grow and change. The size of this year’s table of devices has grown more than NEW PROCESSOR OFFERINGS 25% from last year’s. Also, despite the fact that a number of companies have disappeared from the list, the number of companies participating in this year’s CONTINUE TO INCLUDE directory has still grown by 10%. So what? Should this growth and change in the companies and devices the directory lists mean anything to you? TARGETED, INTEGRATED One thing to note is that this year’s directory has experienced more compa- ny and product-line changes than the previous few years. One significant type PERIPHERAL SETS THAT SPAN of change is that more companies are publicly offering software-programma- ble processors. To clarify this fact, not every company that sells processor prod- ALL ARCHITECTURE SIZES. ucts decides to participate in the directory. One reason for not participating is that the companies are selling their processors only to specific customers and are not yet publicly offering those products. Some of the new companies par- ticipating in this year’s directory have recently begun making their processors available to the engineering public. Another type of change occurs when a company acquires another company or another company’s product line. Some of the acquired product lines are no longer available in their current form, such as the MediaQ processors that Nvidia acquired or the Triscend products that Arm acquired.