High Accuracy Real-Time GPS Synchronized Frequency Measurement Device for Wide-Area Power Grid Monitoring

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Century of WWV

Volume 124, Article No. 124025 (2019) https://doi.org/10.6028/jres.124.025 Journal of Research of the National Institute of Standards and Technology A Century of WWV Glenn K. Nelson National Institute of Standards and Technology, Radio Station WWV, Fort Collins, CO 80524, USA [email protected] WWV was established as a radio station on October 1, 1919, with the issuance of the call letters by the U.S. Department of Commerce. This paper will observe the upcoming 100th anniversary of that event by exploring the events leading to the founding of WWV, the various early experiments and broadcasts, its official debut as a service of the National Bureau of Standards, and its role in frequency and time dissemination over the past century. Key words: broadcasting; frequency; radio; standards; time. Accepted: September 6, 2019 Published: September 24, 2019 https://doi.org/10.6028/jres.124.025 1. Introduction WWV is the high-frequency radio broadcast service that disseminates time and frequency information from the National Institute of Standards and Technology (NIST), part of the U.S. Department of Commerce. WWV has been performing this service since the early 1920s, and, in 2019, it is celebrating the 100th anniversary of the issuance of its call sign. 2. Radio Pioneers Other radio transmissions predate WWV by decades. Guglielmo Marconi and others were conducting radio research in the late 1890s, and in 1901, Marconi claimed to have received a message sent across the Atlantic Ocean, the letter “S” in telegraphic code [1]. Radio was called “wireless telegraphy” in those days and was, if not commonplace, viewed as an emerging technology. -

KHF 950/990 HF Communications Transceiver PILOT’S GUIDE and DIRECTORY of HF SERVICES

KHF 950/990 HF Communications Transceiver PILOT’S GUIDE AND DIRECTORY OF HF SERVICES A Table of Contents INTRODUCTION KHF 950/990 COMMUNICATIONS TRANSCEIVER . .I SECTION I CHARACTERISTICS OF HF SSB WITH ALE . .1-1 ACRONYMS AND DEFINITIONS . .1-1 REFERENCES . .1-1 HF SSB COMMUNICATIONS . .1-1 FREQUENCY . .1-2 SKYWAVE PROPAGATION . .1-3 WHY SINGLE SIDEBAND IS IMPORTANT . .1-9 AMPLITUDE MODULATION (AM) . .1-9 SINGLE SIDEBAND OPERATION . .1-10 SINGLE SIDEBAND (SSB) . .1-10 SUPPRESSED CARRIER VS. REDUCED CARRIER . .1-10 SIMPLEX & SEMI-DUPLEX OPERATION . .1-11 AUTOMATIC LINK ESTABLISHMENT (ALE) . .1-11 FUNCTIONS OF HF RADIO AUTOMATION . .1-11 ALE ASSURES BEST COMM LINK AUTOMATICALLY . .1-12 SECTION II KHF 950/990 SYSTEM DESCRIPTION. .2-1 KCU 1051 CONTROL DISPLAY UNIT . .2-1 KFS 594 CONTROL DISPLAY UNIT . .2-3 KCU 951 CONTROL DISPLAY UNIT . .2-5 KHF 950 REMOTE UNITS . .2-6 KAC 952 POWER AMPLIFIER/ANT COUPLER .2-6 KTR 953 RECEIVER/EXITER . .2-7 ADDITIONAL KHF 950 INSTALLATION OPTIONS .2-8 SINGLE KHF 950 SYSTEM CONFIGURATION .2-9 KHF 990 REMOTE UNITS . .2-10 KAC 992 PROBE/ANTENNA COUPLER . .2-10 KTR 993 RECEIVER/EXITER . .2-11 SINGLE KHF 990 SYSTEM CONFIGURATION . .2-12 Rev. 0 Dec/96 KHF 950/990 Pilots Guide Toc-1 Table of Contents SECTION III OPERATING THE KHF 950/990 . .3-1 KHF 950/990 GENERAL OPERATING INFORMATION . .3-1 PREFLIGHT INSPECTION . .3-1 ANTENNA TUNING . .3-2 FAULT INDICATION . .3-2 TUNING FAULTS . .3-3 KHF 950/990 CONTROLS-GENERAL . .3-3 KCU 1051 CONTROL DISPLAY UNIT OPERATION . -

Time Signal Stations 1By Michael A

122 Time Signal Stations 1By Michael A. Lombardi I occasionally talk to people who can’t believe that some radio stations exist solely to transmit accurate time. While they wouldn’t poke fun at the Weather Channel or even a radio station that plays nothing but Garth Brooks records (imagine that), people often make jokes about time signal stations. They’ll ask “Doesn’t the programming get a little boring?” or “How does the announcer stay awake?” There have even been parodies of time signal stations. A recent Internet spoof of WWV contained zingers like “we’ll be back with the time on WWV in just a minute, but first, here’s another minute”. An episode of the animated Power Puff Girls joined in the fun with a skit featuring a TV announcer named Sonny Dial who does promos for upcoming time announcements -- “Welcome to the Time Channel where we give you up-to- the-minute time, twenty-four hours a day. Up next, the current time!” Of course, after the laughter dies down, we all realize the importance of keeping accurate time. We live in the era of Internet FAQs [frequently asked questions], but the most frequently asked question in the real world is still “What time is it?” You might be surprised to learn that time signal stations have been answering this question for more than 100 years, making the transmission of time one of radio’s first applications, and still one of the most important. Today, you can buy inexpensive radio controlled clocks that never need to be set, and some of us wear them on our wrists. -

STANDARD FREQUENCIES and TIME SIGNALS (Question ITU-R 106/7) (1992-1994-1995) Rec

Rec. ITU-R TF.768-2 1 SYSTEMS FOR DISSEMINATION AND COMPARISON RECOMMENDATION ITU-R TF.768-2 STANDARD FREQUENCIES AND TIME SIGNALS (Question ITU-R 106/7) (1992-1994-1995) Rec. ITU-R TF.768-2 The ITU Radiocommunication Assembly, considering a) the continuing need in all parts of the world for readily available standard frequency and time reference signals that are internationally coordinated; b) the advantages offered by radio broadcasts of standard time and frequency signals in terms of wide coverage, ease and reliability of reception, achievable level of accuracy as received, and the wide availability of relatively inexpensive receiving equipment; c) that Article 33 of the Radio Regulations (RR) is considering the coordination of the establishment and operation of services of standard-frequency and time-signal dissemination on a worldwide basis; d) that a number of stations are now regularly emitting standard frequencies and time signals in the bands allocated by this Conference and that additional stations provide similar services using other frequency bands; e) that these services operate in accordance with Recommendation ITU-R TF.460 which establishes the internationally coordinated UTC time system; f) that other broadcasts exist which, although designed primarily for other functions such as navigation or communications, emit highly stabilized carrier frequencies and/or precise time signals that can be very useful in time and frequency applications, recommends 1 that, for applications requiring stable and accurate time and frequency reference signals that are traceable to the internationally coordinated UTC system, serious consideration be given to the use of one or more of the broadcast services listed and described in Annex 1; 2 that administrations responsible for the various broadcast services included in Annex 2 make every effort to update the information given whenever changes occur. -

Time and Frequency Users' Manual

,>'.)*• r>rJfl HKra mitt* >\ « i If I * I IT I . Ip I * .aference nbs Publi- cations / % ^m \ NBS TECHNICAL NOTE 695 U.S. DEPARTMENT OF COMMERCE/National Bureau of Standards Time and Frequency Users' Manual 100 .U5753 No. 695 1977 NATIONAL BUREAU OF STANDARDS 1 The National Bureau of Standards was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, a technical (3) basis for equity in trade, and (4) technical services to pro- mote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research the Institute for Applied Technology, the Institute for Computer Sciences and Technology, the Office for Information Programs, and the Office of Experimental Technology Incentives Program. THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consist- ent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essen- tial services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of the Office of Measurement Services, and the following center and divisions: Applied Mathematics -

Radiorama N.58.Pdf

Panorama radiofonico internazionale n. 58 Dal 1982 dalla parte del Radioascolto Rivista telematica edita in proprio dall'AIR Associazione Italiana Radioascolto c.p. 1338 - 10100 Torino AD www.air-radio.it lll’angolo delle QSL storiche … radiorama PANORAMA RADIOFONICO INTERNAZIONALE organo ufficiale dell’A.I.R. Associazione Italiana Radioascolto recapito editoriale: radiorama - C. P. 1338 - 10100 TORINO AD e-mail: [email protected] AIR - radiorama - Responsabile Organo Ufficiale: Giancarlo VENTURI - Responsabile impaginazione radiorama: Bruno PECOLATTO - Responsabile Blog AIR-radiorama: i singoli Autori - Responsabile sito web: Emanuele PELICIOLI ------------------------------------------------- Il presente numero di radiorama e' pubblicato in rete in proprio dall'AIR Associazione Italiana Radioascolto, tramite il server Aruba con sede in località Palazzetto, 4 - 52011 Bibbiena Stazione (AR). Non costituisce testata giornalistica, non ha carattere periodico ed è aggiornato secondo la disponibilità e la reperibilità dei materiali. Pertanto, non può essere considerato in alcun modo un prodotto editoriale ai sensi della L. n. 62 del 7.03.2001. La responsabilità di quanto pubblicato è esclusivamente dei singoli Autori. L'AIR-Associazione Italiana Radioascolto, costituita con atto notarile nel 1982, ha attuale sede legale presso il Presidente p.t. avv. Giancarlo Venturi, viale M.F. Nobiliore, 43 - 00175 Roma SR1 EUROPAWELLE SAAR 1421kHz, GERMANIA (anni ‘80) RUBRICHE : Pirate News - Eventi Collabora con noi, invia i tuoi articoli come da protocollo. Il Mondo in Cuffia - Scala parlante e-mail: [email protected] Grazie e buona lettura !!!! Vita associativa - Attività Locale Segreteria, Casella Postale 1338 10100 Torino A.D. radiorama on web - numero 58 e-mail: [email protected] ------------------------ [email protected] Rassegna stampa – Giampiero Bernardini SOMMARIO e-mail: [email protected] ------------------------ In copertina : "Musica a richiesta - Radio Trst", opera di Vilma Coti (cortesia Rubrica FM – Giampiero Bernardini Dorigo Valdi). -

Nbs Technical Note 674 National Bureau of Standards

NBS TECHNICAL NOTE 674 NATIONAL BUREAU OF STANDARDS The National Bureau of Standards' was established by an act of Congress March 3, ,1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs. THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of the Office of Measurement Services, the Office of Radiation Measurement and the following Center and divisions: Applied Mathematics - Electricity - Mechanics - Heat - Optical Physics - Center for Radiation Research: Nuclear Sciences; Applied Radiation - Laboratory Astrophysics * - Cryogenics ' - Electromagnetics - Time and Frequency *. THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. -

Wwvb Time Code

Time & Freq Sp Publication A 2/13/02 5:24 PM Page 1 NIST Special Publication 432, 2002 Edition NIST Time and Frequency Services Michael A. Lombardi Time & Freq Sp Publication A 4/22/03 1:32 PM Page 3 NIST Special Publication 432 (Minor text revisions made in April 2003) NIST Time and Frequency Services Michael A. Lombardi Time and Frequency Division Physics Laboratory (Supersedes NIST Special Publication 432, dated June 1991) January 2002 U.S. DEPARTMENT OF COMMERCE Donald L. Evans, Secretary TECHNOLOGY ADMINISTRATION Phillip J. Bond, Under Secretary for Technology NATIONAL INSTITUTE OF STANDARDS AND TECHNOLOGY Arden L. Bement, Jr., Director Time & Freq Sp Publication A 2/13/02 5:24 PM Page 4 Certain commercial entities, equipment, or materials may be identified in this document in order to describe an experimental procedure or concept adequately. Such identification is not intended to imply recommendation or endorsement by the National Institute of Standards and Technology, nor is it intended to imply that the entities, materials, or equipment are necessarily the best available for the purpose. NATIONAL INSTITUTE OF STANDARDS AND TECHNOLOGY SPECIAL PUBLICATION 432 (SUPERSEDES NIST SPECIAL PUBLICATION 432, DATED JUNE 1991) NATL. INST.STAND.TECHNOL. SPEC. PUBL. 432, 76 PAGES (JANUARY 2002) CODEN: NSPUE2 U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 2002 For sale by the Superintendent of Documents, U.S. Government Printing Office Website: bookstore.gpo.gov Phone: (202) 512-1800 Fax: (202) 512-2250 Mail: Stop SSOP,Washington, DC 20402-0001 -

Measurements of Propagation Delays Between WWV/WWVH and Anchorage, Alaska Whitham D

Measurements of Propagation Delays Between WWV/WWVH and Anchorage, Alaska Whitham D. Reeve 1. Introduction The measurements described here show that the propagation delays between WWV or WWVH time service broadcast stations and a receiver in Anchorage, Alaska are discernible in an audio recording. The propagation delays are on the order of 13 to 15 ms. These measurements are an initial step toward determining the time resolution that might be attainable while analyzing audio recordings of Jupiter s-bursts and other high frequency radio phenomena. It is noted that measuring easily recognizable audio tones (as in this paper) are presumably much easier than measuring noise-like extraterrestrial radio emissions. As described in detail below, post-processing measurements with sub-millisecond resolution can be achieved when the received signal voltage amplitudes are roughly > 6 dB above background noise. At lower voltage signal-to-noise ratios, the ability to recognize the start and end intervals of the WWV/WWVH tones is degraded but measurements with millisecond resolution are still possible. Summary of measurement results: Measurement Measured value Remarks Soundcard timing accuracy +10 ppm measured over 0.2 to 3 minute intervals using PPS Excess propagation delay 0 to +4 ms Referred to calculated delay PPS interval 1.000 010 s Typical PPS pulse width 100 ms Measured between leading to trailing edges Resolution 1 μs Waveform displayed in Goldwave audio software WWV or WWVH second tock width 5 to 8 ms Transmitted width is 5 ms WWV or WWVH minute tone width 800.3 to 800.4 ms Transmitted width is 800 ms 2. -

Compleat Idiot's Guide to Getting Started

Compleat Idiot’s Guide to Getting Started Three “Must” Tips to Catch the World World band radio is your unfiltered Imagine the chaos if each station connection to what’s going on, but it used its own local time for sched- differs from conventional radio. Here uling. In England, 9:00 PM is differ- are three “must” tips to get started. ent from nine in the evening in Japan or Canada. How would anybody “Must” #1: World Time and Day know when to tune in? World band schedules use a single time, World Time. After all, world World Time, or Coordinated Univer- band radio is global, with stations sal Time (UTC), is also known as broadcasting around-the-clock Greenwich Mean Time (GMT) or, in from virtually every time zone. the military, “Zulu.” It is announced COMPLEAT IDIOT’S GUIDE TO GETTING STARTED 2 in 24-hour format, so 2 PM is 1400 (“fourteen hundred”) hours. There are four easy ways to know World Time. First, around North America tune to one of the standard time stations, such as WWV in Colorado and WWVH in Hawaii or CHU in Ottawa. WWV and WWVH are on 5000, 10000 and 15000 kHz, with WWV also on 2500 and 20000 kHz; CHU is on 3330, 7335 and 14670 kHz. Second, tune to a major international broadcaster, such as the BBC What happens at World Service or Voice of America. Most announce World Time at midnight, World the hour. Time? A new Third, on the Internet you can access World Time at various sites, including tycho.usno.navy.mil/what.html and www.nrc.ca/inms/ World Day time/cesium.shtml. -

Standard Frequencies and Time Signals Wwv and Wwvh

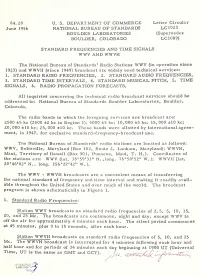

84. 20 U. S. DEPARTMENT OF COMMERCE Letter Circular June 1956 NATIONAL BUREAU OF STANDARDS LC 1023 BOULDER LABORATORIES (Supersedes BOULDER, COLORADO LC10Q9) STANDARD FREQUENCIES AND TIME SIGNALS WWV AND WWVH The National Bureau of Standards' Radio Stations WWV (in operation since 1923) and WWVH (since 1949) broadcast six widely used technical services: 1. STANDARD RADIO FREQUENCIES, 2. STANDARD AUDIO FREQUENCIES, 3. STANDARD TIME INTERVALS, 4. STANDARD MUSICAL PITCH, 5. TIME SIGNALS, 6. RADIO PROPAGATION FORECASTS. All inquiries concerning the technical radio broadcast services should be addressed to: National Bureau of Standards Boulder Laboratories, Boulder, Colorado. The radio bands in which the foregoing services are broadcast are: 2500 ±5 kc (2500 ±2 kc in Region 1); 5000 ±5 kc; 10, 000 ±5 kc; 15, 000 ±10 kc*» 20, 000 ±10 kc; 2.5, 000 ±10 kc. These bands were allotted by international agree- ment, in 1947, for exclusive standard-frequency-broadcast use. The National Bureau of Standards' radio stations are located as follows: WWV, Beltsville, Maryland (Box 182, Route 2, Lanham, Maryland); WWVH, Maui, Territory of Hawaii (Box 901, Puunene, Maui, T. H. ). Coordinates of the stations 38 °59'33" 76°50'52" are: WWV (lat. N. , long. W. ); WWVH (lat. 20°46'02" N. , long. 156°27'42" W. ). The WWV - WWVH broadcasts are a convenient means of transferring the national standard of frequency and time interval and making it readily avail- able throughout the United States and over much of the world. The broadcast program is shown schematically in Figure 1. 1. Standard Radio Frequencies : Station WWV broadcasts on standard radio frequencies of 2. -

Agilent an 1289 the Science of Timekeeping Application Note

Agilent AN 1289 The Science of Timekeeping Application Note • UTC: Official World Time • GPS: A Time Distribution Utility • Time: An Historical and Future Perspective • From Laboratory to Practical Use • Broad Applications Across Society Table of Contents 8 Introduction to the Science of Timekeeping 10 Precise Timing Applications Pervade Our Society 14 Clocks and Timekeeping 19 The Definition of the Second and Its General Importance 19 Historical Perspective 22 An Illustrative Timekeeping Example 26 UTC, Official Time for the World 30 GPS Time and UTC 31 Accuracy and Stability of UTC 36 Einstein’s Relativity and Precise Timekeeping 39 How to Access UTC 44 Future Timing Techniques 47 Global Navigation Satellite System Developments 52 UTC and the Future 53 Conclusions 54 Acknowledgments 56 Appendix A: Time and Frequency Measures Accuracy, Error, Precision, Predictability, Stability, and Uncertainty 66 Appendix B: Stability Analysis of Harrison-like Chronometers 72 Appendix C: Time and Frequency Transfer, Distribution and Dissemination Systems 82 Glossary and Definitions 85 Bibliography Agilent Technologies is grateful to the three authors of this applica- tion note for sharing their expertise. Their combined knowledge offers a resource which will undoubtedly be considered a classic reference on the science of timekeeping for decades to come. David W. Allan David W. Allan was born in Mapleton, Utah on September 25,1936. He received the B.S. and M.S. degrees in physics from Brigham Young University, Provo, Utah and from the University of Colorado, respec- tively. From 1960 until 1992 he worked at the U.S. National Institute of Standards and Technology (NIST), formerly the National Bureau of Standards (NBS).