Z5U Dielectric General Specifications

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Syfer Capacitor Basics

Syfer Technology Limited, Old Stoke Road, Arminghall, Norwich, Norfolk, NR14 8SQ, United Kingdom Tel: +44 (0) 1603 723300 Tel. (Sales): 01603 723310 Fax: +44 (0) 1603 723301 Email: [email protected] Web: www.knowlescapacitors.com Syfer Capacitor Basics What is a Capacitor ..................................................................................2 Electrode .............................................................................................2 Dielectric .............................................................................................2 Construction ........................................................................................2 MLCC Uses ..............................................................................................3 Limitations and Factors for Consideration ....................................................3 Dielectric Types .......................................................................................4 X7R.....................................................................................................4 X5R.....................................................................................................5 X8R.....................................................................................................5 2C1 (BZ) and 2X1 (BX) .........................................................................5 C0G ....................................................................................................5 High Q .................................................................................................5 -

Ltc3225/Ltc3225-1

LTC3225/LTC3225-1 150mA Supercapacitor Charger FEATURES DESCRIPTION n Low Noise Constant Frequency Charging of Two The LTC®3225/LTC3225-1 are programmable supercapaci- Series Supercapacitors tor chargers designed to charge two supercapacitors in n Automatic Cell Balancing Prevents Capacitor series to a selectable fi xed output voltage (4.8V/5.3V for Overvoltage During Charging the LTC3225 and 4V/4.5V for the LTC3225-1) from input n Programmable Charge Current (Up to 150mA) supplies as low as 2.8V to 5.5V. Automatic cell balancing n Selectable 2.4V or 2.65V Regulation per Cell prevents overvoltage damage to either supercapacitor. No (LTC3225) balancing resistors are required. n Selectable 2V or 2.25V Regulation per Cell Low input noise, low quiescent current and low external (LTC3225-1) parts count (one fl ying capacitor, one bypass capacitor at n Automatic Recharge V and one programming resistor) make the LTC3225/ n I = 20μA in Standby Mode IN VIN LTC3225-1 ideally suited for small battery-powered n I < 1μA When Input Supply is Removed COUT applications. n No Inductors n Tiny Application Circuit (2mm × 3mm DFN Package, Charge current level is programmed with an external All Components <1mm High) resistor. When the input supply is removed, the LTC3225/ LTC3225-1 automatically enter a low current state, drawing APPLICATIONS less than 1μA from the supercapacitors. The LTC3225/LTC3225-1 are available in a 10-lead 2mm n Current Limited Applications with High Peak Power × 3mm DFN package. Loads (LED Flash, PCMCIA Tx Bursts, HDD Bursts, L, LT, LTC and LTM are registered trademarks and ThinSOT is a trademark of Linear GPRS/GSM Transmitter) Technology Corporation. -

Synthesis of Nano-Ceramics for Supercapacitors

University of Wollongong Research Online University of Wollongong Thesis Collection 1954-2016 University of Wollongong Thesis Collections 2014 Synthesis of nano-ceramics for supercapacitors Azrin Akhter Chowdhury University of Wollongong Follow this and additional works at: https://ro.uow.edu.au/theses University of Wollongong Copyright Warning You may print or download ONE copy of this document for the purpose of your own research or study. The University does not authorise you to copy, communicate or otherwise make available electronically to any other person any copyright material contained on this site. You are reminded of the following: This work is copyright. Apart from any use permitted under the Copyright Act 1968, no part of this work may be reproduced by any process, nor may any other exclusive right be exercised, without the permission of the author. Copyright owners are entitled to take legal action against persons who infringe their copyright. A reproduction of material that is protected by copyright may be a copyright infringement. A court may impose penalties and award damages in relation to offences and infringements relating to copyright material. Higher penalties may apply, and higher damages may be awarded, for offences and infringements involving the conversion of material into digital or electronic form. Unless otherwise indicated, the views expressed in this thesis are those of the author and do not necessarily represent the views of the University of Wollongong. Recommended Citation Chowdhury, Azrin Akhter, Synthesis of nano-ceramics for supercapacitors, Doctor of Philosophy thesis, Engineering Materials Institute, University of Wollongong, 2014. https://ro.uow.edu.au/theses/4314 Research Online is the open access institutional repository for the University of Wollongong. -

Suggestion of the Supercapacitor(EDLC) Application to the Electrical Characteristic Tester

Supercapacitor (EDLC) Application Note No. C2M1CXS-163A(E) Suggestion of the Supercapacitor(EDLC) Application to the Electrical Characteristic Tester 1. Summary Supercapacitor, also known as EDLC or supercap, has higher-capacity than ceramic capacitor or electrolytic capacitor. And supercapacitor is an energy storage device having longer life than a battery. In addition, Murata’s supercapacitor can handle the output power up to 50W by realizing super low ESR approximately 40mΩ (DMF series example) At the measurement environment that a high peak electric current runs through the load instantly, our supercapacitor can assist such peak current. By this effect, it is possible to downsize Fig.3 : Measurement Block Diagram with Supercapacitor and reduce power capacity of DC power supply. Besides it contributes to reduce measuring equipment cost and save the Fig.4 and Fig.5 shows each part waveform. electric power of the facilities. Top(Yellow):Load current, Middle(Green):Power line voltage, Bottom(Purple):DC power supply current. 2. Benefits Fig.4: DC power supply only. ①Downsize the DC power supply Fig.5: Supercap is added to DC power supply. Even if the power supply capacity cannot support a peak current, The effect of supercap can be confirmed because the fluctuation it does not matter because supercap can assist it. ②Supercapacitor as a power source of the input voltage is smaller and the peak current of power Because supercap can be charged quickly, it is possible to use supply decreases. supercap as power source at the time of measurement. ③Reduce the cost and Save power of measurement equipment. ④Can be mounted on limited area because of its thinner and smaller shape. -

Surface Mount Ceramic Capacitor Products

Surface Mount Ceramic Capacitor Products 082621-1 IMPORTANT INFORMATION/DISCLAIMER All product specifications, statements, information and data (collectively, the “Information”) in this datasheet or made available on the website are subject to change. The customer is responsible for checking and verifying the extent to which the Information contained in this publication is applicable to an order at the time the order is placed. All Information given herein is believed to be accurate and reliable, but it is presented without guarantee, warranty, or responsibility of any kind, expressed or implied. Statements of suitability for certain applications are based on AVX’s knowledge of typical operating conditions for such applications, but are not intended to constitute and AVX specifically disclaims any warranty concerning suitability for a specific customer application or use. ANY USE OF PRODUCT OUTSIDE OF SPECIFICATIONS OR ANY STORAGE OR INSTALLATION INCONSISTENT WITH PRODUCT GUIDANCE VOIDS ANY WARRANTY. The Information is intended for use only by customers who have the requisite experience and capability to determine the correct products for their application. Any technical advice inferred from this Information or otherwise provided by AVX with reference to the use of AVX’s products is given without regard, and AVX assumes no obligation or liability for the advice given or results obtained. Although AVX designs and manufactures its products to the most stringent quality and safety standards, given the current state of the art, isolated component failures may still occur. Accordingly, customer applications which require a high degree of reliability or safety should employ suitable designs or other safeguards (such as installation of protective circuitry or redundancies) in order to ensure that the failure of an electrical component does not result in a risk of personal injury or property damage. -

Understanding Polymer and Hybrid Capacitors Advanced Capacitors Based on Conductive Polymers Maximize Performance and Reliability

WHITE PAPER Understanding Polymer and Hybrid Capacitors Advanced capacitors based on conductive polymers maximize performance and reliability The various polymer and hybrid capacitors have distinct sweet spots in terms of their ideal voltages, frequency characteristics, environmental conditions and other application requirements. In this paper, we’ll show you how to identify the best uses for each type of advanced capacitor. We’ll also highlight specific applications in which a polymer or hybrid capacitor will outperform traditional electrolytic or even ceramic capacitors. POLYMER CAPACITOR VARIETIES Polymer capacitors come in four main varieties, including the hybrid. Each type has different electrolytic and electrode Hybrid capacitor technology combines the performance benefits of materials, packaging and application targets: electrolytic and polymer capacitors. • Layered polymer aluminum capacitors use conductive Capacitors may seem simple enough, but specifying them has polymer as the electrolyte and have an aluminum cathode actually grown more complex in recent years. The reason why (see Figure 1). Depending on the specific model, these comes down to freedom of choice. The universe of capacitors capacitors cover a voltage range from 2-25V and offer has expanded greatly over the past few years, in large part capacitances between 2.2-560µF. The distinguishing because of capacitor designs that take advantage of advances electrical characteristic of these polymer capacitors is in conductive polymers. their extremely low equivalent series resistance (ESR). For example, some of our SP-Cap™ polymer capacitors have These advanced capacitors sometimes use conductive polymers ESR values as low as 3mΩ, which is among the lowest in to form the entire electrolyte. Or the conductive polymers can be used in conjunction with a liquid electrolyte in a design known as a hybrid capacitor. -

Polymer Film Capacitors Provide Needed Performance

Polymer Film Capacitors Provide Needed Performance Rick A. Price Paktron Capacitors 1205 McConville Road Lynchburg, VA 24502 Phone: 434-239-6941 Fax: 434-239-4730 Web site: http://www.panconcorp.com Abstract – Mechanical flexibility, immunity to sized components has generally removed some of the aging and stable operating characteristics are the safety margin in the designs or caused increased hallmarks of polymer film capacitors used in parasitic losses. In what seems like the ultimate power applications. validation of the superior performance characteristics of polymer film capacitors, various capacitor type There is probably not a single electronic design (tantalum, aluminum electrolytic and ceramic) engineer who has not come up with a new circuit manufacturers have now begun adding polymer design only to have it fail during bench testing elements to their products in order to enhance because it appeared that either there was a design electrical and mechanical performance. Rather than error or a faulty component had been used. In the using these polymer “hybrids”, those requiring the majority of cases it is neither; with the failure highest performance, most stable capacitors occurring because of a key component’s commercially available should choose polymer film unacceptable parasitic losses due to its reaction to capacitors for their critical applications. temperature, voltage and/or frequency variations. There is nothing more frustrating than spending Critical electronic systems used in markets such as the time troubleshooting a “defective” circuit only Military, Flight or Telecommunications require the to find the cause being a 4.7µF capacitor that has use of components with inherent reliability. No an actual effective working value of only 0.33µF. -

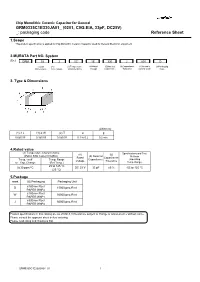

GRM0335C1E330JA01 (0201, C0G:EIA, 33Pf, DC25V) : Packaging Code Reference Sheet

Chip Monolithic Ceramic Capacitor for General GRM0335C1E330JA01_ (0201, C0G:EIA, 33pF, DC25V) _: packaging code Reference Sheet 1.Scope This product specification is applied to Chip Monolithic Ceramic Capacitor used for General Electronic equipment. 2.MURATA Part NO. System (Ex.) GRM 03 3 5C 1E 330 J A01 D (1)L/W (2)T (3)Temperature (4)Rated (5)Nominal (6)Capacitance (7)Murata’s (8)Packaging Dimensions Dimensions Characteristics Voltage Capacitance Tolerance Control Code Code 3. Type & Dimensions (Unit:mm) (1)-1 L (1)-2 W (2) T e g 0.6±0.03 0.3±0.03 0.3±0.03 0.1 to 0.2 0.2 min. 4.Rated value (3) Temperature Characteristics (4) (6) Specifications and Test (Public STD Code):C0G(EIA) (5) Nominal Methods Rated Capacitance Temp. coeff Temp. Range Capacitance (Operating Voltage Tolerance or Cap. Change (Ref.Temp.) Temp. Range) 25 to 125 °C 0±30 ppm/°C DC 25 V 33 pF ±5 % -55 to 125 °C (25 °C) 5.Package mark (8) Packaging Packaging Unit 180mm Reel D f 15000 pcs./Reel PAPER W8P2 180mm Reel W f 30000 pcs./Reel PAPER W8P1 330mm Reel J f 50000 pcs./Reel PAPER W8P2 Product specifications in this catalog are as of Mar.5,2016,and are subject to change or obsolescence without notice. Please consult the approval sheet before ordering. Please read rating and !Cautions first. GRM0335C1E330JA01-01 1 ■ Specifications and Test Methods Test Method No Item Specification (Ref. Standard:JIS C 5101, IEC60384) 1 Rated Voltage Shown in Rated value. The rated voltage is defined as the maximum voltage which may be applied continuously to the capacitor. -

How to Select a Capacitor for Power Supplies

CAPACITOR FUNDAMENTALS 301 HOW TO SELECT A CAPACITOR FOR POWER SUPPLIES 1 Capacitor Committee Upcoming Events PSMA Capacitor Committee Website, Old Fundamentals Webinars, Training Presentations and much more – https://www.psma.com/technical-forums/capacitor Capacitor Workshop “How to choose and define capacitor usage for various applications, wideband trends, and new technologies” The day before APEC, Saturday March 14 from 7:00AM to 6:00PM Capacitor Industry Session as part of APEC “Capacitors That Stand Up to the Mission Profiles of the Future – eMobility, Broadband” Tuesday March 17, 8:30AM to Noon in New Orleans Capacitor Roadmap Webinar – Timing TBD – Latest in Research and Technology Additional info here. Short Introduction of Today‘s Presenter Eduardo Drehmer Director of Marketing FILM Capacitors Background: • Over 20 years experience with knowledge on +1 732 319 1831 Manufacturing, Quality and Application of Electronic Components. [email protected] • Responsible for Technical Marketing for Film Capacitors www.tdk.com 2018-09-25 StM Short Introduction of Today‘s Presenter Edward Lobo was born in Acushnet, MA in 1943 and graduated from the University of Massachusetts in Amherst in 1967 with a BS in Chemistry. Ed worked for Magnetek, Aerovox and CDE where he is currently Chief Engineer for New Product Development. Ed Lobo Ed has served for over 52 years in Chief Engineer, New Product capacitor product development. He holds [email protected] 14 US patents involving capacitors. 4 ABSTRACT This presentation will guide individuals selecting components for their Electronic Power Supplies. Capacitors come in a wide variety of technologies, and each offers specific benefits that should be considered when designing a Power Supply circuit. -

The Important Points of Multi-Layer Ceramic Capacitor Used in Buck Converter Circuit

© 2017 ROHM Co., Ltd. No. 60AP001E Rev.001 2017.4 Application Note Switching Regulator Series The Important Points of Multi-layer Ceramic Capacitor Used in Buck Converter circuit Multi-layer Ceramic Capacitor (MLCC) with large-capacitance can be used as smoothing-capacitor in power supply circuits. Compared to other capacitor types such as an electrolytic capacitor, MLCC differs in frequency characteristics, temperature characteristics, and DC voltage characteristics. Using unmatched MLCC may not obtain required target characteristics for power supply circuit and may cause abnormal operation. This application note explains the important points while using MLCC. Figure1 shows frequency characteristics of all major types of Types of Multi-layer ceramic capacitor (MLCC) capacitors. Ripple voltage of output is expected to become smaller by using MLCC in a power circuit. However in earlier MLCC can be broadly classified into two types; for temperature power-IC designs, usage of MLCC with ultra-low ESR was not compensation and for high-dielectric constant. MLCC for considered. Therefore, phase of feedback circuit rotates too temperature compensation uses Titanium oxide (TiO2) and much at high-frequency area, causing power circuit to operate Calcium zirconate (CaZrO3) as material for its paraelectric. unstably and may cause oscillation in worst case. When MLCC Therefore, it cannot suit for capacitor with large-capacitance as has to be used at any cost, connecting a low-ohmic resistor more relative permittivity is small, about 20 to 300. Moreover, since than 10mΩ in series is recommended, and may deteriorate the relative permittivity changes linearly with temperature, the frequency characteristics. temperature coefficient can be restricted between +100 to - 4700ppm/°C by adjusting composition of the dielectric material. -

Design of a Bilayer Ceramic Capacitor with Low Temperature Coefficient of Capacitance P

Design of a bilayer ceramic capacitor with low temperature coefficient of capacitance P. Y. Foeller, J. S. Dean, I. M. Reaney, and D. C. Sinclair Citation: Applied Physics Letters 109, 082904 (2016); doi: 10.1063/1.4961616 View online: http://dx.doi.org/10.1063/1.4961616 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/109/8?ver=pdfcov Published by the AIP Publishing Articles you may be interested in Influence of temperature on the dielectric nonlinearity of BaTiO3-based multi-layer ceramic capacitors Appl. Phys. Lett. 108, 242902 (2016); 10.1063/1.4953626 Tuning of dielectric, pyroelectric and ferroelectric properties of 0.715Bi0.5Na0.5TiO3-0.065BaTiO3-0.22SrTiO3 ceramic by internal clamping AIP Advances 5, 087145 (2015); 10.1063/1.4929328 Ferroelectric phase transition and low-temperature structure fluctuations in Ba 4 Nd 2 Ti 4 Nb 6 O 30 tungsten bronze ceramics J. Appl. Phys. 105, 124110 (2009); 10.1063/1.3157147 ( 1 − x ) Ba Ti O 3 − x ( Na 0.5 K 0.5 ) Nb O 3 ceramics for multilayer ceramic capacitors Appl. Phys. Lett. 90, 132905 (2007); 10.1063/1.2717559 Dielectric behavior and microstructure of ( Bi 1 ∕ 2 Na 1 ∕ 2 ) TiO 3 – ( Bi 1 ∕ 2 K 1 ∕ 2 ) TiO 3 – BaTiO 3 lead-free piezoelectric ceramics J. Appl. Phys. 97, 104101 (2005); 10.1063/1.1890453 Reuse of AIP Publishing content is subject to the terms at: https://publishing.aip.org/authors/rights-and-permissions. Download to IP: 143.167.30.107 On: Tue, 27 Sep 2016 15:50:37 APPLIED PHYSICS LETTERS 109, 082904 (2016) Design of a bilayer ceramic capacitor with low temperature coefficient of capacitance P. -

Output Filter Capacitors Parasitic Parameters Impact on Power Quality

Output Filter Capacitors for Mission Critical Applications Parasitic Parameters Impact on Power Quality Pat Hollenbeck Field Applications Engineer Advanced Operations Abstract: The constancy and regularity of output voltage in a DC/DC output network is critical in SMPS (switched-mode power supplies) electronic performance. When different input and output voltages are required in the circuitry, output filter capacitors are required to maintain current uniformity and reduce noise. This document discusses the effect of capacitors on output power AVX Corporation quality. It evaluates and provides a comparison of different capacitor technologies, their high reliability qualification availability from www.avx.com COTS+ to space level, and their impact on the output filtering 3 / 1 5 / 2 0 1 3 capabilities in switching power supplies primarily used for mission critical applications. Output Filter Capacitors Parasitic Parameters Impact on Power Quality requirements, will increase power quality significantly. If Introduction and Overview designed well, the SMPS can approach maximum efficiency (Figure 2). The constancy of output voltage in a DC/DC output network is critical to SMPS (switched-mode power supply) electronic performance. When different output voltages are required by the circuit application, output filter capacitors are required to maintain current uniformity and reduce noise. Output capacitors play a major role in optimizing the design characteristics. Linear regulators can be used to regulate circuit voltage. Figure 2. DC waveform filtered with an output filter capacitor. (Storr 2011) Excess energy from the voltage source is dissipated as heat. Dissipation of heat is a large waste of energy and results in system inefficiency. Simulation Software In today’s designs, switching regulators in switched-mode power supplies are being used.