Troubleshooting and Repairing

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Skyfox Fighter

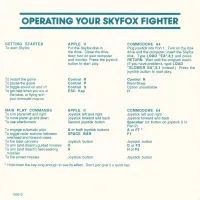

OPERATING YOUR SKYFOX FIGHTER GETTING STARTED APPLE II COMMODORE 64 To start Skyfox Put the Skyfox disk in Plug joystick into Port 1. Turn on the disk the drive. Close the drive drive and the computer; insert the Skyfox door; turn on your computer disk. Type LOAD "EA",8,1 and press and monitor. Press the joystick RETURN. Wait until the program loads. button to start play. (If you have problems, type LOAD "SLOWER EA",8,1 instead.) Press the joystick button to start play. To restart the game Control R Control R To pause the game Control P Run/Stop To toggle sound on and off Control S Option unavailable To get help when you are at ESC Key H the base, or flying with your computer map up MAIN PLAY COMMANDS APPLE II COMMODORE 64 To turn plane left and right Joystick left and right Joystick left and right To move plane up and down Joystick forward and back Joystick forward and back To use afterburners Second joystick button Spacebar (or button on joystick 2 in Port 2) To engage automatic pilot A or both joystick buttons AorF7* To toggle radar scanner between SPACE BAR F1 overhead and forward views To fire laser cannons Joystick button Joystick button To arm (and disarm) guided missiles G G or F3 To arm (and disarm) heat-seeking H H or F5 missiles To fire armed missiles Joystick button Joystick button • Hold down the key long enough to see' its effect. Don't just give it a quick tap. 103619 GETTING STARTED ATARI ST COMMODORE AMIGA To start Skyfox Put the Skyfox disk in After kickstarting your Amiga, insert the the drive and turn on the Skyfox disk in the drive. -

Commodore 64 Users Guide

INTRODUCTION Now that you've become more intimately involved with your Commo- dore 64, we want you to know that our customer support does not stop here. You may not know it, but Commodore has been in business for over 23 years. In the 1970's we introduced the first self-contained per- sonal computer (the PET). We have since become the leading computer company in many countries of the world. Our ability to design and manufacture our own computer chips allows us to bring you new and better personal computers at prices way below what you'd expect for this level of technical excellence. Commodore is committed to supporting not only you, the end user, but also the dealer you bought your computer from, magazines which publish how-to articles showing you new applications or techniques, and . importantly . software developers who produce programs on cartridge, disk and tape for use with your computer. We encourage you to establish or join a Commodore "user club" where you can learn new techniques, exchange ideas and share discoveries. We publish two separate magazines which contain programming tips, information on new products and ideas for computer applications. (See Appendix N). In North America, Commodore provides a "Commodore Information Network" on the CompuServe Information Service . to access this network, all you need is your Commodore 64 computer and our low cost VICMODEMtelephone interface cartridge (or other compatible modem). The following APPENDICEScontain charts, tables, and other informa- tion which help you program your Commodore 64 faster and more efficiently. They also include important information on the wide variety of Commodore products you may be interested in, and a bibliography listing of over 20 books and magazines which can help you develop your programming skills and keep you current on the latest information con- cerning your computer and peripherals. -

![When High-Tech Was Low-Tech : a Retrospective Look at Forward-Thinking Technologies [Multiple Exhibits]](https://docslib.b-cdn.net/cover/4438/when-high-tech-was-low-tech-a-retrospective-look-at-forward-thinking-technologies-multiple-exhibits-614438.webp)

When High-Tech Was Low-Tech : a Retrospective Look at Forward-Thinking Technologies [Multiple Exhibits]

University of South Florida Scholar Commons Library and Community-based Exhibits Library Outreach 9-1-2003 When High-Tech was Low-Tech : A Retrospective Look at Forward-Thinking Technologies [Multiple exhibits] James Anthony Schnur, Follow this and additional works at: https://scholarcommons.usf.edu/npml_outreach_exhibits Scholar Commons Citation Schnur,, James Anthony, "When High-Tech was Low-Tech : A Retrospective Look at Forward-Thinking Technologies [Multiple exhibits]" (2003). Library and Community-based Exhibits. 43. https://scholarcommons.usf.edu/npml_outreach_exhibits/43 This Presentation is brought to you for free and open access by the Library Outreach at Scholar Commons. It has been accepted for inclusion in Library and Community-based Exhibits by an authorized administrator of Scholar Commons. For more information, please contact [email protected]. When High-Tech was Low-Tech A Retrospective Look at Forward-Thinking Technologies Nelson Poynter Memorial Library University of South Florida St. Petersburg When High-Tech was Low-Tech When High-Tech was Low-Tech When High-Tech was Low-Tech The development of transistors after By the late 1970s, early “personal Before the widespread use of “floppy” World War II allowed manufacturers to computers” and game systems began to disks (in both 5¼ and 8 inch formats), build smaller, more sophisticated, and appear in homes. One of the most many early personal computers used less expensive devices. No longer did popular games of this period came from tape drives. “Personal computer consumers have to worry about Atari. This Ultra-Pong console, cassettes” usually held about 64,000 purchasing expensive tubes for heavy, released by Atari in 1977, included bytes of data and could take up to 30 bulky radios and televisions. -

The Ultimate C64 Overview Michael Steil, 25Th Chaos Communication Congress 2008

The Ultimate C64 Overview Michael Steil, http://www.pagetable.com/ 25th Chaos Communication Congress 2008 Retrocomputing is cool as never before. People play Look and Feel C64 games in emulators and listen to SID music, but few people know much about the C64 architecture A C64 only needs to be connected to power and a TV and its limitations, and what programming was like set (or monitor) to be fully functional. When turned back then. This paper attempts to give a comprehen- on, it shows a blue-on-blue theme with a startup mes- sive overview of the Commodore 64, including its in- sage and drops into a BASIC interpreter derived from ternals and quirks, making the point that classic Microsoft BASIC. In order to load and save BASIC computer systems aren't all that hard to understand - programs or use third party software, the C64 re- and that programmers today should be more aware of quires mass storage - either a “datasette” cassette the art that programming once used to be. tape drive or a disk drive like the 5.25" Commodore 1541. Commodore History Unless the user really wanted to interact with the BA- SIC interpreter, he would typically only use the BA- Commodore Business Machines was founded in 1962 SIC instructions LOAD, LIST and RUN in order to by Jack Tramiel. The company specialized on elec- access mass storage. LOAD"$",8 followed by LIST tronic calculators, and in 1976, Commodore bought shows the directory of the disk in the drive, and the chip manufacturer MOS Technology and decided LOAD"filename",8 followed by RUN would load and to have Chuck Peddle from MOS evolve their KIM-1 start a program. -

Imitation and Limitation

Fake Bit: Imitation and Limitation Brett Camper [email protected] ABSTRACT adventure and role-playing games, which are traditionally less A small but growing trend in video game development uses the action-oriented. Several lesser known NES games contributed to “obsolete” graphics and sound of 1980s-era, 8-bit microcomputers the style early on as well, such as Hudson Soft’s Faxanadu (1989) to create “fake 8-bit” games on today’s hardware platforms. This and Milon’s Secret Castle (1986), as well as Konami’s The paper explores the trend by looking at a specific case study, the Goonies II (1987). In more recent decades, the Castlevania series platform-adventure game La-Mulana, which was inspired by the from Konami has also adopted and advanced the form, from Japanese MSX computer platform. Discussion includes the Symphony of the Night (1997) on PlayStation, through Portrait of specific aesthetic traits the game adopts (as well as ignores), and Ruin (2006) for the Nintendo DS. the 8-bit technological structures that caused them in their original La-Mulana is an extremely well made title that ranks among the 1980s MSX incarnation. The role of technology in shaping finest in this genre, displaying unusual craftsmanship and aesthetics, and the persistence of such effects beyond the lifetime cohesiveness. Its player-protagonist is Professor Lemeza, an of the originating technologies, is considered as a more general archaeologist explorer charting out vast underground ruins in a “retro media” phenomenon. distant, unspecified corner of the globe (Indiana Jones is an obvious pop culture reference, but also earlier examples like H. -

Micro-KIM Tutorial

Micro-KIM Tutorial Aart J.C. Bik http://www.aartbik.com/ 1 Getting Started Perhaps reminiscing the past is a sign of getting older, but I cannot help but look back fondly at the times I learned programming machine code on the Commodore 64 in the eighties. Therefore, it is probably no surprise I still occasionally enjoy programming 6502 on the Micro-KIM, which is a modern replica of the seventies KIM1 microcomputer, made available by the well-known retro computer kits provider Briel Computers [?]. In fact, I am having so much fun with this board, I decided to write a series of tutorials on operating and programming the Micro-KIM. In this series, I assume you have already some experience with the Micro-KIM and 6502 machine code, and have read the basic documentation that is shipped with the kit. Other than that, I hope to give additional information on various topics, such as developing assembly programs, programming the display, using the RS232 port or keypad, setting up timer-based interrupts, using a cross-assembler to generate programs in paper tape format, and uploading these to the kit. Note that the original KIM1 featured a 6502 microprocessor, 1K of static RAM, two 6530 RRIOT IC’s, and a 6 character hexadecimal LED diplay. Even though the Micro-KIM is a surprisingly accurate clone, it features a single 6532 RIOT, 2K EPROM for the monitor program, and 5K RAM. Please keep these differences in mind while reading the tutorial, since not all examples that work on the Micro-KIM will also work on the original KIM1. -

CP/M Is Finally Available for PET. to Run CP/M on the PET, a Z-80 Chip and in the UK

The Whole PETCatalog 23 24 The Whole PET Catalog CP/M Choices: DMS, from Compsoft. Claimed to be the most popular data management system CP/M is finally available for PET. To run CP/M on the PET, a Z-80 chip and in the UK. The new version includes a mini-word processor, which shows they've add-on memory are required. There are 2 contenders: Small Systems Engineering heard about SILICON OFFICE. and Madison Computing. Neither is sold directly by Commodore here. Users have to choose between the SUPERPET, the 8096, and the 2 CP/M's, HORNET, from Claremont Controls. A project planner and management package since they all tie up the same space on an 8032 motherboard. It's not an easy that links into SILICON OFFICE. decision, as all four products seem great! CP/M (and/or CP/M-86) will supposedly be available on the forthcoming Commodore 64, 'P', 'B'. and 'BX' models. CP/M KEYNET, a local network scheme from Commodore. Said to be able to link options include: up to 200 of most any of the Commodore machines over a distance of up to about a mile at about 250 kilobaud. OPTION #1: Small Systems Engineering advertises a price of $900 retail for a SOFTBOX that allows an 8032 to use CPM software. This unit attaches externally MW-1000, from Small Systems Engineering. A 12MB hard disk that can be to the rear of an 8032. It reportedly turns the PET into an intelligent terminal on divided into separate sections for CP/M, includes a Z80 computer, and CBM DOS, this separate computer box. -

Commodore 16 Commodore Plus/4 MSX Standard Computers

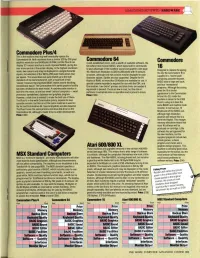

•!. Commodore Plus/4 This is the machine that may well eventually replace the Commodore 64. Both machines have a similar 320 by 200 pixel Commodore 64 graphics resolution and 64 Kbytes of RAM, but the Plus/4 can A well-established micro, with a wealth of available software, the Commodore display 121 colours and has a much improved BASIC, giving the 64 suffers from its poor BASIC, which lacks built-in commands user more control of the screen display. In the highest resolution 16 to take advantage of the excellent sound and graphics (see page Designed to replace the ageing mode, two colours only may be displayed in a single character 10). Maximum resolution is 320 by 200 pixels with 16 colours square, but selection of the 160 by 200 pixel mode allows four Vic-20, the Commodore 16 is onscreen, although only two colours may be displayed in each supplied in a 'starter pack' per square. The sound does not quite match up to the high character square. Sprites are also supported. Despite the 64 standards of the Commodore 64, with a maximum of two containing cassette recorder, Kbytes of RAM, no more than 39 Kbytes are available for use. A BASIC tutorial tape and book. 'voices': however, the improved BASIC makes sound-handling special cassette recorder is required for use with the C64, and considerably easier. The Commodore 64's sprite graphics facility and four 'recreational' Commodore 'own brand' printers and disk drives are needed if programs. Although the casing has been omitted in the new model. A machine code monitor is expansion is desired. -

An Accurate Millisecond Timer for the Commodore 64 Or 128

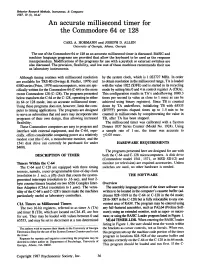

Behavior Research Methods. Instruments. &: Computers 1987. 19 (l). 36-41 An accurate millisecond timer for the Commodore 64 or 128 CARL A. HORMANN and JOSEPH D. ALLEN University of Georgia. Athens. Georgia The use of the Commodore 64 or 128 as an accurate millisecond timer is discussed. BASIC and machine language programs are provided that allow the keyboard to be used as the response manipulandum. Modifications of the programs for use with a joystick or external switches are also discussed. The precision, flexibility, and low cost of these machines recommends their use as laboratory instruments. Although timing routines with millisecond resolution by the system clock, which is 1.022727 MHz. In order are available for TRS-80 (Owings & Fiedler, 1979) and to obtain resolution in the millisecond range, TA is loaded 6500 series (Price, 1979) microcomputers, none are spe with the value 1022 ($3FE) and is started in its recycling cifically written for the Commodore 64 (C-64) or the more mode by setting bits 0 and 4 in control register A (CRA). recent Commodore 128 (C-128). The programs presented This configuration results in TA's underflowing 1000.3 below transform the C-64 or the C-128, operating ineither times per second (a value as close to 1 msec as can be its 64 or 128 mode, into an accurate millisecond timer. achieved using binary registers). Since TB is counted Using these programs does not, however, limit the com down by TA underflows, initializing TB with 65535 puter to timing applications. The programs are designed ($FFFF) permits elapsed times up to 1.5 min to be to serve as subroutines that end users may incorporate into counted in milliseconds by complementing the value in programs of their own design, thus allowing increased TB, after TA has been stopped. -

SID2SID Installation Guide

SSID2SIDID2SID Installation Guide SID2SID Introduction..................................................................................................................3 Overview........................................................................................................................4 List of Components......................................................................................................5 Assembling the components........................................................................................9 Installing the sockets..................................................................................................9 New filter capacitors for SID #1 OPTIONAL!........................................................10 Resistors...................................................................................................................11 Capacitors.................................................................................................................12 Transistor..................................................................................................................12 Filter capacitors........................................................................................................13 Audio out / Chip select.............................................................................................14 Final Checks................................................................................................................16 Installing the SID2SID...............................................................................................17 -

A Commodore 64 Retrospective Roberto Dillon

Roberto Dillon Ready A Commodore 64 Retrospective Ready Roberto Dillon Ready A Commodore 64 Retrospective 1 3 Roberto Dillon James Cook University Singapore Singapore ISBN 978-981-287-340-8 ISBN 978-981-287-341-5 (eBook) DOI 10.1007/978-981-287-341-5 Library of Congress Control Number: 2014955994 Springer Singapore Heidelberg New York Dordrecht London © Springer Science+Business Media Singapore 2015 This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use. The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. Printed on acid-free paper Springer Science+Business -

The Human Machine Art Interface: Arcade Port Aesthetics and Production Practices

The Human Machine Art Interface: Arcade Port Aesthetics and Production Practices Kieran Nolan GV2 Research Group School of Computer Science and Statistics Trinity College, Dublin +353-868227888 [email protected] ABSTRACT This research focuses on the aesthetic properties and production processes of arcade to home computer game ports during the 1980s and 1990s, in particular arcade titles originating in Japan that were licensed by UK based software houses for the 8-bit and 16-bit microcomputer market. The conversion teams worked within the unique constraints of 6 main platforms, namely the ZX Spectrum, Amstrad / Schneider CPC, Commodore 64, Atari ST, Commodore Amiga, and MS-DOS PC. In all the examples discussed, the original arcade cabinet was used as the core audiovisual and gameplay reference. As a human mediated process, the conversion of the digital material of arcade game to home computers not only bore the audiovisual constraints of the target platforms, but also the creative signatures of the conversion teams. The most successful home ports succeeded in capturing the essence of the arcade originals, while positively augmenting the gameplay, narrative, and overall aesthetic. Keywords arcade, home computer, video game, art, aesthetics, port, conversion, platform INTRODUCTION This paper concentrates on the creative processes and aesthetic properties, both audiovisual and interactive, of arcade to home computer game conversions in the 1980s and 1990s. It focuses mainly on arcade games licensed by third party developers for conversion to western 8-bit and 16-bit microcomputer platforms by UK based software houses, with findings based on first hand interaction with home arcade ports, alongside developer interviews sourced from video game magazines of the period.