12Th MRAM Global Innovation Forum

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Technology of Enterprise Solid State Drive

White Paper | April 2014 Technology of Enterprise Solid State Drive Recently, large capacity and high-performance storages are highly required in the cloud computing and data center due to rapidly increasing amount of information and number of access. When many people heavily access to internet services such as social network service (SNS) or web search engine, they will always expect an instant response from the service. In the corporate on-premise network system and financial trading system, micro seconds range of the response time makes big difference to the business outcome. As an evolution of the enterprise server and storage system, more focus is placed on speed, response time and latency to support large number of SNS user accesses and time-critical business transactions. Then Solid State Drive (SSD) plays an important role for server system to make the transactions faster. Enterprise class SSD is a storage device with NAND flash memories and required the design to store and retrieve data at very high speed under high duty operation conditions with reliable endurance performance. It will be very beneficial for system managers to deploy SSD for boosting up computing process and storage access speed. By positioning between host processor and hard disk drive (HDD) storage pools as a large cache memory, SSD increases the system transaction speed. SSD has also good points, in addition to higher performance, such as smaller footprint and lower power consumption. Toshiba has matured leading edge technologies in the SSD as the first company developing NAND flash memory. Interfaces Host Controller Interface) is popular for client application. -

2020 ANNUAL MEMBERS MEETING October 22, 2020 8AM Pacific / 11AM Eastern – Teleconference (See Next Page for Dial-In and Zoom Instructions)

2020 ANNUAL MEMBERS MEETING October 22, 2020 8AM Pacific / 11AM Eastern – Teleconference (See Next Page for Dial-in and Zoom Instructions) 1 | ©2020 Storage Networking Industry Association. All Rights Reserved. Conference Call Dial-in and Zoom Info https://www.snia.org/annualmeeting Link will start Zoom meeting – afterwards, redirects to copy of the presentation materials Teleconference/Zoom coordinates: Zoom Meeting ID: 988 4674 5668 Passcode: 102220 https://zoom.us/j/98846745668?pwd=SW5BUzAxdUJZVDFhTmhPS2VNd0FKZz09 One tap mobile +16699009128,,98846745668#,,,,,,0#,,102220# US (San Jose) +13462487799,,98846745668#,,,,,,0#,,102220# US (Houston) +16465588656,,98846745668#,,,,,,0#,,102220# US (New York) Find your local number: https://zoom.us/u/aekOw6XZjj 2 | ©2020 Storage Networking Industry Association. All Rights Reserved. Zoom Format – Attendee Guidance . Enter Name (Company) on your Zoom Login/Attendee Info . Everyone will be on Mute, except the Moderator/Speaker . You can unmute yourself if you would like to say something . Voting Member Company Primary/Alternate representatives, please identify yourself when joining . Remain on Mute when not speaking . Use the Chat Icon to text message the group or a particular person . Use Raised Hand function under “participants” icon 3 | ©2020 Storage Networking Industry Association. All Rights Reserved. 2020 Annual Members Meeting Agenda . Greetings and Roll Call – Michael Oros, Executive Director . FY2019: Annual Report published . Motion to Approve 2019 Meeting Minutes – Jim Pappas, SNIA Secretary . Fiscal Report (2019 Annual Report) – Sue Amarin, SNIA Treasurer . FY2020: SNIA update and achievements to date – Michael Oros, Executive Director . FY2021: What’s ahead for SNIA – J Metz, Ph.D, SNIA Chairman . Special Guest Speakers: EPA: Ryan Fogle; DMTF: Jeff Hilland; NVM Express: Amber Huffman . -

ISSM2020 –International Symposium on Semiconductor Manufacturing SPONSORSHIP December 15-16, 2020, Tokyo, Japan

ISSM2020 –International Symposium on Semiconductor Manufacturing SPONSORSHIP December 15-16, 2020, Tokyo, Japan Shozo Saito Chairman, ISSM2020 Organizing Committee Device & System Platform Development Center Co., Ltd. Shuichi Inoue, ATONARP INC. It is our great pleasure to announce that The 28th annual International Symposium on Semiconductor Manufacturing (ISSM) 2020 will be held on December 15-16, 2020 at KFC Hall, Ryogoku, Tokyo in cooperation with e-Manufacturing & Design Collaboration Symposium (eMDC) which is sponsored by TSIA with support from SEMI and GSA. The program will feature keynote speeches by world leading speakers, timely and highlighted topics and networking sessions focusing on equipment/materials/software/services with suppliers' exhibits. ISSM continues to contribute to the growth of the semiconductor industry through its infrastructure for networking, discussion, and information sharing among the world's professionals. We would like you to cooperate with us by supporting the ISSM 2020. Please see the benefit of ISSM2020 sponsorship. Conference Overview Date: December 15-16, 2020 Location: KFC (Kokusai Fashion Center) Hall 1-6-1 Yokoami Sumidaku, Tokyo 130-0015 Japan +81-3-5610-5810 Co-Sponsored by: IEEE Electron Devices Society Minimal Fab Semiconductor Equipment Association of Japan (SEAJ) Semiconductor Equipment and Materials International (SEMI) Taiwan Semiconductor Industry Association (TSIA) Endorsement by: The Japan Society of Applied Physics Area of Interest: Fab Management Factory Design & Automated Material -

Federal Register/Vol. 85, No. 97/Tuesday, May 19, 2020/Notices

Federal Register / Vol. 85, No. 97 / Tuesday, May 19, 2020 / Notices 29975 DEPARTMENT OF JUSTICE Register pursuant to Section 6(b) of the No other changes have been made in Act on April 12, 2019 (84 FR 14973). either the membership or planned Antitrust Division activity of the group research project. Suzanne Morris, Membership in this group research Notice Pursuant to the National Chief, Premerger and Division Statistics, project remains open, and Pistoia Cooperative Research and Production Antitrust Division. Alliance, Inc. intends to file additional Act of 1993—Silicon Integration [FR Doc. 2020–10730 Filed 5–18–20; 8:45 am] written notifications disclosing all Initiative, Inc. BILLING CODE P changes in membership. On May 28, 2009, Pistoia Alliance, Notice is hereby given that, on April Inc. filed its original notification DEPARTMENT OF JUSTICE 23, 2020, pursuant to Section 6(a) of the pursuant to Section 6(a) of the Act. The Department of Justice published a notice National Cooperative Research and Antitrust Division Production Act of 1993, 15 U.S.C. 4301 in the Federal Register pursuant to et seq. (‘‘the Act’’), Silicon Integration Notice Pursuant to the National Section 6(b) of the Act on July 15, 2009 Initiative, Inc. (‘‘Si2’’) has filed written Cooperative Research and Production (74 FR 34364). notifications simultaneously with the Act of 1993—Pistoia Alliance, Inc. The last notification was filed with the Department on February 6, 2020. A Attorney General and the Federal Trade notice was published in the Federal Commission disclosing changes in its Notice is hereby given that, on April 24, 2020, pursuant to Section 6(a) of the Register pursuant to Section 6(b) of the membership. -

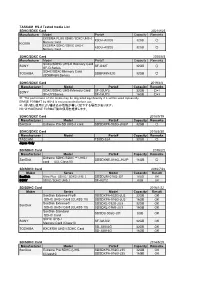

SD Supported Media 08-03-2020 Hs

TASCAM HS-2 Tested media List SDHC/SDXC Card 2021/8/25 Manufacturer Model Parts# Capacity Remarks EXCERIA PLUS SDHC/SDXC UHS-I KSDH-A032G 32GB ○ Memory Card KIOXIA EXCERIA SDHC/SDXC UHS-I KSDU-A032G 32GB ○ Memory Card SDHC/SDXC Card 2020/8/3 Manufacturer Model Parts# Capacity Remarks SDXC/SDHC UHS-II IMemory Card SONY SF-G32T 32GB ○ SF-G Series SDHC/SDXCIMemory Card TOSHIBA SDBR48N32G 32GB ○ (SDBR48N Series) SDHC/SDXC Card 2019/4/8 Manufacturer Model Parts# Capacity Remarks SDXC/SDHC UHS-IMemory Card SF-32UY3 32GB ○*1 SONY SF-UY3Series SF-16UY3 16GB ○*1 *1: The performace of the media may be degraded significantly if it will be used repeatedly. ERASE FORMAT by HS-2 is recommended before use. *1: 繰り返し使用により書き込み性能が著しく低下する場合があります。 HS-2IでのERASE FORMAT後の使用を推奨します。 SDHC/SDXC Card 2018/9/19 Manufacturer Model Parts# Capacity Remarks SanDisk Extreme Pro SD UHS-II card SDSDXPK-032G-JNJIP 32GB ○ SDHC/SDXC Card 2018/5/30 Manufacturer Model Parts# Capacity Remarks TASCAM TSQD-32A 32GB ○ Japan Only SD/SDHC Card 2018/2/2 Manufacturer Model Parts# Capacity Remarks Extreme SDHC/SDXC™ UHS-I SanDisk SDSDXNE-016G-JNJIP 16GB ○ card (U3, Class10) SD/SDHC Card 2016/7/22 Maker Series Model Capacity Result SanDisk Ultra Plus SDHC/ SDXC UHS-I SDSDUM-016G-J01 16GB OK SONY SDXC/SDHC UHS-I SF-8UY2 8GB OK SD/SDHC Card 2016/1/22 Maker Series Model Capacity Result SanDisk Extreme Pro® SDSDXPA-032G-JU3 32GB OK SDHC UHS-I Card (CLASS 10) SDSDXPA-016G-JU3 16GB OK SanDisk Extreme® SDSDXL-032G-JU3 32GB OK SanDisk SDHC UHS-I Card (CLASS 10) SDSDXL-016G-JU3 16GB OK SanDisk Standard -

Synnex Corporate 2021 Line Card

SYNNEX CORPORATE 2021 LINE CARD Corporate Headquarters Fremont, California* Sales Headquarters Greenville, South Carolina Warehouse Locations 1 Tracy, California 3 5 2 Chantilly, Virginia 6 10 3 Romeoville, Illinois 1 4 Richardson, Texas 2 5 Monroe, New Jersey 8 6 Grove City, Ohio 9 7 Miami, Florida 4 8 Southaven, Mississippi* 9 Chino, California 10 Columbus, Ohio 7 *ISO-9001:2015 Manufacturing Facilities ADVANCING IT INNOVATIONS SERVICES Map your destination to increased productivity, Sounds simple, but at • GSA Schedule cost savings and overall business success. Our SYNNEX we understand that • ECExpress Online Ordering true business growth requires • Software Licensing distribution centers are strategically located across access to meaningful, tangible the United States to provide you with product business infrastructure, tools, • Reseller Marketing Services where you need it when you need it. Each of our and resources. That’s why • Leasing distribution centers provides our customers with over the last year we’ve • Integration Services invested heavily in providing • Trade Up warehouse ratings of nearly 100% in accuracy and our partners with high-impact • A Menu of Financial Services business services, designed PPS (pick, pack and ship) performance. Couple that • SYNNEX Service Network with unsurpassed service from our infrastructure from the ground up to provide real value, and delivering on • ASCii Program support, giving you one more reason why you our commitment to provide • PRINTSolv should be doing business with SYNNEX. That’s -

RZ/V Series, Visionai ASSP RZ/V2M Datasheet

DATASHEET RZ/V Series, VisionAI_ASSP RZ/V2M R01DS0372EJ0100 Rev.1.00 Apr 28, 2021 Section 1 Overview 1.1 Features This LSI chip includes the AI dedicated accelerator (DRP-AI) and 4K-compatible image signal processor (ISP). This processor is vision-AI ASSP for real-time human and object recognition. The AI dedicated hardware IP, DRP-AI, configured with the dynamic reconfigurable processor (DRP) and AI-MAC, combines both a high-speed AI inference and low power consumption and realizes 1TOPS/W class power performance. In addition, the image signal processor (ISP) is highly robust, producing a stable image independent of the environment, allowing for a high AI recognition accuracy. With these features, this LSI realizes low power consumption, which is a critical factor for embedded devices, making heat dissipation measures easier. The result is that it is ideal for vision AI applications in a wide range of embedded markets, including surveillance security, retail, office automation (OA), industrial automation, and robotics. In addition, this LSI also features abundant high-speed communication interfaces such as USB 3.1, PCI Express®, Gigabit Ethernet, and many CPU peripheral functions, so it can also be used in a variety of applications. CPU and DDR Memory Interfaces High Speed Interfaces ● Cortex®-A53 Dual (996 MHz maximum) ● 1× Gigabit Ethernet ● 32-bit LPDDR4-3200 ● 1× USB3.1 Gen1 Host/Peripheral ® ● 1× PCIe Gen 2 (2 lanes) ● 2× SDIO 3.0 Vision and AI ● 1× NAND Flash Interface ONFI1.0 ● AI accelerator: DRP-AI (1.0 TOPS/W class) ● 1× -

Toshiba Memory Corporation to Deliver Value SAS Ssds Targeting SATA Applications

Toshiba Memory Corporation to Deliver Value SAS SSDs Targeting SATA Applications New RM5 value SAS Series Brings Improved Performance, Reliability and Capacity at a Price Point that Enables SATA Replacement in Servers Düsseldorf, Germany, 20 June 2018 - Toshiba Memory Europe (TME), European subsidiary of Toshiba Memory Corporation, unveiled today a new, game-changing category of SAS SSDs expected to replace SATA SSDs in server applications. The RM5 12Gbit/s value SAS (vSAS) series features capacity, performance, reliability, and manageability and data security advantages – at a price that obsoletes SATA SSDs. A homogeneous SAS environment has long been the gold standard for enterprise server and storage systems. With vertical integration expertise in flash technology, firmware and controller design, Toshiba Memory Corporation leveraged its leading position as the world’s leading[1] SAS SSD line optimising RM5 to close the cost gap with SATA – and usher in a new class of SSDs. SATA simply cannot compete with SAS, falling well short in terms of performance, robustness, and encryption options. “Designed with affordability and server applications in mind, the Toshiba RM5 vSAS series seeks to provide a cost effective and much higher performing solution to overcome the bottlenecks that are inherent with SATA today,” Comments Paul Rowan, General Manager for the SSD unit at Toshiba Memory Europe. Where SATA drives often use SAS expanders to scale out, the RM5 enables the use of native SAS from end-to-end, eliminating the need for protocol translation to SATA. Customers can now take full advantage of SAS’s richer feature set and realise performance throughput superiority over SATA. -

TOSHIBA Storage Utilities Version 3.11

TOSHIBA Storage Utilities Version 3.11 User’s Manual Version 1.0 Notice The information contained in this manual, including but not limited to any product specifications, is subject to change without notice. TOSHIBA CORPORATION AND ITS AFFILIATES (“TOSHIBA”) PROVIDE NO WARRANTY WITH REGARD TO THIS MANUAL OR ANY OTHER INFORMATION CONTAINED HEREIN AND HEREBY EXPRESSLY DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE WITH REGARD TO ANY OF THE FOREGOING. TOSHIBA ASSUMES NO LIABILITY FOR ANY DAMAGES INCURRED DIRECTLY OR INDIRECTLY FROM ANY TECHNICAL OR TYPOGRAPHICAL ERRORS OR OMISSIONS CONTAINED HEREIN OR FOR DISCREPANCIES BETWEEN THE PRODUCT AND THE MANUAL. IN NO EVENT SHALL TOSHIBA BE LIABLE FOR ANY INCIDENTAL, CONSEQUENTIAL, SPECIAL, OR EXEMPLARY DAMAGES, WHETHER BASED ON TORT, CONTRACT OR OTHERWISE, ARISING OUT OF OR IN CONNECTION WITH THIS MANUAL OR ANY OTHER INFORMATION CONTAINED HEREIN OR THE USE THEREOF. DISCLAIMER We assume no responsibility whatsoever for any damage or loss resulting from the use of this application. THIS APPLICATION IS PROVIDED "AS IS" WITHOUT WARRANTIES OF ANY KIND. WITHOUT LIMITING THE FOREGOING, TOSHIBA DISCLAIMS ALL WARRANTIES AND REPRESENTATIONS OF ANY KIND RELATING TO THE APPLICATION, WHETHER EXPRESS, IMPLIED, OR STATUTORY, INCLUDING WITHOUT LIMITATION THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY, OR NONINFRINGEMENT OF THIRD PARTY RIGHTS. TOSHIBA DOES NOT WARRANT THAT THE OPERATION OF THE APPLICATION WILL BE UNINTERRUPTED, ERROR-FREE, OR SECURE. ANY INSTALLATION AND/OR USE OF THE APPLICATION SHALL BE AT YOUR OWN RISK. About Trademarks Microsoft, Windows, Internet Explorer, SuperFetch are either registered trademarks or trademarks of Microsoft Corporation in the United States and other countries. -

EXCERIA Nvme™

Capacity 250GB 500GB 1TB ™ EXCERIA NVMe SSD Max Sequential Read/Write Speed1 250GB: 1,700/1,200 MB/s Upgrade Your Productivity 500GB, 1TB: 1,700/1,600 MB/s Max Random Read/Write Speed2 250GB: 200,000/290,000 IOPS 500GB, 1TB: 350,000/400,000 IOPS Features BiCS FLASH™ NVMe™ 1.3c Technology M.2 2280 Form Factor PCIe® Gen3 x4 Lane SSD Utility Management Software Upgrading from a hard drive or SATA SSD should be easy and affordable and that’s where EXCERIA SSDs come in. KIOXIA EXCERIA SSD Series is built to boost your mobile or PC experience and deliver balanced performance and value that will transform your system. Leveraging BiCS FLASH™ 3D flash memory, this new mainstream-class SSD series offers up to 1TB of capacity in a M.2 2280 form factor suitable for both desktops and notebooks. Application Peformance Maximized KIOXIA EXCERIA SSD series redefine mainstream storage for everyday users that feel held back by SATA-based hardware. Say goodbye to hard drive lag and get a computing experience worthy of your applications. Small and Compact for an Easy Upgrade Featuring a slim and light M.2 2280 form factor, the EXCERIA SSD series plugs directly into thin notebooks’ motherboard, reducing additional cable clutter for a sleeker and an easy system upgrade. NVMe™ Technology Why keep using an interface that was designed for hard drives? Utilizing the latest NVMe™ 1.3c technology, EXCERIA SSDs reduce latency in your system’s I/O path between your SSD and your CPU, resulting in smooth and responsive performance. -

IBIS Open Forum Minutes

IBIS Open Forum Minutes Meeting Date: November 13, 2020 Meeting Location: Online Virtual Summit VOTING MEMBERS AND 2020 PARTICIPANTS ANSYS Curtis Clark, Wei-hsing Huang, Marko Marin Shai Sayfan-Altman, Zilwan Mahmod, Baolong Li Usman Saeed, Miyo Kawata* Applied Simulation Technology (Fred Balistreri) Broadcom James Church, Jim Antonellis Cadence Design Systems Zhen Mu, Ambrish Varma, Jared James Kumar Keshavan, Ken Willis, Suomin Cui Takuya Moriya*, Tadaaki Yoshimura* Cisco Systems Stephen Scearce, Hong Wu, Han Gao Dassault Systemes (CST) Stefan Paret Ericsson [Anders Ekholm], Sungjoo Yu, Thomas Ahlstrom Google Zhiping Yang, Shuai Jin, Zhenxue Xu, Hanfeng Wang Songping Wu, Yimajian Yan Huawei Technologies (Hang (Paul) Yan) IBM [Michael Cohen], Greg Edlund Infineon Technologies AG (Christian Sporrer) Instituto de Telecomunicações (Abdelgader Abdalla) Intel Corporation Hsinho Wu, Michael Mirmak, Adrien Auge Fernando Mendoza, Taeyoung Kim, Wendem Beyene Oleg Mikulchenko, Nhan Phan, Ifiok Umoh Subas Bastola, Kinger Cai Keysight Technologies Radek Biernacki, Hee-Soo Lee, Todd Bermensolo Graham Riley, Pegah Alavi, Fangyi Rao Stephen Slater, Toshinori Kageura*, Hiroaki Sasaki* Satoshi Nakamizo*, Toshinobu Sanuki* Marvell Steve Parker, Johann Nittmann, Shaowu Huang Maxim Integrated Joe Engert, Charles Ganal, Dzung Tran, Yan Liang Tushar Pandey Mentor, A Siemens Business Arpad Muranyi, Raj Raghuram, Todd Westerhoff Weston Beal, Kunimoto Mashino*, Kenji Kushima* Micron Technology Randy Wolff*, Justin Butterfield, Larry Smith Vijay Kanagachalam Micron Memory Japan, G.K. Masayuki Honda*, Mikio Sugawara* MST EMC Lab Chulsoon Hwang, Anfeng Huang, Bo Pu, Jiayi He Yin Sun NXP John Burnett ©2020 IBIS Open Forum 1 SerDesDesign.com John Baprawski SiSoft (MathWorks) Mike LaBonte*, Walter Katz, Graham Kus Synopsys Ted Mido*, Andy Tai Teraspeed Labs Bob Ross* Xilinx Ravindra Gali ZTE Corporation (Shunlin Zhu) Zuken Michael Schäder, Kazunari Koga, Kensuke Yoshijima* Takayuki Shiratori* Zuken USA Lance Wang* OTHER PARTICIPANTS IN 2020 A&D Print Engineering Co. -

Floor Map(PDF)

8 7 6 5 4 3 2 1 Hall 8 Hall 7 8 7 6 5 4 3 2 1 Video Production/ International Conference Event International Hall Hall Conference Event Broadcast Equipment Hall Hall 8216 7514 Bitmedia 7206 7513 Cinfo 7519 Entaniya 7516 EXCEL Information 7514 INFOCITY GROUP 7314 7514 INFOCITY Rest Area Blackmagic Design 7517 Japan Broadcasting NEC 7521 JVCKENWOOD Mobile Charging Lounge 7520 MEDIAEDGE IKEGAMI TSUSHINKI Hands On Area 7518 Musashi SI 7515 Restaurant ▶ Venue: Event Hall 8613 Anime Tokusatsu Archive Centre NGC 7514 8610 Audio Visual Communications TECHNONET Feel Quality Sound! 7512 8611 SCENES Traffic Sim Cafe Free Trial for High Quality Audio Equipment 8609 TASCAM/TEAC The nation’s largest SR speaker demo will be held once again this year. We will bring together 15 8612 Think DESIGN Restroom famous brands with 18 products, making it the largest world-class listening experience that Inter BEE has held. This event has been gathering attention not only in Japan but also from countries overseas. There are three categories: point source, compact line array, medium and large scale line Elevator array. Please use the program below according to your interest. 8313 8215 7413 7313 7205 Hall ▶ Venue: Exhibition Hall 1 Sanshin Electronics/ 7 6 Totsu Sakura Eiki Grass Valley Leader Electronic International LiveU Global Scale! Largest ever in Inter BEE History, 8503 18 Products from 15 Brands! X-Headphone and X-Microphone was created so people could openly experience professional grade audio equipment. We will be holding this popular event with well-known brands showcasing their high quality devices.